# SGM40657/SGM40658 High-Current Over-Voltage Protector

### **GENERAL DESCRIPTION**

The SGM40657/8 over-voltage protection devices feature a low  $20m\Omega$  (TYP)  $R_{ON}$  internal FET and protect low-voltage systems against voltage faults up to +28V<sub>DC</sub>. An internal clamp also protects the devices from surges up to +120V. When the input voltage exceeds the over-voltage threshold, the internal FET is turned off to prevent damage to the protected downstream components.

The over-voltage protection threshold can be adjusted with optional external resistors to any voltage between 4V and 20V. If the OVLO input is below the external OVLO select voltage, the SGM40657/8 automatically choose the internal trip thresholds. The internal over-voltage thresholds ( $V_{IN_OVLO}$ ) are preset to be 6.82V/5.95V typical (SGM40657/8). The devices feature an open-drain  $\overline{ACOK}$  output indicating a stable supply between minimum supply voltage and  $V_{OVLO}$ . The SGM40657/8 are also protected against over-current events by an internal thermal shutdown.

The SGM40657/8 are available in Green 12-Ball CSP package and operate over an ambient temperature range of -40°C to +85°C.

## **FEATURES**

- Protect High-Power Portable Devices

- Wide Operating Input Voltage Protection from 2.5V to 28V

- Integrated 20mΩ (TYP) N-Channel MOSFET Switch

- Flexible Over-Voltage Protection Design

- Adjustable Over-Voltage Protection Trip Level

- Wide Adjustable OVLO Threshold Range from 4V to 20V

- Internal Preset OVLO Thresholds:

6.82V (SGM40657)

5.95V (SGM40658)

- Additional Protection Features Increase System Reliability

- Surge Immunity up to +120V

- Soft-Start to Minimize In-Rush Current

- Internal 15ms Startup Debounce

- Thermal Shutdown Protection

- Enable Function

- -40°C to +85°C Operating Temperature Range

- Available in Green WLCSP-1.31×1.84-12B Package

# **APPLICATIONS**

Smart Phones Tablet PCs Mobile Internet Devices

### **PACKAGE/ORDERING INFORMATION**

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM40657 | WLCSP-1.31×1.84-12B    | -40°C to +85°C                    | SGM40657YG/TR      | XXXXX<br>GM3YG     | Tape and Reel, 3000 |

| SGM40658 | WLCSP-1.31×1.84-12B    | -40°C to +85°C                    | SGM40658YG/TR      | XXXXX<br>GM4YG     | Tape and Reel, 3000 |

NOTE: XXXXX = Date Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN (with respect to GND)                  | 0.3V to 28V <sup>(1)</sup>    |

|-------------------------------------------|-------------------------------|

| IN (with respect to GND) +120V, 1.2/50    |                               |

| OUT (with respect to GND)0                | .3V to V <sub>IN</sub> + 0.3V |

| OVLO                                      | 0.3V to 26.4V                 |

| ACOK, EN (with respect to GND)            | 0.3V to 6V                    |

| Continuous IN, OUT Current <sup>(4)</sup> | 6A                            |

| Peak IN, OUT Current (10ms)               | 8A                            |

| Junction Temperature                      | +150°C                        |

| Storage Temperature Range                 | 65°C to +150°C                |

| Lead Temperature (Soldering 10 sec)       | +260°C                        |

| ESD Susceptibility                        |                               |

| HBM                                       | 7kV                           |

| MM                                        | 400V                          |

| CDM                                       | 1kV                           |

| Air Gap Discharge on IN Pin (IEC61000-4-2 | )20kV                         |

| Contact Discharge on IN Pin (IEC61000-4-2 | 2) 12kV                       |

### **OVERSTRESS CAUTION**

Stresses beyond those listed may cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational section of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time.

#### **RECOMMENDED OPERATING CONDITIONS**

| Supply Voltage Range        | 2.5V to 28V <sup>(5)</sup> |

|-----------------------------|----------------------------|

| Operating Temperature Range | -40°C to +85°C             |

#### NOTES:

1. Non-frequent repeat peak voltage during input surge transient and ESD transient is not subject to this rating value, which may go higher than 35V during the surge test.

- 2. Surge test in compliance with IEC61000-4-5 specification.

- 3. Survives burst pulse up to +120V with 2 $\Omega$  series resistance.

4. Continuous current limit may vary with the circuit board thermal dissipation condition.

5. If protection discharging triggered, the discharging keeps until the supply falls below the hysteresis range. Continuously force driving during discharging with a voltage in the hysteresis range would cause overstress or even damage the device. Supply voltage within the hysteresis range is not recommended. A  $1k\Omega$  resistor should be inserted in supply path for clamp voltage evaluation to avoid overstress damage by unintended triggering.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

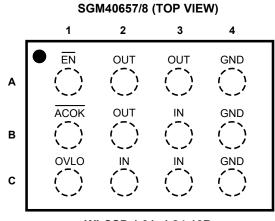

# **PIN CONFIGURATION**

WLCSP-1.31×1.84-12B

### **PIN DESCRIPTION**

| PIN        | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                    |

|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1         | ĒN   | Enable Control. When $\overline{EN}$ = "Low", chip is enabled; when $\overline{EN}$ = "High", chip is in disable status.                                                                                                                                                                                                                    |

| A4, B4, C4 | GND  | Ground. Connect GND pins together for proper operation.                                                                                                                                                                                                                                                                                     |

| A2, A3, B2 | OUT  | Output Voltage. Output of internal switch. Connect OUT pins together for proper operation.                                                                                                                                                                                                                                                  |

| B1         | ACOK | Open-Drain Flag Output. $\overline{\text{ACOK}}$ is driven low after input voltage is stable between minimum V <sub>IN</sub> and V <sub>OVLO</sub> after debounce. Connect a pull-up resistor from $\overline{\text{ACOK}}$ to the logic I/O voltage of the host system. $\overline{\text{ACOK}}$ is high impedance after thermal shutdown. |

| B3, C2, C3 | IN   | Input Voltage. Bypass IN with a $0.1\mu$ F ceramic capacitor as close as possible to the device. Connect IN pins together for proper operation.                                                                                                                                                                                             |

| C1         | OVLO | External OVLO Adjustment. Connect OVLO to GND when using the internal threshold. Connect a resistor-divider to OVLO to set a different OVLO threshold; this external resistor-divider is completely independent of the internal threshold.                                                                                                  |

# **ELECTRICAL CHARACTERISTICS**

(V<sub>IN</sub> = 2.5V to 28V,  $\overline{EN}$  = 0V, C<sub>IN</sub> = 0.1µF, T<sub>A</sub> = -40°C to +85°C, typical values are at V<sub>IN</sub> = 5V, I<sub>IN</sub> ≤ 3A, T<sub>A</sub> = +25°C, unless otherwise noted.)

| otherwise noted.) PARAMETER       | SYMBOL                   | CONDITIONS                                                                                                                                                                                                                                                                                               |                           | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|-------|-------|-------|

| Input Voltage Range               | V <sub>IN</sub>          |                                                                                                                                                                                                                                                                                                          |                           | 2.5   |       | 28    | V     |

| Input Clamp Triggering Voltage    | VIN CLAMP                | $I_{IN} = 10$ mA limited, $T_A = +25$ °C                                                                                                                                                                                                                                                                 |                           |       | 28.8  |       | V     |

| Input Clamp Hysteresis            | -<br>V <sub>HYS</sub>    |                                                                                                                                                                                                                                                                                                          |                           |       | 0.75  |       | V     |

| Input Supply Current              | I <sub>IN</sub>          | V <sub>IN</sub> = 5V                                                                                                                                                                                                                                                                                     |                           |       | 95    | 155   | μA    |

| OVLO Supply Current               | I <sub>IN_Q</sub>        | V <sub>OVLO</sub> = 3V, V <sub>IN</sub> = 5                                                                                                                                                                                                                                                              | 5V, V <sub>OUT</sub> = 0V |       | 95    | 155   | μA    |

| Shutdown Current                  | I <sub>Q_OFF</sub>       | $V_{IN} = 5V, \overline{EN} = 2$                                                                                                                                                                                                                                                                         | V                         |       |       | 2     | μA    |

|                                   |                          | V <sub>IN</sub> rising                                                                                                                                                                                                                                                                                   | SGM40657                  | 6.61  | 6.82  | 7.06  |       |

|                                   |                          |                                                                                                                                                                                                                                                                                                          | SGM40658                  | 5.73  | 5.95  | 6.18  |       |

| Internal Over-Voltage Trip Level  | V <sub>IN_OVLO</sub>     |                                                                                                                                                                                                                                                                                                          | SGM40657                  | 6.07  | 6.53  |       | V     |

|                                   |                          | V <sub>IN</sub> falling                                                                                                                                                                                                                                                                                  | SGM40658                  | 5.15  | 5.63  |       |       |

| V <sub>BG</sub> Reference         | V <sub>BG</sub>          |                                                                                                                                                                                                                                                                                                          |                           | 1.180 | 1.216 | 1.255 | V     |

| Adjustable OVLO Threshold Range   |                          |                                                                                                                                                                                                                                                                                                          |                           | 4     |       | 20    | V     |

| External OVLO Select Threshold    | V <sub>OVLO_SELECT</sub> |                                                                                                                                                                                                                                                                                                          |                           | 0.23  | 0.26  | 0.30  | V     |

| Switch On-Resistance              | R <sub>on</sub>          | V <sub>IN</sub> = 5V, I <sub>OUT</sub> = 0.5A, T <sub>A</sub> = +25°C                                                                                                                                                                                                                                    |                           |       | 20    | 35    | mΩ    |

| OUT Load Capacitance              | C <sub>OUT</sub>         | V <sub>IN</sub> = 5V                                                                                                                                                                                                                                                                                     |                           |       |       | 1000  | μF    |

| OVLO Input Leakage Current        | I <sub>OVLO</sub>        | V <sub>OVLO</sub> = 1.3V                                                                                                                                                                                                                                                                                 |                           | -100  |       | 100   | nA    |

| IN Leakage Voltage by OVLO        | V <sub>IN_LEAK</sub>     | $\label{eq:V_OVLO} \begin{split} V_{\text{OVLO}} &= 20 V,  V_{\text{IN}} = \text{unconnected}, \\ R_{\text{OVLO}} &= 1 M \Omega \end{split}$                                                                                                                                                             |                           |       |       | 0.2   | V     |

| Thermal Shutdown                  |                          |                                                                                                                                                                                                                                                                                                          |                           |       | 150   |       | °C    |

| Thermal Shutdown Hysteresis       |                          |                                                                                                                                                                                                                                                                                                          |                           |       | 30    |       | °C    |

| DIGITAL SIGNAL ( ACOK )           |                          |                                                                                                                                                                                                                                                                                                          |                           |       |       |       |       |

| ACOK Output Low Voltage           | V <sub>OL</sub>          | $V_{I/O}$ = 3.3V, $I_{SINK}$ = 1mA,<br>See Figure 1                                                                                                                                                                                                                                                      |                           |       | 0.26  | 0.32  | V     |

| ACOK Leakage Current              | I <sub>ACOK_LEAK</sub>   | $V_{I/O}$ = 3.3V, $\overline{ACOK}$ deasserted,<br>See Figure 1                                                                                                                                                                                                                                          |                           |       |       | 1     | μA    |

| TIMING CHARACTERISTICS            |                          |                                                                                                                                                                                                                                                                                                          |                           |       |       |       |       |

| Debounce Time                     | t <sub>DEB</sub>         | Time from V <sub>IN</sub> > 2.5V to the time V <sub>OUT</sub> starts rising                                                                                                                                                                                                                              |                           |       | 15    |       | ms    |

| Soft-Start Time                   | t <sub>ss</sub>          | Time from $V_{IN}$ > 2.5V to soft-start off                                                                                                                                                                                                                                                              |                           |       | 30    |       | ms    |

| Switch Turn-On Time               | t <sub>on</sub>          | $\label{eq:VIN} \begin{array}{l} V_{\text{IN}} = 5V, \; R_{\text{L}} = 100\Omega, \; C_{\text{LOAD}} = 100 \mu\text{F}, \\ V_{\text{OUT}} \; \text{from} \; 10\%, \; V_{\text{IN}} \; \text{to} \; 90\% \; V_{\text{IN}} \end{array}$                                                                    |                           |       | 1.5   |       | ms    |

| Switch Turn-Off Time              | t <sub>OFF</sub>         | $ \begin{array}{l} V_{\text{IN}} > V_{\text{IN} \ \text{OVLO}} \ \text{to} \ V_{\text{OUT}} = 80\% \ \text{of} \ V_{\text{IN}}, \\ R_{\text{L}} = 100\Omega, \ \text{with} \ 20\% \ \text{over} \ \text{drive}, \ \text{for} \\ \text{the case of using the internal} \\ \text{threshold.} \end{array} $ |                           |       | 50    |       | ns    |

| Switch Turn-Off Propagation Delay | t <sub>DELAY</sub>       | OVLO > V <sub>BG</sub> with<br>output falling 10%<br>case of using exte                                                                                                                                                                                                                                  |                           | 80    |       | ns    |       |

| EN LOGIC LEVELS                   |                          |                                                                                                                                                                                                                                                                                                          |                           |       |       |       |       |

| Logic LOW Input Voltage           | V <sub>IL</sub>          |                                                                                                                                                                                                                                                                                                          |                           |       | 0.4   | V     |       |

| Logic HIGH Input Voltage          | V <sub>IH</sub>          |                                                                                                                                                                                                                                                                                                          |                           | 1.6   |       |       | V     |

| EN Leakage Current                | IEN_LEAK                 | V <sub>IN</sub> = 5V                                                                                                                                                                                                                                                                                     |                           |       |       | 1     | μA    |

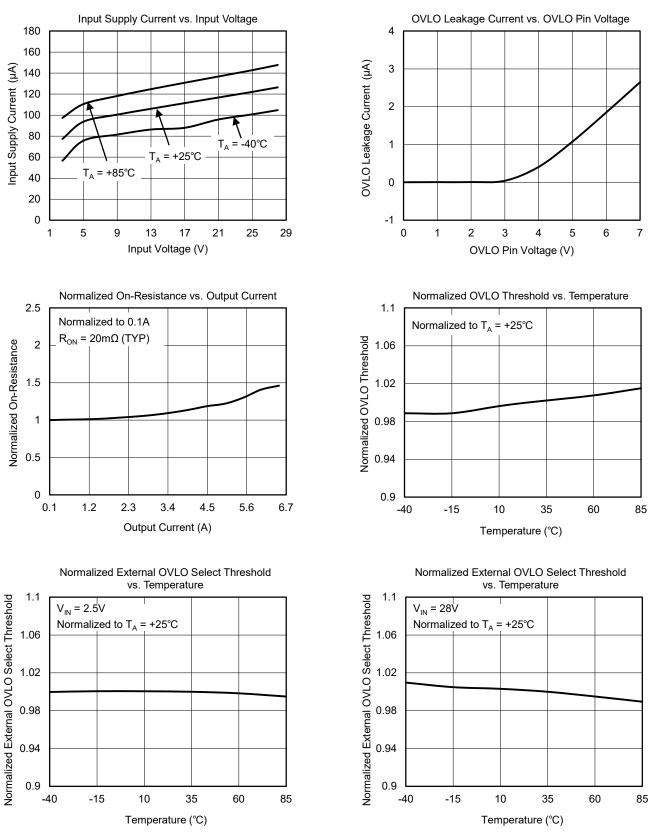

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{\text{IN}} = 5V, \ \overline{\text{EN}} = 0V, C_{\text{IN}} = 0.1 \mu\text{F}, C_{\text{OUT}} = 1 \mu\text{F}, T_{\text{A}} = +25^{\circ}\text{C}, \text{ unless otherwise noted}.$

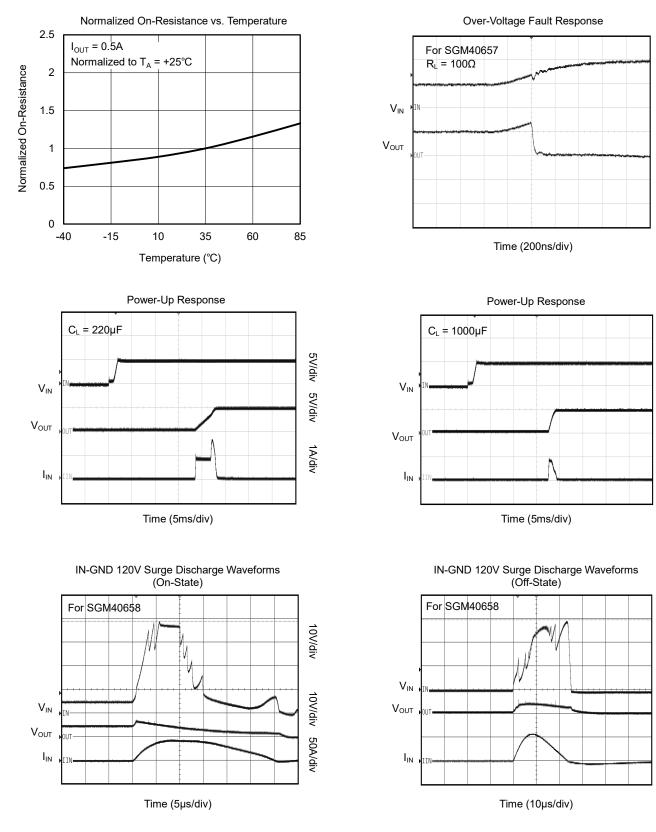

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{\text{IN}} = 5V, \ \overline{\text{EN}} = 0V, C_{\text{IN}} = 0.1 \mu\text{F}, C_{\text{OUT}} = 1 \mu\text{F}, T_{\text{A}} = +25^{\circ}\text{C}, \text{ unless otherwise noted}.$

SG Micro Corp

5V/div

5V/div

5V/div

5V/div

1A/div

10V/div

2V/div 50A/div

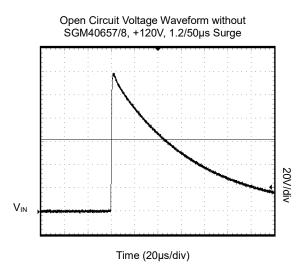

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{\text{IN}} = 5V, \ \overline{\text{EN}} = 0V, C_{\text{IN}} = 0.1 \mu\text{F}, C_{\text{OUT}} = 1 \mu\text{F}, T_{\text{A}} = +25^{\circ}\text{C}, \text{ unless otherwise noted}.$

## SGM40657/SGM40658

### **TYPICAL APPLICATION**

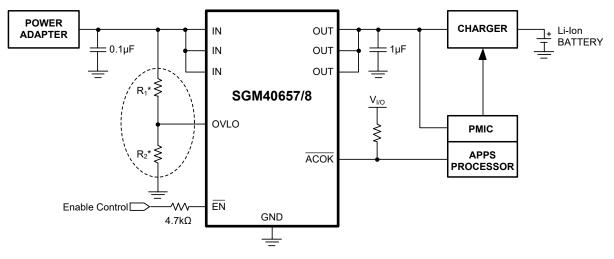

\*  $R_1$  and  $R_2$  are only required for adjustable OVLO; otherwise, connect OVLO to GND.

Figure 1. Typical Application Circuit

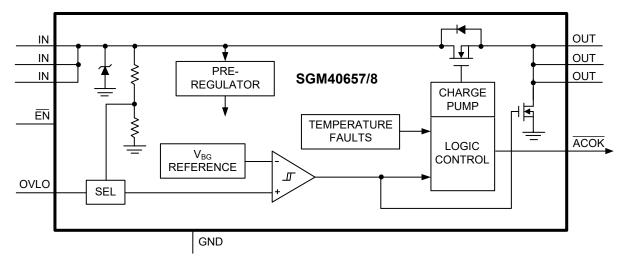

# FUNCTIONAL BLOCK DIAGRAM

Figure 2. Block Diagram

### SGM40657/SGM40658

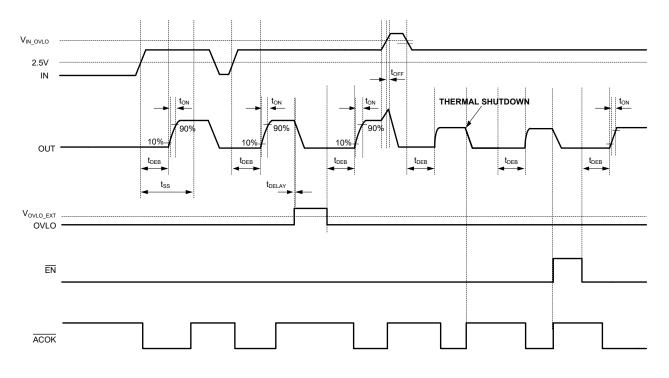

### TIMING DIAGRAM

NOTE: Waveforms are not to scale.

Figure 3. Timing Diagram

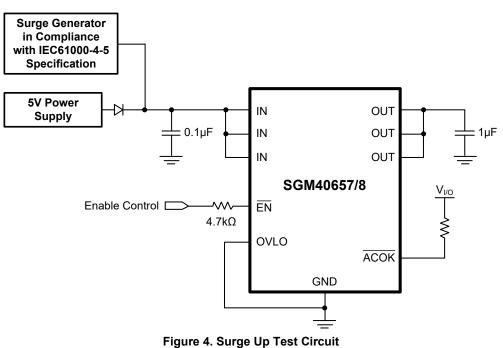

# SURGE UP TEST CIRCUIT

# **DETAILED DESCRIPTION**

The SGM40657/8 over-voltage protection devices feature a low on-resistance ( $R_{ON}$ ) internal FET and protect low-voltage systems against voltage faults up to +28V<sub>DC</sub>. An internal clamp also protects the devices from surges up to +120V. Surge up tests are operated according to the test circuit in Figure 4. If the input voltage exceeds the over-voltage threshold, the internal FET is turned off to prevent damage to the protected components. A 15ms (TYP) debounce time built into the device prevents false turn-on of the internal FET during startup.

#### **Device Operation**

The devices contain timing logic that controls the turn-on of the internal FET. The internal charge pump is enabled when  $V_{IN} < V_{IN_OVLO}$ , if internal trip thresholds are used or when  $V_{OVLO} < V_{OVLO_EXT}$  if external trip thresholds are used. The charge-pump after a 15ms (TYP) debounce delay, turns the internal FET on (see Figure 2). After the debounce time, soft-start limits the FET inrush current for 15ms (TYP). At any time, if  $V_{IN}$  rises above  $V_{OVLO}$  THRESH, OUT is disconnected from IN.

### **Enable Function**

The IC has an enable pin which is used to enable or disable the device. Connect the  $\overline{EN}$  pin high to turn off the internal pass FET. Connect the  $\overline{EN}$  pin low to turn on the internal pass FET and enter the start-up routine.

### **Internal Switch**

The SGM40657/8 incorporate an internal FET with a 20m $\Omega$  (TYP)  $R_{\text{ON}}.$  The FET is internally driven by a charge pump that generates a necessary gate voltage above IN.

### **Over-Voltage Lockout (OVLO)**

The SGM40657/8 have 6.82V/5.95V (TYP) over-voltage threshold (OVLO) respectively.

### **Thermal Shutdown Protection**

The SGM40657/8 feature thermal shutdown circuitry. The internal FET turns off when the junction temperature exceeds  $+150^{\circ}C$  (TYP). The device exits thermal shutdown after the junction temperature cools by  $30^{\circ}C$  (TYP).

### **ACOK** Output

An open-drain  $\overline{\text{ACOK}}$  output gives the SGM40657/8 the ability to communicate a stable power source to the host system.  $\overline{\text{ACOK}}$  is driven low after input voltage is stable between minimum V<sub>IN</sub> and V<sub>OVLO</sub> after debounce. Connect a pull-up resistor from  $\overline{\text{ACOK}}$  to the logic I/O voltage of the host system.  $\overline{\text{ACOK}}$  is high impedance after thermal shutdown.

### **USB OTG Support**

When used in an OTG application the SGM40657/8 can provide power from OUT to IN. Initially, the OTG voltage applied at OUT will forward-bias the power switch bulk diode and present a voltage drop of approximately 0.7V between OUT and IN. Once the voltage at IN exceeds the minimum input voltage of 2.5V and the debounce time has elapsed, the main power switch will turn fully on, significantly reducing the voltage drop from OUT to IN. In this mode, the part is able to supply a continuous current up to 3.5A to the OTG load.

## **APPLICATION INFORMATION**

#### **Bypass Capacitor**

For most applications, bypass IN to GND with a  $0.1\mu$ F ceramic capacitor as close as possible to the device. If the power source has significant inductance due to long lead length, the device clamps the overshoot due to LC tank circuit.

#### **Output Capacitor**

The slow turn-on time provides a soft-start function that allows the SGM40657/8 to charge an output capacitor up to  $1000\mu F$  without turning off due to an over-current condition.

#### **Enhancing Surge Absorbability**

When the input voltage ramps higher than the V<sub>IN\_CLAMP</sub>, it triggers an active path in the device to discharge the input quickly until the input voltage falls V<sub>HYS</sub> below the V<sub>IN\_CLAMP</sub>. Input rising and discharging may repeat until the surge source energy is discharged. A voltage pulse with saw shape top is clamped between the V<sub>IN\_CLAMP</sub> and the active path's resumable breaking voltage, which protects components which are connected to the device's input or output.

As the active path tries to pull in more energy upon triggering, only those absorption components with similar triggering voltage and similar residual voltage could share their capability for enhancing surge absorption. Both the trigger voltage and the residual voltage should be evaluated for selection matched companion absorption components. As a rule of thumb, a TVS with triggering voltage lower than the V<sub>IN\_CLAMP</sub> is recommended.

#### **External OVLO Adjustment Functionality**

The device detects voltage at the OVLO pin to check if an external divider exists. If OVLO is connected to ground, the internally set OVLO value will be applied.

If an external resistor-divider is connected to OVLO and V<sub>OVLO</sub> exceeds the OVLO select voltage, V<sub>OVLO\_SELECT</sub>, then this external resistor divider determines the V<sub>IN\_OVLO\_EXT</sub>. R<sub>1</sub> = 1M $\Omega$  is a good starting value for minimum current consumption. Since V<sub>IN\_OVLO\_EXT</sub>, V<sub>BG</sub>, and R<sub>1</sub> are known, R<sub>2</sub> can be calculated from the following formula:

$$V_{\text{IN}_{\text{OVLO}_{\text{EXT}}}} = V_{\text{BG}} \times \left[1 + \frac{R_1}{R_2}\right]$$

This external resistor-divider is completely independent from the internal resistor-divider.

### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Original (DECEMBER 2017) to REV.A

Changed from product preview to production data.....Al

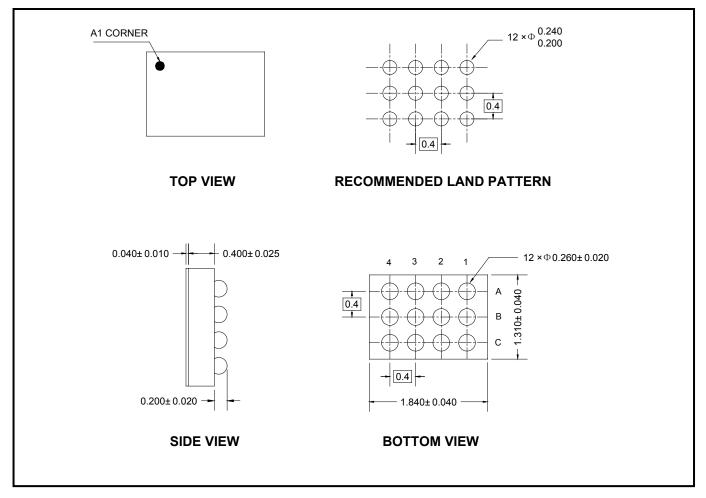

# PACKAGE OUTLINE DIMENSIONS

# WLCSP-1.31×1.84-12B

NOTE: All linear dimensions are in millimeters.

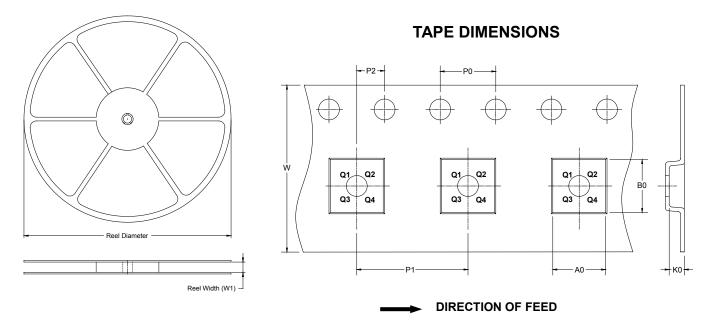

# TAPE AND REEL INFORMATION

### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type        | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| WLCSP-1.31×1.84-12B | 7″               | 9.2                      | 1.40       | 2.00       | 0.80       | 4.0        | 4.0        | 2.0        | 8.0       | Q2               |

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |       |

|-------------|----------------|---------------|----------------|--------------|-------|

| 7" (Option) | 368            | 227           | 224            | 8            |       |

| 7"          | 442            | 410           | 224            | 18           | 00002 |