## SGM51610C Ultra-Small, Low-Power, 16-Bit SGMICRO Analog-to-Digital Converter with Internal Reference

#### GENERAL DESCRIPTION

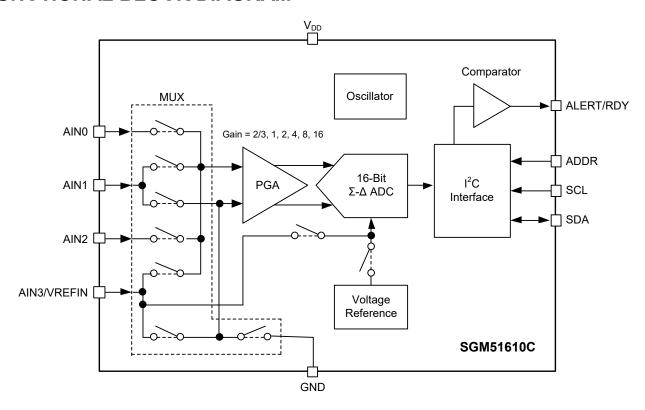

The SGM51610C is a low-power, 16-bit, precision, sigma-delta ( $\Sigma$ - $\Delta$ ) analog-to-digital converter (ADC). It operates from a 2V to 5.5V supply.

The SGM51610C contains a very low-drift on-chip reference and oscillator. It has an I<sup>2</sup>C-compatible interface, and it can select four I<sup>2</sup>C slave addresses. The data rate of the filter is up to 960SPS. The SGM51610C has an on-chip PGA, which can provide input ranges to as low as ±256mV from the power supply.

The input multiplexer supports 4 single-ended inputs or 2 differential inputs configuration.

The SGM51610C is available in Green MSOP-10 and TDFN-3×3-10L packages. It operates over an ambient temperature range of -40°C to +125°C.

#### **FEATURES**

• Single-Supply Voltage Range: 2V to 5.5V

I<sup>2</sup>C Bus Voltage Range: 2V to 5.5V

• Low Quiescent Current:

◆ Continuous Mode: 310µA (TYP)

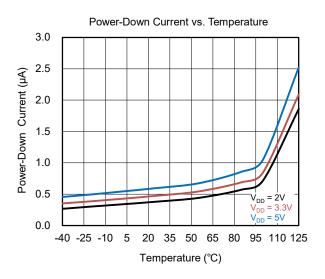

◆ Power-Down Mode: 0.65µA (TYP)

• Selectable Data Rates: 5SPS to 960SPS

• Single-Cycle Settling

• 50/60Hz Line Rejection

• Input Multiplexer

4 Single-Ended Inputs or 2 Differential Inputs

Internal Programmable Gain Amplifier (PGA)

**Internal Voltage Reference and Oscillator**

**Selectable Digital Comparator**

• I<sup>2</sup>C-Compatible Serial Interface

Available in Green MSOP-10 and TDFN-3×3-10L **Packages**

#### APPLICATIONS

Portable Devices Process Control **Battery Monitoring System** Temperature Measurement

#### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER                      | PACKAGE<br>MARKING       | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|-----------------------------------------|--------------------------|---------------------|

| SGM51610C | MSOP-10                | 1000 / 10-00                      | SGM51610CXMS10G/TR                      | SGM0KS<br>XMS10<br>XXXXX | Tape and Reel, 4000 |

|           | WISOF-10               | -40°C to +125°C                   | SGM51610CXMS10SG/TR                     | SGM0KS<br>XMS10<br>XXXXX | Tape and Reel, 500  |

|           | TDFN-3×3-10L           | -40°C to +125°C                   | SGM51610CXTD10G/TR SGM<br>0KRD<br>XXXXX | _                        | Tape and Reel, 4000 |

|           | 10FN-3*3-10L           | -40 0 10 +125 0                   | SGM51610CXTD10SG/TR                     | SGM<br>0KRD<br>XXXXX     | Tape and Reel, 500  |

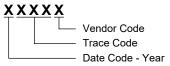

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range (with Respect to GND) |                |

|-------------------------------------|----------------|

| V <sub>DD</sub>                     | 0.3V to 5.5V   |

| Analog Input Voltage                | 0.3V to 5.5V   |

| SDA, SCL, ADDR, ALERT/RDY Voltage   | 0.3V to 5.5V   |

| Input Current (Momentary)           | 100mA          |

| Input Current (Continuous)          | 10mA           |

| Package Thermal Resistance          |                |

| MSOP-10, θ <sub>JA</sub>            | 139.4°C/W      |

| MSOP-10, θ <sub>JB</sub>            | 90.6°C/W       |

| MSOP-10, θ <sub>JC</sub>            | 47.7°C/W       |

| TDFN-3×3-10L, θ <sub>JA</sub>       | 39.5°C/W       |

| TDFN-3×3-10L, θ <sub>JB</sub>       | 16.8°C/W       |

| TDFN-3×3-10L, $\theta_{JC (TOP)}$   | 46.2°C/W       |

| TDFN-3×3-10L, $\theta_{JC (BOT)}$   | 4.7°C/W        |

| Junction Temperature                | +150°C         |

| Storage Temperature Range           | 65°C to +150°C |

| Lead Temperature (Soldering, 10s)   | +260°C         |

| ESD Susceptibility (1) (2)          |                |

| HBM                                 | ±4000V         |

| CDM                                 | ±1000V         |

|                                     |                |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

Operating Temperature Range.....-40°C to +125°C

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

## **PIN CONFIGURATIONS**

#### PIN DESCRIPTION

|         | PIN NAME TYPE |             | TVDE | FUNCTION                                                                                                  |  |  |

|---------|---------------|-------------|------|-----------------------------------------------------------------------------------------------------------|--|--|

| MSOP-10 | TDFN-3×3-10L  | NAME        | ITPE | FUNCTION                                                                                                  |  |  |

| 1       | 1             | ADDR        | DI   | I <sup>2</sup> C Address Selection Pin.                                                                   |  |  |

| 2       | 2             | ALERT/RDY   | DO   | Digital Comparator Output/Conversion Ready Pin.                                                           |  |  |

| 3       | 3             | GND         | G    | Ground.                                                                                                   |  |  |

| 4       | 4             | AIN0        | Al   | Positive Input of Differential Channel 1 or Input of Single-Ended Channel 1.                              |  |  |

| 5       | 5             | AIN1        | Al   | Negative Input of Differential Channel 1 or Input of Single-Ended Channel 2.                              |  |  |

| 6       | 6             | AIN2        | Al   | Positive Input of Differential Channel 2 or Input of Single-Ended Channel 3.                              |  |  |

| 7       | 7             | AIN3/VREFIN | Al   | Negative Input of Differential Channel 2 or Input of Single-Ended Channel 4, or External Reference Input. |  |  |

| 8       | 8             | $V_{DD}$    | Р    | Power Supply Pin. It can be operated from 2V to 5.5V.                                                     |  |  |

| 9       | 9             | SDA         | DIO  | Serial Data Pin.                                                                                          |  |  |

| 10      | 10            | SCL         | DI   | Serial Clock Input Pin.                                                                                   |  |  |

| _       | Exposed Pad   | EP          | _    | Exposed pad should be soldered to PCB board and connected to GND.                                         |  |  |

NOTE: AI = analog input, DI = digital input, DO = digital output, DIO = digital input and output, P = power, G = ground.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 3.3V, DR = 5SPS, full-scale input voltage range (FSR) = \pm 2.048V, internal reference, maximum and minimum specifications apply from <math>T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , typical values are measured at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                     | SYMBOL         | CONDITIONS                                                                     |                        | MIN  | TYP               | MAX      | UNITS  |

|-------------------------------|----------------|--------------------------------------------------------------------------------|------------------------|------|-------------------|----------|--------|

| Analog Input                  | •              |                                                                                |                        |      |                   |          | •      |

| Full-Scale Input Voltage (1)  |                | $V_{IN} = AIN_P - AIN_N$                                                       |                        |      | ±4.096/PGA        |          | V      |

| Analog Input Voltage          |                | AIN <sub>P</sub> or AIN <sub>N</sub> to GND                                    |                        | -0.1 |                   | $V_{DD}$ | V      |

| Differential Input Impedance  |                |                                                                                |                        |      | See Table 1       |          |        |

| System Performance            |                |                                                                                |                        |      |                   |          |        |

| Resolution                    |                | No missing codes                                                               |                        | 16   |                   |          | Bits   |

| Data Rate                     | DR             |                                                                                |                        |      | See Table 5       |          | SPS    |

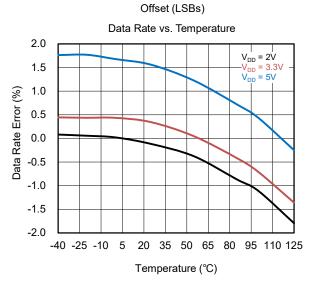

| Data Rate Variation           |                | All data rates                                                                 |                        | -3.5 |                   | 3.5      | %      |

| Output Noise                  |                |                                                                                |                        | See  | e Table 6 and Tab | ole 7    |        |

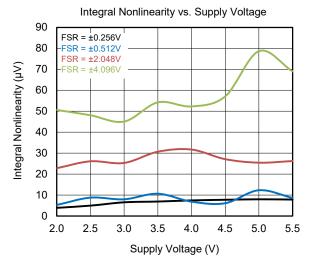

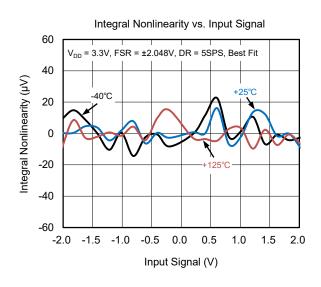

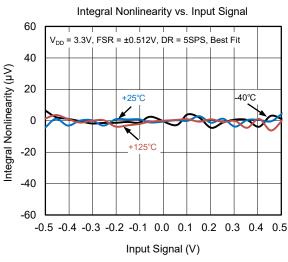

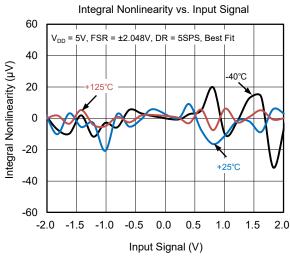

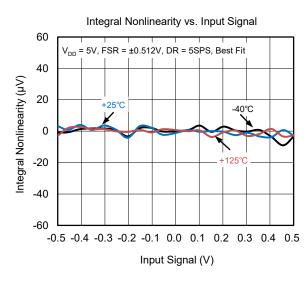

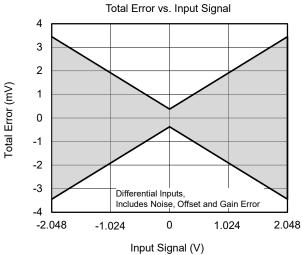

| Integral Nonlinearity         | INL            | DR = 5SPS, FSR = ±                                                             | ±2.048V <sup>(2)</sup> |      | 1                 | 4        | LSB    |

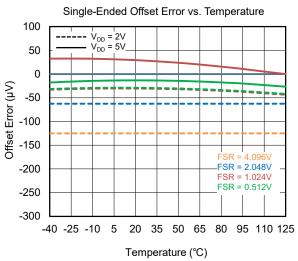

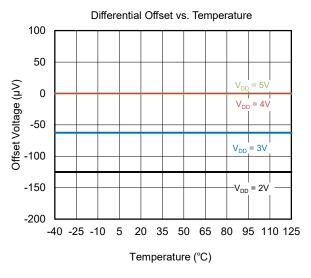

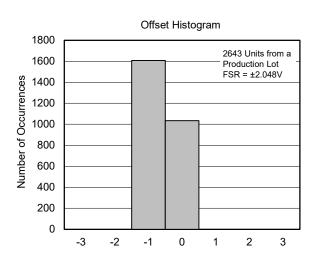

| Offset Error                  | _              | ECD - +2 040\/                                                                 | Differential inputs    | -6   | -1                | 6        | LCD    |

|                               | Eo             | FSR = ±2.048V                                                                  | Single-ended inputs    | -7   | -1                | 7        | LSB    |

| Offset Drift                  |                | FSR = ±2.048V                                                                  | FSR = ±2.048V          |      | 0.005             | 0.025    | LSB/°C |

| Offset Power Supply Rejection |                | FSR = ±2.048V                                                                  |                        |      | 0.6               |          | LSB/V  |

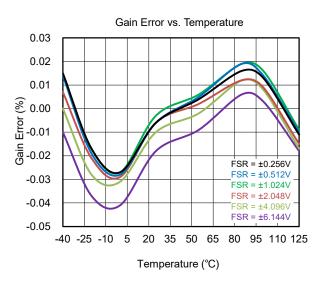

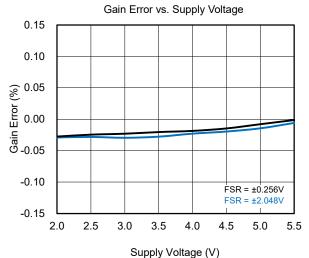

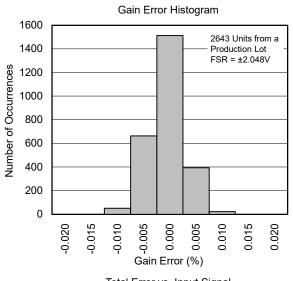

| Gain Error (3)                | E <sub>G</sub> | FSR = ±2.048V at +2                                                            | 25°C                   |      | 0.01              | 0.15     | %      |

|                               |                | FSR = ±0.256V<br>FSR = ±2.048V                                                 |                        |      | 6                 |          | ppm/°C |

| Gain Drift (3) (4)            |                |                                                                                |                        |      | 6                 | 15       |        |

|                               |                | FSR = ±6.144V <sup>(1)</sup>                                                   |                        |      | 6                 |          | 1      |

| Gain Power Supply Rejection   |                |                                                                                |                        |      | 80                |          | ppm/V  |

| PGA Gain Match (3)            |                | Match between any                                                              | two PGA gains          |      | 0.01              | 0.1      | %      |

| Gain Match                    |                | Match between any                                                              | two inputs             |      | 0.01              | 0.08     | %      |

| Offset Match                  |                | Match between any                                                              | two gains              |      | 2                 | 9        | LSB    |

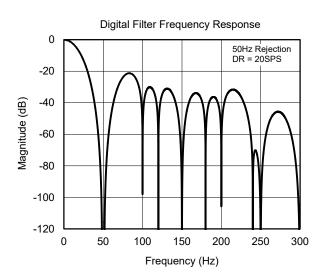

| 50/60Hz Rejection             |                | FSR = ±2.048V                                                                  | FSR = ±2.048V          |      | 100               |          | dB     |

| Channel-to-Channel Crosstalk  |                | At DC and FSR = ±2.048V, differential or single-ended inputs adjacent channels |                        |      | 110               |          | dB     |

|                               |                | At DC and FSR = ±0                                                             | .256V                  |      | 105               |          |        |

| Common Mode Rejection Ratio   | CMRR           | At DC and FSR = ±2                                                             | .048V                  |      | 100               |          | dB     |

|                               |                | At DC and FSR = ±6                                                             | .144V <sup>(1)</sup>   |      | 90                |          |        |

#### NOTES:

- 1. The full-scale range of the ADC scaling. In any event, it should not exceed  $V_{DD}$  + 0.3V applied to this device.

- 2. Best fit (99% of full-scale).

- 3. It includes all errors from on-chip PGA and reference.

- 4. Gain temperature drift is defined as the maximum change of gain error measured over the specified temperature range. The gain error drift is calculated using the box method, as described by Equation: Gain Error Drift =  $(GE_{MAX} GE_{MIN})/(T_{MAX} T_{MIN})$ .

#### Where:

- GE<sub>MAX</sub> and GE<sub>MIN</sub> are the maximum and minimum gain errors, respectively.

- $T_{MAX}$  and  $T_{MIN}$  are the maximum and minimum temperatures, respectively, over the temperature range -40°C to +125°C.

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 3.3V, DR = 5SPS, full-scale input voltage range (FSR) = \pm 2.048V, internal reference, maximum and minimum specifications apply from <math>T_A = -40^{\circ}C$  to +125°C, typical values are measured at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                           | SYMBOL          |                           | CONDITIONS                      | MIN                   | TYP  | MAX                   | UNITS |

|-------------------------------------|-----------------|---------------------------|---------------------------------|-----------------------|------|-----------------------|-------|

| Reference                           |                 |                           |                                 |                       |      | •                     |       |

| External Reference                  |                 |                           |                                 | 0.5                   |      | 2.5                   | V     |

| External Reference Input<br>Current |                 | V <sub>REFIN</sub> = 2.5\ | /, continuous mode              |                       | 2.35 |                       | μΑ    |

| Digital Input/Output                |                 |                           |                                 |                       |      |                       |       |

| High Input Voltage (5)              | V <sub>IH</sub> |                           |                                 | 0.7 × V <sub>DD</sub> |      |                       | V     |

| Low Input Voltage (5)               | V <sub>IL</sub> |                           |                                 |                       |      | 0.3 × V <sub>DD</sub> | V     |

| Low Output Voltage                  | V <sub>OL</sub> | I <sub>OL</sub> = 3mA     |                                 |                       | 0.13 | 0.4                   | V     |

| High Input Leakage Current (6)      | I <sub>IH</sub> | V <sub>IH</sub> = 5.5V    |                                 |                       | 0.1  | 1                     | μA    |

| Low Input Leakage Current (6)       | I <sub>IL</sub> | V <sub>IL</sub> = GND     |                                 |                       | 0.1  | 1                     | μA    |

| Power Supply Requirements           |                 |                           |                                 |                       |      |                       |       |

| Power Supply Voltage                | $V_{DD}$        |                           |                                 | 2                     |      | 5.5                   | V     |

|                                     |                 |                           | Power-down current at +25°C     |                       | 0.65 | 1.2                   |       |

| Committee Comment                   |                 | \/ - F F\/                | Power-down current up to +125°C |                       |      | 3.5                   |       |

| Supply Current                      | I <sub>DD</sub> | $V_{DD} = 5.5V$           | Operating current at +25°C      |                       | 310  | 380                   | μA    |

|                                     |                 |                           | Operating current up to +125°C  |                       |      | 400                   |       |

| Dawan Diagination                   | -               | $V_{DD} = 5V$             |                                 |                       | 1.5  |                       | \^/   |

| Power Dissipation                   | P <sub>D</sub>  | $V_{DD} = 3.3V$           |                                 |                       | 0.8  |                       | mW    |

#### NOTES:

6. Meet the "loss of V<sub>DD</sub>" requirement of I<sup>2</sup>C fast mode. When V<sub>DD</sub> is lost, the leakage drawn from the pin is controlled.

<sup>5.</sup> There are two scenarios:  $V_{DD}$  = 5V,  $V_{BUS}$  can be 2V to 5V.  $V_{DD}$  = 3.3V,  $V_{BUS}$  should be 3.3V. Note that  $V_{BUS}$  = 2V may cause leakage in some extreme conditions, and it is better to make it higher than 3.1V. For  $V_{BUS}$  =  $V_{DD}$ ,  $V_{IL}/V_{IH}$  = 30%/70% of  $V_{BUS}$ . For  $V_{BUS}$  = 3.3V and  $V_{DD}$  = 5V,  $V_{IL}/V_{IH}$  = 20%/80% of  $V_{BUS}$ .

## **TIMING CHARACTERISTICS**

| PARAMETER                                                                                    | SYMBOL           | CONDITIONS | FAST | FAST MODE HIGH-SPEED MO |      | ED MODE | UNITS |

|----------------------------------------------------------------------------------------------|------------------|------------|------|-------------------------|------|---------|-------|

| PARAMETER                                                                                    | STIVIBUL         | CONDITIONS | MIN  | MAX                     | MIN  | MAX     | UNITS |

| SCL Operating Frequency                                                                      | f <sub>SCL</sub> |            | 0.01 | 0.4                     | 0.01 | 3.4     | MHz   |

| Bus Free Time between START and STOP Conditions                                              | t <sub>1</sub>   |            | 1300 |                         | 160  |         | ns    |

| Hold Time after Repeated START Condition.<br>After This Period, the First Clock is Generated | t <sub>2</sub>   |            | 600  |                         | 160  |         | ns    |

| SCL Clock Low Time                                                                           | t <sub>3</sub>   |            | 1300 |                         | 160  |         | ns    |

| SCL Clock High Time                                                                          | t <sub>7</sub>   |            | 600  |                         | 60   |         | ns    |

| Repeated START Condition Setup Time                                                          | t <sub>9</sub>   |            | 600  |                         | 160  |         | ns    |

| STOP Condition Setup Time                                                                    | t <sub>10</sub>  |            | 600  |                         | 160  |         | ns    |

| Data Hold Time                                                                               | t <sub>5</sub>   |            | 0    |                         | 0    |         | ns    |

| Data Setup Time                                                                              | t <sub>8</sub>   |            | 100  |                         | 10   |         | ns    |

| Clock/Data Fall Time (1)                                                                     | t <sub>6</sub>   |            |      | 300                     |      | 40      | ns    |

| Clock/Data Rise Time                                                                         | t <sub>4</sub>   |            |      | 300                     |      | 80      | ns    |

#### NOTE:

1.  $t_6$  (MIN) for SDA output is 20ns for normal/fast mode and 10ns for high-speed mode. Glitch filter capability is 50ns for normal/fast mode and 10ns for high-speed mode.

Figure 1. I<sup>2</sup>C Timing Diagram

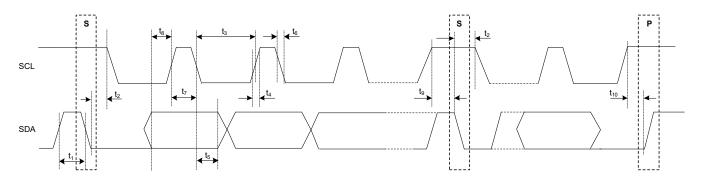

#### TYPICAL PERFORMANCE CHARACTERISTICS

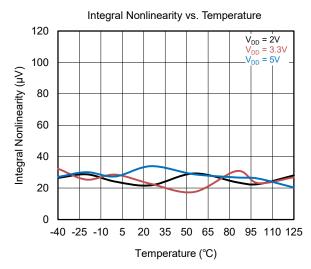

$T_A = +25$ °C,  $V_{DD} = 3.3$ V, FSR =  $\pm 2.048$ V, DR = 5SPS, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25$ °C,  $V_{DD} = 3.3$ V, FSR =  $\pm 2.048$ V, DR = 5SPS, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25$ °C,  $V_{DD} = 3.3$ V, FSR =  $\pm 2.048$ V, DR = 5SPS, unless otherwise noted.

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Functional Block Diagram

#### **DETAILED DESCRIPTION**

#### Overview

The SGM51610C is a low-power, 16-bit, sigma-delta ( $\Sigma$ - $\Delta$ ) analog-to-digital converter (ADC).

The SGM51610C supports both differential inputs and single-ended inputs.

The SGM51610C has two working modes: single-shot mode and continuous conversion mode.

In single-shot mode, the ADC performs one conversion and gives full settled data, no data needs to be discarded. Once ADC completes the conversion, it then goes to low-power shutdown mode.

In continuous mode, the ADC will achieve the first fully settled data without discarding any data, similar in single-shot mode. And the ADC begins a new conversion automatically after a previous conversion is completed. Every conversion result is given out. The data rate is equal to the configured data rate.

#### **Quickstart Guide**

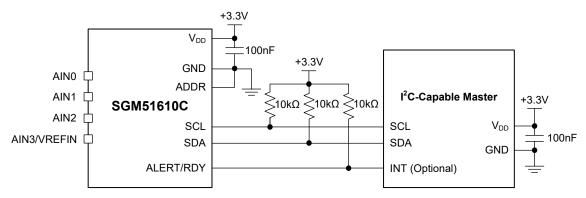

The basic connection of ADC is shown in Figure 3. The communication interface is  $I^2C$  compatible. The SGM51610C works in slave mode. The  $I^2C$  address is configured as 0b1001000 (ADDR is connected to GND).

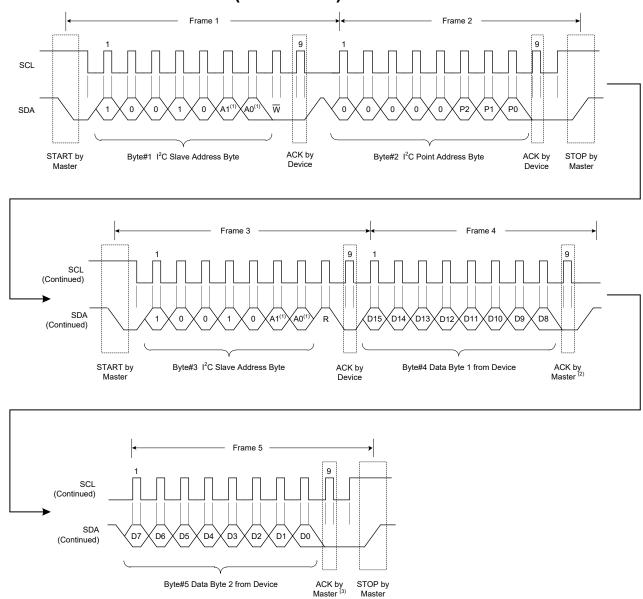

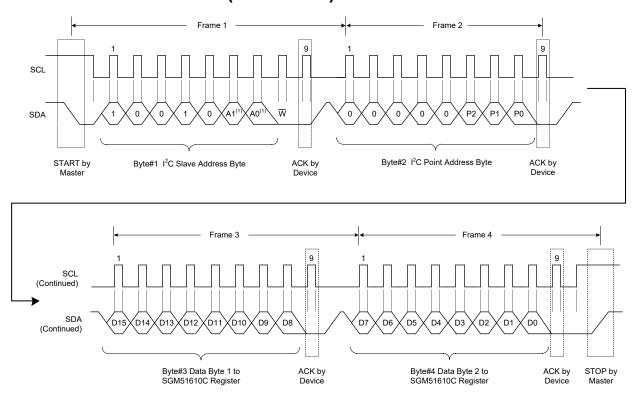

Figure 4 and Figure 5 show the demo read and write operation sequences.

For example, writing to the configuration register 0x1 sets the SGM51610C to continuous conversion mode, the following order can be followed:

- 1. The first byte, 0b1001000 (first 7-bit is I<sup>2</sup>C address), the 8<sup>th</sup> bit is read/write bit which is low writing now

- 2. The second byte, 0b00000001 (points to Config register 0x1)

- 3. The third byte, 0b10000100 (MSB of the Config register to be written, Bit[8] = '0' means the continuous mode)

- 4. The fourth byte, 0b10000011 (LSB of the Config register to be written, Bit[7:5] = '100' means data rate 100Hz)

For example, to read the conversion result from SGM51610C, the following order can be followed:

- 1. The first byte, 0b1001000 (first 7-bit is I<sup>2</sup>C address), the 8<sup>th</sup> bit is read/write bit which is low writing now

- 2. The second byte, 0b00000000 (points to Conversion register 0x0)

- 3. The third byte, 0b10010001 (first 7-bit is  $I^2C$  address), the  $8^{th}$  bit is read/write bit which is high reading now

- 4. The fourth byte, the SGM51610C answers with the MSB of the Conversion register

- 5. The fifth byte, the SGM51610C answers with the LSB of the Conversion register

Figure 3. Basic Hardware Configuration

#### NOTES:

- 1. The A0 and A1 values depend on the ADDR pin.

- 2. SDA can be set high by master to terminate a single-byte read operation.

- 3. SDA can be set high by master to terminate a two-byte read operation.

Figure 4. Timing Diagram for Read Word Register

#### NOTE:

1. The A0 and A1 values depend on the ADDR pin.

Figure 5. Timing Diagram for Write Word Register

#### Multiplexer

The SGM51610C has a flexible input multiplexer. It can be configured as 2 differential inputs or 4 single-ended inputs.

Whether the input is configured as differential inputs or single-ended inputs, the absolute voltage on any inputs pin must be in the range from GND to  $V_{\rm DD}$ .

#### **Analog Inputs**

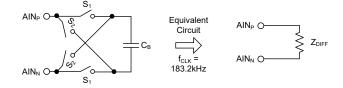

The SGM51610C has a switched capacitor input stage. There are charge and discharge current when ADC is working. The equal effective input impedance can be estimated by  $R_{\text{EFF}} = V_{\text{IN}}/I_{\text{AVERAGE}}$ .

The differential input impedance is  $Z_{\text{DIFF}}$  in Figure 6. Table 1 shows the typical differential input impedance.

Figure 6. Simplified Analog Input Circuit

**Table 1. Differential Input Impedance**

| FSR (V)               | Differential Input Impedance (MΩ) |

|-----------------------|-----------------------------------|

| ±6.144 <sup>(1)</sup> | 2.3                               |

| ±4.096 <sup>(1)</sup> | 2.1                               |

| ±2.048                | 1.4                               |

| ±1.024                | 1.2                               |

| ±0.512                | 0.752                             |

| ±0.256                | 0.452                             |

#### NOTE:

1. FSR = Full-scale range of the ADC scaling. In any event, it should not exceed  $V_{DD}$  + 0.3V applied to this device.

#### **Full-Scale Input**

The SGM51610C has an internal PGA. The PGA can be set to gains of 2/3, 1, 2, 4, 8 or 16. Table 2 and Table 3 show the corresponding full-scale ranges (FSR).

Analog input voltages can never exceed the analog input voltage limits.

Table 2. PGA Gain Full-Scale Range with Internal Reference

| PGA Setting | FSR (V)               |

|-------------|-----------------------|

| 2/3         | ±6.144 <sup>(1)</sup> |

| 1           | ±4.096 <sup>(1)</sup> |

| 2           | ±2.048                |

| 4           | ±1.024                |

| 8           | ±0.512                |

| 16          | ±0.256                |

#### NOTE:

1. FSR = Full-scale range of the ADC scaling. In any event, it should not exceed  $V_{DD}$  + 0.3V applied to this device.

Table 3. PGA Gain Full-Scale Range with External Reference

| FSR (V)                        |

|--------------------------------|

| ±6.144 × V <sub>REF</sub> /1.2 |

| ±4.096 × V <sub>REF</sub> /1.2 |

| ±2.048 × V <sub>REF</sub> /1.2 |

| ±1.024 × V <sub>REF</sub> /1.2 |

| ±0.512 × V <sub>REF</sub> /1.2 |

| ±0.256 × V <sub>REF</sub> /1.2 |

|                                |

#### **Data Format**

The SGM51610C conversion result data is in binary two's complement format.

Table 4 shows the ideal output codes for different input signals.

Table 4. Ideal Output Code for Different Input Signals

| table 4: lacal Output Code for Different input Oighais              |                       |  |  |  |  |

|---------------------------------------------------------------------|-----------------------|--|--|--|--|

| Input Signal V <sub>IN</sub> (AIN <sub>P</sub> - AIN <sub>N</sub> ) | Ideal Output Code (1) |  |  |  |  |

| ≥ FS (2 <sup>15</sup> - 1)/2 <sup>15</sup>                          | 7FFFh                 |  |  |  |  |

| +FS/2 <sup>15</sup>                                                 | 0001h                 |  |  |  |  |

| 0                                                                   | 0                     |  |  |  |  |

| -FS/2 <sup>15</sup>                                                 | FFFFh                 |  |  |  |  |

| ≤-FS                                                                | 8000h                 |  |  |  |  |

#### NOTE:

1. Except for effects of INL, noise, offset, and gain errors.

#### Aliasing

For some applications, an RC external filtering is recommended.

#### **Operating Modes**

The SGM51610C has two working modes, continuous mode and single-shot mode.

In continuous mode, the ADC begins a new conversion automatically after a previous conversion is completed. Every conversion result is given out.

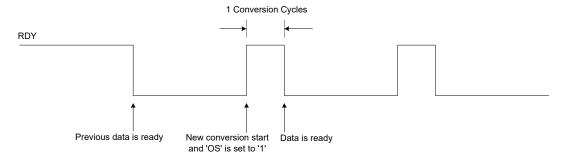

In single-shot mode, if OS bit is written to '1', a single-shot conversion is started, during the conversion process, the OS bit is kept '0', and the chip doesn't response to OS bit operation. If conversion data is ready, the OS bit is set to '1' and the chip goes power-down automatically, and user can write '1' to OS bit to call a single-shot conversion again.

#### **Power-Up and Reset**

When the SGM51610C is powered up, all registers are reset to default values.

The SGM51610C supports  $I^2C$  general call reset command. See  $I^2C$  General Call section for details.

#### **Duty Cycling for Low-Power**

In some power sensitive application, the SGM51610C can work in sampling and power-down mode periodically. The duty cycle of working time and power-down time can be controlled by microcontroller flexibly.

For example, if the SGM51610C is configured as sample data rate at 960Hz, it can be operated with 125ms duty cycle. It means that if the chip is called to do single-shot conversion every 125ms, it will take the chip 1.2ms for sampling and then stay in power-down mode for 123.8ms. Under this working mode, it will reduce 103/104 power consumption compare with 960Hz operation in continuous mode.

#### **Data Rate**

Table 5. ADC Output Data Rate (SPS)

| DR[2:0] Bits<br>in Config Register | ODR   |

|------------------------------------|-------|

| 000                                | 5Hz   |

| 001                                | 10Hz  |

| 010                                | 20Hz  |

| 011                                | 50Hz  |

| 100                                | 100Hz |

| 101                                | 200Hz |

| 110                                | 480Hz |

| 111                                | 960Hz |

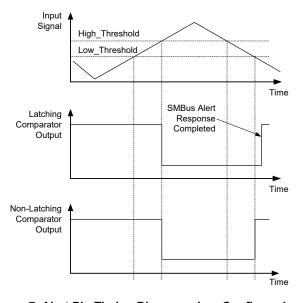

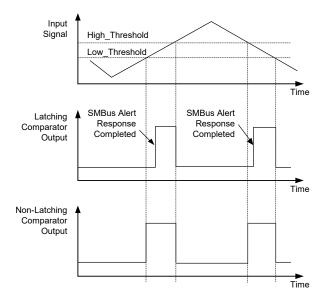

#### Comparator

The SGM51610C has an inside comparator that can be used to check ADC conversion results with high threshold and low threshold. When the result exceeds the limited setting, the chip can give an alert on the ALERT/RDY pin.

The comparator has two workings modes: traditional mode and window comparator mode. These modes are configurable. Under both working modes, the comparator can be configured as latch output or no-latch output (COMP\_LAT bit in Config register). In latch output mode, the latched

response or by reading the Conversion register. The ALERT/RDY pin output active polarity (low or high) can be configured by COMP\_POL bit in Config register. Demos are shown in Figure 7 and Figure 8.

The comparator output trigger waiting times can be set by

comparator output can be cleared by issuing an SMBus alert

The comparator output trigger waiting times can be set by COMP\_QUE[1:0] bits in Config register. It means comparator output can wait until the ADC results beyond the threshold configured times (which can be one, two, or four times). See Config Register section for details.

Figure 7. Alert Pin Timing Diagram when Configured as a Traditional Comparator

Figure 8. Alert Pin Timing Diagram when Configured as a Window Comparator

#### **ADC Noise**

Table 6. ADC Noise with Internal Reference (RMS in µV)

| DR<br>FSR | 960   | 480   | 200   | 100   | 50    | 20    | 10    | 5     |

|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 6.144     | 187.5 | 187.5 | 187.5 | 187.5 | 187.5 | 187.5 | 187.5 | 187.5 |

| 4.096     | 125   | 125   | 125   | 125   | 125   | 125   | 125   | 125   |

| 2.048     | 62.5  | 62.5  | 62.5  | 62.5  | 62.5  | 62.5  | 62.5  | 62.5  |

| 1.024     | 31.25 | 31.25 | 31.25 | 31.25 | 31.25 | 31.25 | 31.25 | 31.25 |

| 0.512     | 15.62 | 15.62 | 15.62 | 15.62 | 15.62 | 15.62 | 15.62 | 15.62 |

| 0.256     | 7.81  | 7.81  | 7.81  | 7.81  | 7.81  | 7.81  | 7.81  | 7.81  |

Table 7. ADC ENOB (ENOB = In(FSR/V<sub>RMS-Noise</sub>)/In(2))

| DR<br>FSR | 960 | 480 | 200 | 100 | 50 | 20 | 10 | 5  |

|-----------|-----|-----|-----|-----|----|----|----|----|

| 6.144     | 16  | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

| 4.096     | 16  | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

| 2.048     | 16  | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

| 1.024     | 16  | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

| 0.512     | 16  | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

| 0.256     | 16  | 16  | 16  | 16  | 16 | 16 | 16 | 16 |

#### **Digital Filter**

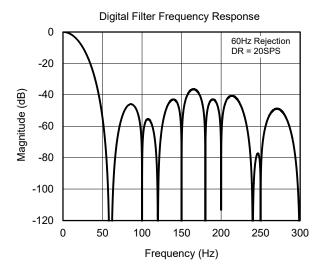

The SGM51610C features a finite impulse response (FIR) digital filter with linear-phase characteristics. This filter serves a dual purpose, filtering and decimating the incoming digital data stream from the modulator. Notably, the digital filter automatically adapts to different data rates, ensuring a settling process within a single cycle. Operating at data rates of 5SPS, 10SPS and 20SPS, the filter configuration provides flexibility to reject either 50Hz or 60Hz line frequencies. One bit (DR\_SEL) in the configuration register enables easy customization of the filter's behavior.

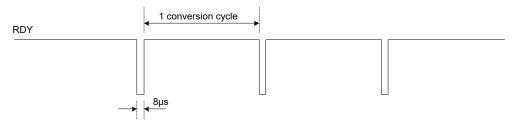

#### **Conversion Ready Pin**

If ALERT/RDY pin is used as a conversion ready pin, the following operations need to be followed, firstly set the MSB (Most Significant Bit) of the high threshold register to '1', secondly set the MSB of the low threshold register to '0', and select COMP\_QUE[1:0] bits in '00' mode. It should be noted that COMP\_QUE[1:0] bits can disable this pin function. The COMP\_MODE and COMP\_LAT bits have no affection on this function.

The ALERT/RDY pin is an open-drain output, it needs a pull-up resistor outside.

When the SGM51610C works in continuous mode, the ALERT/RDY pin gives a pulse ( $\sim$ 8 $\mu$ s) at the end of every conversion completion.

When the SGM51610C works in single-shot mode, the ALERT/RDY pin goes low (COMP\_POL bit is set to '0') when the conversion data is ready, and keeps low until the next conversion starts. Please see demos in Figure 9 and Figure 10.

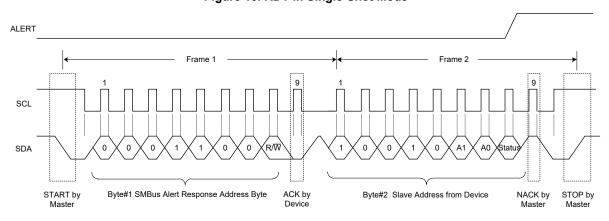

#### **SMBus Alert Response**

The ALERT/RDY pin can output as an SMBus alert. When it is in latch mode, the COMP\_LAT bit is set to '1'. If an ADC result is above the upper threshold or below the lower threshold, this pin is set (active low or active high). And the pin output is latched, it can be cleared by reading ADC conversion data, or by issuing an SMBus alert response (reading the alerting device I<sup>2</sup>C address).

If an alert is output at the ALERT/RDY pin and latched, the master controller accepts the alert, it sent an SMBus alert command (0b00011001) to I<sup>2</sup>C bus. Any SGM51610C on the bus will response with their own address, the lowest I<sup>2</sup>C address chip will occupy the bus and it will clear itself ALERT/RDY pin, the chip which loses I<sup>2</sup>C bus will keep alert on ALERT/RDY pin. The master will repeat SMBus alert command until all salve chips clear their alert.

In a multiple I<sup>2</sup>C devices system, there are two scenarios to note about clearing an alert on ALERT/RDY pin. The first scenario is, to clear an alert on ALERT/RDY pin of SGM51610C by sending an SMBus alert command (0x19), it must be committed that there is only one SGM51610C device in system, meanwhile make sure that SGM51610C keeps the lowest address. Another scenario is, to clear an alert on ALERT/RDY pin of SGM51610C by reading data register (0x0) of SGM51610C, it needs to be committed that there are multiple SGM51610C chips in the system (need to read SGM51610Cs' data registers one by one) or there is only one SGM51610C chip in the system.

When ALERT/RDY pin is configured as window comparator mode, if ADC result is higher than upper threshold or ADC result is below the lower threshold, the pin is set (active low or active high).

Timing diagram for SMBus alert response is shown in Figure 11.

Figure 9. RDY in Continuous Mode

Figure 10. RDY in Single-Shot Mode

NOTE:

1. The A0 and A1 values depend on the ADDR pin.

Figure 11. Timing Diagram for SMBus Alert Response

#### I<sup>2</sup>C Interface

The SGM51610C communication interface is an  $I^2C$  interface. The SGM51610C can only act as slave devices. An  $I^2C$  timing diagram is shown in Figure 1.

#### I<sup>2</sup>C Address Selection

The SGM51610C has a separate address setting pin ADDR, which can be connected to GND,  $V_{DD}$ , SDA and SCL. Table 8 shows the four available addresses.

Table 8. ADDR Pin Connection and Corresponding Slave Address

| ADDR Pin | Slave Address |

|----------|---------------|

| GND      | 1001000       |

| $V_{DD}$ | 1001001       |

| SDA      | 1001010       |

| SCL      | 1001011       |

#### I<sup>2</sup>C General Call

The SGM51610C supports  $I^2$ C general call address (0000000) and the eighth bit must be '0'. The device acknowledges the

general call address. And if the second byte is 00000110 (06h), the SGM51610C resets all registers and goes to power-down.

#### I<sup>2</sup>C Speed Modes

The I<sup>2</sup>C bus operation supports three speed modes: standard mode, fast mode, and high-speed mode. See Timing Characteristics section for more details.

To enter standard and fast mode, it needs no special operation.

To enter high-speed mode, send a special address byte of 00001XXX following the I<sup>2</sup>C start condition. The SGM51610C doesn't give an ACK (acknowledge) to this byte, the SGM51610C switches to high-speed mode after receiving this byte. The SGM51610C quits high-speed mode with the next STOP condition.

#### **Slave Mode Operations**

The SGM51610C works in slave mode and doesn't drive the SCL line.

#### **REGISTER MAPS**

#### **Register Address**

The SGM51610C has seven pointer registers. Table 9 and Table 10 show these register maps. Figure 4 shows how to access this pointer registers.

Table 9. Register Address

| Address | Register                          |

|---------|-----------------------------------|

| 0x0     | Conversion Register               |

| 0x1     | Config Register                   |

| 0x2     | Low_Thresh Register               |

| 0x3     | High_Thresh Register              |

| 0x4     | Config1 Register                  |

| 0x5     | Chip_ID Register                  |

| 0x6     | GN_Trim1 Register for EXT_REF bit |

#### **Pointer Register**

#### Table 10. Pointer Register Byte (Write-Only)

MSB

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

0

0

0

Register Address

#### **REG0x0:** Conversion Register [Reset = 0x0000]

The ADC conversion result is 16-bit two's complement format. Table 11 shows the data format. Its reset default value is '0'.

#### Table 11. 16-Bit Conversion Register (Read-Only)

MSB LSB

| Bit | 15 Bit | 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|--------|----|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| D1  | 5 D    | 14 | D13    | D12    | D11    | D10    | D9    | D8    | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

**LSB**

## **REGISTER MAPS (continued)**

## **REG0x1: Config Register [Reset = 0x8583]**

The configuration register (Config Register) is shown in Table 12.

Table 12. Config Register Details

| Table 12. | Config Register | Details |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-----------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BITS      | BIT NAME        | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| D[15]     | os              | 1       | R/W  | Working Status/Single-Shot Conversion Start For a write status: 0 = No effect 1 = Start a single conversion (when in single-shot mode)  For a read status: 0 = The chip is doing a conversion 1 = The chip is not doing a conversion This bit reports the status of the chip. It can only be written when the chip is in power-down.                                                                                                                                                      |

| D[14:12]  | MUX[2:0]        | 000     | R/W  | Input Multiplexer (MUX) Configuration $000 = AIN_P = AIN0 \text{ and } AIN_N = AIN1 \text{ (default)}$ $001 = AIN_P = AIN0 \text{ and } AIN_N = AIN3$ $010 = AIN_P = AIN1 \text{ and } AIN_N = AIN3$ $011 = AIN_P = AIN2 \text{ and } AIN_N = AIN3$ $100 = AIN_P = AIN0 \text{ and } AIN_N = GND$ $101 = AIN_P = AIN1 \text{ and } AIN_N = GND$ $110 = AIN_P = AIN2 \text{ and } AIN_N = GND$ $111 = AIN_P = AIN3 \text{ and } AIN_N = GND$ $111 = AIN_P = AIN3 \text{ and } AIN_N = GND$ |

| D[11:9]   | PGA[2:0]        | 010     | R/W  | Programmable Gain Amplifier (PGA) Configuration  000 = FSR = ±6.144V (1)  001 = FSR = ±4.096V (1)  010 = FSR = ±2.048V (default)  011 = FSR = ±1.024V  100 = FSR = ±0.512V  101 = FSR = ±0.256V  110 = FSR = ±0.256V  111 = FSR = ±0.256V                                                                                                                                                                                                                                                 |

| D[8]      | MODE            | 1       | R/W  | Device Operating Mode 0 = Continuous conversion mode 1 = Power-down single-shot mode (default)                                                                                                                                                                                                                                                                                                                                                                                            |

| D[7:5]    | DR[2:0]         | 100     | R/W  | Data Rate These bits control the data rate setting. See Table 5.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D[4]      | COMP_MODE       | 0       | R/W  | Comparator Mode 0 = A traditional comparator with hysteresis (default) 1 = A window comparator                                                                                                                                                                                                                                                                                                                                                                                            |

| D[3]      | COMP_POL        | 0       | R/W  | Comparator Polarity 0 = Active low (default) 1 = Active high This bit sets the active polarity of the ALERT/RDY pin.                                                                                                                                                                                                                                                                                                                                                                      |

| D[2]      | COMP_LAT        | 0       | R/W  | Latching Comparator 0 = Non-latching comparator (default) 1 = Latching comparator This bit sets whether the ALERT/RDY pin latches once its outputs sets or resets when ADC conversion result is within the upper and lower threshold limitations.                                                                                                                                                                                                                                         |

| D[1:0]    | COMP_QUE[1:0]   | 11      | R/W  | Comparator Queue and Disable Function 00 = Assert after one conversion 01 = Assert after two conversions 10 = Assert after four conversions 11 = Disable comparator (default) These bits can disable the comparator. They can set the required times of successive ADC conversion beyond the threshold before an alert output on ALERT/RDY pin.                                                                                                                                           |

#### NOTE:

1. This is a theoretical full-scale range of the ADC scaling. The real input must be within the electrical limitation (0V to  $V_{DD}$  + 0.3V).

## **REGISTER MAPS (continued)**

## REG0x2 ~ REG0x3: Low\_Thresh [Reset = 0x8000] and High\_Thresh [Reset = 0x7FFF] Registers

The lower (Low\_Thresh) and upper (High\_Thresh) threshold registers are in 16-bit two's complement format. Table 13 shows these two register format.

Table 13. Low\_Thresh and High\_Thresh Registers Format (Read/Write)

|        | Low_Thresh Register |        |            |             |        |                  |       |  |  |  |  |

|--------|---------------------|--------|------------|-------------|--------|------------------|-------|--|--|--|--|

| Bit 15 | Bit 14              | Bit 13 | Bit 12     | Bit 11      | Bit 10 | t 10 Bit 9 Bit 8 |       |  |  |  |  |

|        | Low_Thresh[15:8]    |        |            |             |        |                  |       |  |  |  |  |

| Bit 7  | Bit 6               | Bit 5  | Bit 4      | Bit 3       | Bit 2  | Bit 1            | Bit 0 |  |  |  |  |

|        | Low_Thresh[7:0]     |        |            |             |        |                  |       |  |  |  |  |

|        |                     |        |            |             |        |                  |       |  |  |  |  |

|        |                     |        | High_Thres | sh Register |        |                  |       |  |  |  |  |

| Bit 15 | Bit 14              | Bit 13 | Bit 12     | Bit 11      | Bit 10 | Bit 9            | Bit 8 |  |  |  |  |

|        |                     |        | High_Thr   | esh[15:8]   |        |                  |       |  |  |  |  |

| Bit 7  | Bit 6               | Bit 5  | Bit 4      | Bit 3       | Bit 2  | Bit 1            | Bit 0 |  |  |  |  |

|        | High_Thresh[7:0]    |        |            |             |        |                  |       |  |  |  |  |

#### **REG0x4: Config1 Register [Reset = 0x0000]**

Table 14. 16-Bit Config1 Register Details

| 1able 14. 1 | 6-Bit Config1 Re | egister Deta | IIS  |                                                                                                                                                                                                                                                                                                                        |

|-------------|------------------|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BITS        | BIT NAME         | DEFAULT      | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                            |

| D[15:9]     | Reserved         | 000 0000     | R/W  |                                                                                                                                                                                                                                                                                                                        |

| D[8]        | PD               | 0            | R/W  | Writing '1' to PD powers down this part, and this PD bit is automatically cleared internally. Another continuous/single conversion can be carried out again without the need to clear this bit.                                                                                                                        |

| D[7]        | DR_SEL           | 0            | R/W  | FIR Filter Configuration This specific bit is designated for the customization of filter coefficients dedicated to the internal finite impulse response (FIR) filter. Kindly employ these bits in conjunction with the 5SPS, 10SPS and 20SPS configuration.  0 = 50Hz rejection only (default) 1 = 60Hz rejection only |

| D[6:4]      | Reserved         | 000          | R/W  |                                                                                                                                                                                                                                                                                                                        |

| D[3]        | EXT_REF          | 0            | R/W  | 0 = None (default)<br>1 = Use AIN3 as external reference for ADC                                                                                                                                                                                                                                                       |

| D[2:0]      | Reserved         | 000          | R/W  |                                                                                                                                                                                                                                                                                                                        |

#### REG0x5: Chip\_ID Register [Reset = 0x0280]

Table 15. 16-Bit Chip\_ID Register for Identifying Chip ID and Its Subversions (Read-Only)

| BITS     | BIT NAME | DEFAULT | TYPE | DESCRIPTION |

|----------|----------|---------|------|-------------|

| D[15:13] | Reserved | 000     | R    | Reserved.   |

| D[12:8]  | ID[4:0]  | 0 0010  | R    |             |

| D[7:5]   | VER[2:0] | 100     | R    |             |

| D[4:0]   | Reserved | 0 0000  | R    | Reserved.   |

## **REGISTER MAPS (continued)**

#### REG0x6: GN\_Trim1 Register (When Using EXT\_REF Bit) [Reset = 0x999A]

The ADC gain coefficient for user selecting Config1 register EXT\_REF bit as reference. A default value is provided and the user is responsible for writing proper value to the register if they want to compensate external reference error. This register does not take effect when EXT\_REF = 0 and the internal reference is selected.

Table 16. GN\_Trim1 Register Format

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8 |

|--------|--------|--------|--------|--------|--------|---------|-------|

| GN15   | GN14   | GN13   | GN12   | GN11   | GN10   | GN9     | GN8   |

| 1      | 0      | 0      | 1      | 1      | 0      | 0       | 1     |

| Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0 |

| GN7    | GN6    | GN5    | GN4    | GN3    | GN2    | GN2 GN1 |       |

| 1      | 0      | 0      | 1      | 1      | 0      | 1       | 0     |

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Original (DECEMBER 2024) to REV.A

Page

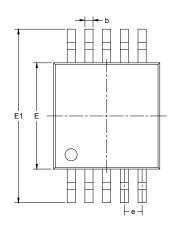

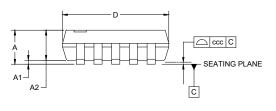

## **PACKAGE OUTLINE DIMENSIONS** MSOP-10

#### RECOMMENDED LAND PATTERN (Unit: mm)

| Cymphal | Di    | mensions In Millimet | ers   |  |  |

|---------|-------|----------------------|-------|--|--|

| Symbol  | MIN   | NOM                  | MAX   |  |  |

| Α       | -     | -                    | 1.100 |  |  |

| A1      | 0.000 | -                    | 0.150 |  |  |

| A2      | 0.750 | -                    | 0.950 |  |  |

| b       | 0.170 | -                    | 0.330 |  |  |

| С       | 0.080 | -                    | 0.230 |  |  |

| D       | 2.900 | -                    | 3.100 |  |  |

| Е       | 2.900 | -                    | 3.100 |  |  |

| E1      | 4.750 | -                    | 5.050 |  |  |

| е       |       | 0.500 BSC            |       |  |  |

| Н       |       | 0.250 TYP            |       |  |  |

| L       | 0.400 | -                    | 0.800 |  |  |

| θ       | 0°    | -                    | 8°    |  |  |

| ccc     |       | 0.100                |       |  |  |

#### NOTES:

- This drawing is subject to change without notice.

The dimensions do not include mold flashes, protrusions or gate burrs.

Reference JEDEC MO-187.

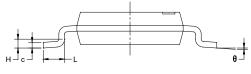

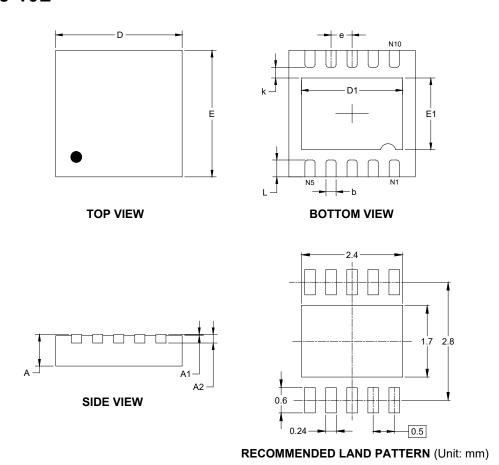

# PACKAGE OUTLINE DIMENSIONS TDFN-3×3-10L

| Symbol   |       | nsions<br>meters | Dimensions<br>In Inches |       |  |  |

|----------|-------|------------------|-------------------------|-------|--|--|

| <b>J</b> | MIN   | MAX              | MIN                     | MAX   |  |  |

| А        | 0.700 | 0.800            | 0.028                   | 0.031 |  |  |

| A1       | 0.000 | 0.050            | 0.000                   | 0.002 |  |  |

| A2       | 0.203 | REF              | 0.008 REF               |       |  |  |

| D        | 2.900 | 3.100            | 0.114                   | 0.122 |  |  |

| D1       | 2.300 | 2.600            | 0.091                   | 0.103 |  |  |

| E        | 2.900 | 3.100            | 0.114                   | 0.122 |  |  |

| E1       | 1.500 | 1.800            | 0.059                   | 0.071 |  |  |

| k        | 0.200 | MIN              | 0.008                   | 3 MIN |  |  |

| b        | 0.180 | 0.300            | 0.007                   | 0.012 |  |  |

| е        | 0.500 | ) TYP            | 0.020 TYP               |       |  |  |

| L        | 0.300 | 0.500            | 0.012 0.02              |       |  |  |

NOTE: This drawing is subject to change without notice.

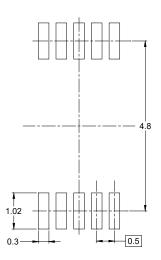

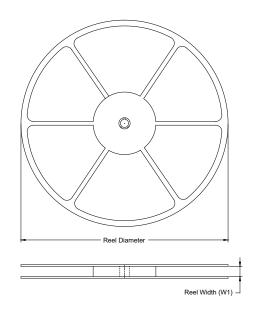

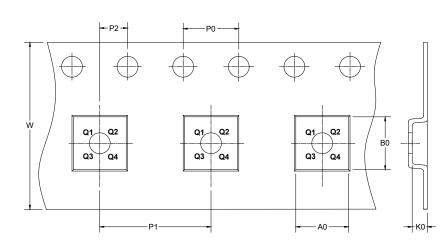

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

#### **TAPE DIMENSIONS**

DIRECTION OF FEED

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| MSOP-10      | 13"              | 12.4                     | 5.20       | 3.30       | 1.50       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| TDFN-3×3-10L | 13"              | 12.4                     | 3.35       | 3.35       | 1.13       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

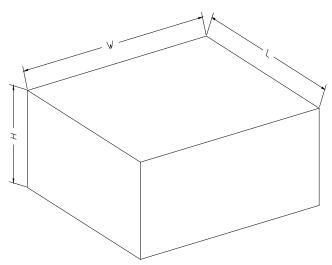

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-----------|----------------|---------------|----------------|--------------|

| 13"       | 386            | 280           | 370            | 5            |