SGM5202-14 Low-Power, 14-Bit, 1MSPS, 8 Channels Unipolar Inputs Analog-to-Digital Converter with Serial Interface

## **GENERAL DESCRIPTION**

The SGM5202-14 is a 14-bit, high-precision, multichannel input, successive approximation (SAR) analog-to-digital converter (ADC).

The SGM5202-14 supports 8 single-ended inputs. The SGM5202-14 needs to work with an external voltage reference. Its available range is 1.2V to 4.2V. The digital interface is compatible to the traditional SPI protocol.

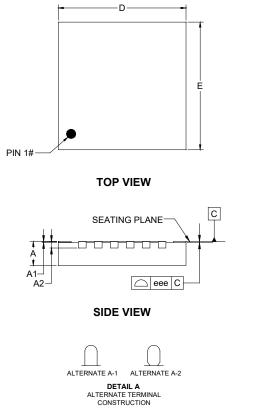

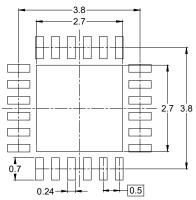

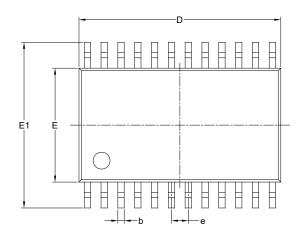

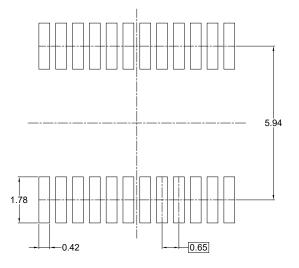

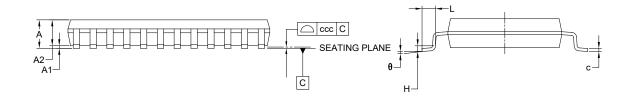

The SGM5202-14 is available in Green TQFN-4×4-24L and TSSOP-24 packages. It operates over an ambient temperature range  $-40^{\circ}$ C to  $+125^{\circ}$ C.

# APPLICATIONS

Industrial Process Control Factory Automation Equipment Lab Instrumentations

# FEATURES

- Supply Voltage Ranges:

- Analog Supply: 2.7V to 5.5V

- Digital I/O Supply: 2.7V to V<sub>A</sub> + 0.2V

- Sampling Rate: Up to 1MSPS

- Excellent DC Performance

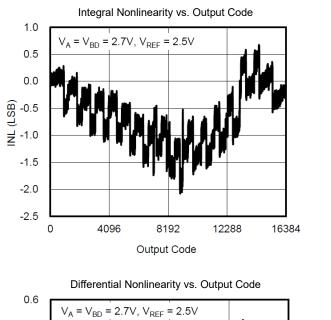

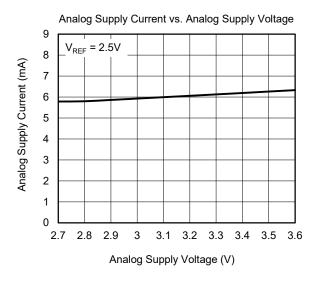

- Integral Nonlinearity (INL): ±2LSB (TYP), 6LSB (MAX) at 2.7V

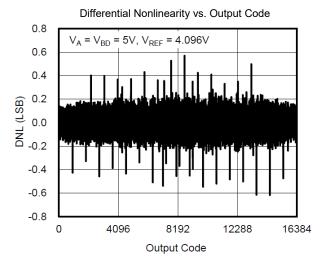

- Differential Nonlinearity (DNL): ±0.7LSB (TYP), 3LSB (MAX) at 2.7V

- Excellent AC Performance at 5V, f<sub>IN</sub> = 1kHz

- Signal-to-Noise Ratio (SNR): 81.5dB (TYP)

- Spurious Free Dynamic Range (SFDR): 90.4dB (TYP)

- Total Harmonic Distortion (THD): -87.9dB (TYP)

- Flexible Input Multiplexer

- Support Daisy-Chain Connection

- SPI-Compatible Serial Interface

- Available in Green TQFN-4×4-24L and TSSOP-24 Packages

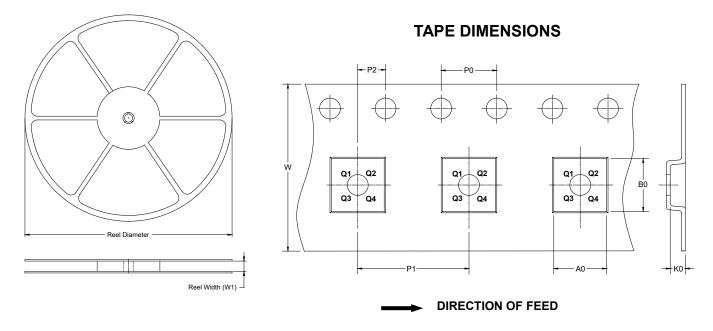

## PACKAGE/ORDERING INFORMATION

| MODEL      | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER    | PACKAGE<br>MARKING          | PACKING<br>OPTION   |

|------------|------------------------|-----------------------------------|-----------------------|-----------------------------|---------------------|

|            |                        | -40°C to +125°C                   | SGM5202-14XTQF24G/TR  | SGM008<br>XTQF24<br>XXXXX   | Tape and Reel, 3000 |

| TQFN-4×4-2 | IQFN-4×4-24L           | -40 C 10 +125 C                   | SGM5202-14XTQF24SG/TR | SGM008<br>XTQF24<br>XXXXX   | Tape and Reel, 500  |

| SGM5202-14 | TSSOP-24               | TSSOP-24 -40°C to +125°C          | SGM5202-14XTS24G/TR   | SGM520214<br>XTS24<br>XXXXX | Tape and Reel, 4000 |

|            |                        |                                   | SGM5202-14XTS24SG/TR  | SGM520214<br>XTS24<br>XXXXX | Tape and Reel, 500  |

### **MARKING INFORMATION**

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Trace Code

Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range (with Respect to AGND)

| 5 5 ( 1 -                             | /                  |

|---------------------------------------|--------------------|

| IN <sub>X</sub> , MUXOUT, ADCIN, REFP | 0.3V to VA + 0.3V  |

| COM, REF                              | -0.3V to 0.3V      |

| VA                                    | 0.3V to 6.5V       |

| Voltage Range (with Respect to DGNE   | ))                 |

| VBD                                   | -0.3V to 6.5V      |

| AGND                                  | -0.3V to 0.3V      |

| Digital Input Voltage                 | 0.3V to VBD + 0.3V |

| Digital Output Voltage                | 0.3V to VBD + 0.3V |

| Junction Temperature                  | +150°C             |

| Storage Temperature Range             | 65°C to +150°C     |

| Lead Temperature (Soldering, 10s)     | +260°C             |

| ESD Susceptibility                    |                    |

| HBM                                   | 4000V              |

| CDM                                   |                    |

|                                       |                    |

### **RECOMMENDED OPERATING CONDITIONS**

Analog Supply Voltage Range, V<sub>A</sub> Digital Supply Voltage Range, V<sub>BD</sub> Operating Temperature Range .....-40°C to +125°C

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

### ESD SENSITIVITY CAUTION

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

## Low-Power, 14-Bit, 1MSPS, 8 Channels Unipolar Input Analog-to-Digital Converter with Serial Interface

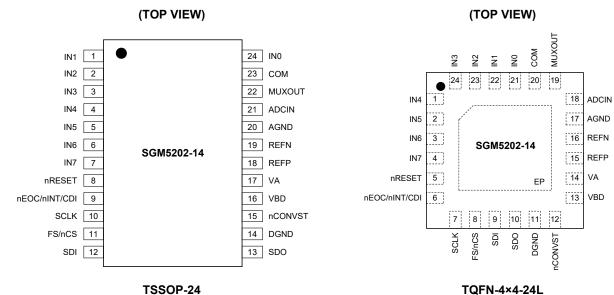

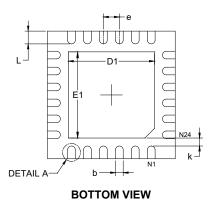

## **PIN CONFIGURATIONS**

**TSSOP-24**

# **PIN DESCRIPTION**

| F        | PIN              |                       |                     |                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|----------|------------------|-----------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TSSOP-24 | TQFN-<br>4×4-24L | NAME                  | TYPE <sup>(1)</sup> | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 1-7, 24  | 1-4, 21-24       | IN0 to IN7            | I                   | Channel 0 to Channel 7 Inputs to MUX (Multiplexer).                                                                                                                                                                                                                                                                                                                                                     |  |

| 8        | 5                | nRESET                | I                   | External Reset Pin. Active low.                                                                                                                                                                                                                                                                                                                                                                         |  |

| 9        | 6                | nEOC/<br>nINT/<br>CDI | 0/0/I               | Status Output Pin.<br>Used as end-of-conversion (nEOC) pin: active low (default) while<br>conversion is in progress. The nEOC polarity is programmable.<br>Used as an interrupt (nINT) pin: active low (default) after<br>end-of-conversion and returns high after FS/nCS goes low. The nINT pola<br>is programmable.<br>Used as a chain data input (CDI) pin: when it is operated in daisy-ch<br>mode. |  |

| 10       | 7                | SCLK                  | I                   | SPI Serial Clock Input.                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 11       | 8                | FS/nCS                | I                   | Frame Synchronization Signal for Host Controller or Chip Select Input for SPI.                                                                                                                                                                                                                                                                                                                          |  |

| 12       | 9                | SDI                   | I                   | SPI Serial Data Input.                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 13       | 10               | SDO                   | 0                   | SPI Serial Data Output.                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 14       | 11               | DGND                  | —                   | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 15       | 12               | nCONVST               | I                   | Conversion Start Pin. Freeze sample and hold, start conversion.                                                                                                                                                                                                                                                                                                                                         |  |

| 16       | 13               | VBD                   | —                   | Digital Power Supply.                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 17       | 14               | VA                    | —                   | Analog Power Supply.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 18       | 15               | REFP                  | I                   | External Positive Reference Input.                                                                                                                                                                                                                                                                                                                                                                      |  |

| 19       | 16               | REFN                  | —                   | External Negative Reference Input.                                                                                                                                                                                                                                                                                                                                                                      |  |

| 20       | 17               | AGND                  | —                   | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 21       | 18               | ADCIN                 | I                   | ADC Input.                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 22       | 19               | MUXOUT                | 0                   | Mux Output.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 23       | 20               | COM                   | I                   | Common ADC Input. Connect it to AGND usually.                                                                                                                                                                                                                                                                                                                                                           |  |

| _        | Exposed Pad      | EP                    | _                   | Exposed pad. Connect it to analog ground.                                                                                                                                                                                                                                                                                                                                                               |  |

NOTE: 1. I = Input, O = Output.

# **ELECTRICAL CHARACTERISTICS**

(V<sub>A</sub> = 2.7V, V<sub>BD</sub> = 2.7V, V<sub>REF</sub> = 2.5V, and f<sub>SAMPLE</sub> = 1MSPS, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted.)

| PARAMETER                                | SYMBOL               | CONDITIONS                                      | MIN        | TYP   | MAX                  | UNITS         |

|------------------------------------------|----------------------|-------------------------------------------------|------------|-------|----------------------|---------------|

| Analog Input                             |                      |                                                 |            |       |                      |               |

| Full-Scale Input Voltage <sup>(1)</sup>  |                      | IN <sub>X</sub> - COM, ADCIN - COM              | 0          |       | V <sub>REF</sub>     | V             |

|                                          |                      | IN <sub>x</sub> , ADCIN                         | AGND - 0.2 |       | V <sub>A</sub> + 0.2 |               |

| Absolute Input Voltage                   |                      | СОМ                                             | AGND - 0.2 |       | AGND + 0.2           | V             |

| Input Capacitance                        |                      | ADCIN                                           |            | 40    |                      | pF            |

| Input Leakage Current                    |                      | Unselected ADC input                            | -1         |       | 1                    | μA            |

| System Performance                       |                      |                                                 | II         |       | 1                    |               |

| Resolution                               |                      |                                                 |            | 14    |                      | Bits          |

| Integral Nonlinearity                    | INL                  |                                                 | -6         | ±2    | 6                    | LSB (2)       |

| Differential Nonlinearity                | DNL                  |                                                 |            | ±0.7  | 3                    | LSB (2)       |

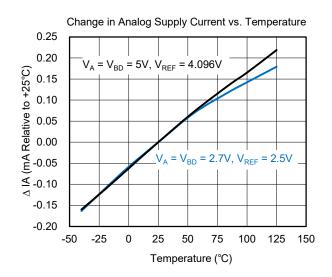

| Offset Error (3)                         | Eo                   |                                                 | -3.5       | ±0.2  | 3.5                  | mV            |

| Offset Error Drift                       |                      |                                                 |            | 2     |                      | PPM/°C        |

| Offset Error Matching                    |                      |                                                 |            | ±0.2  |                      | mV            |

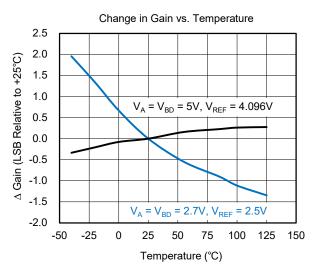

| Gain Error                               | E <sub>G</sub>       |                                                 |            | -0.08 |                      | %FSR          |

| Gain Error Drift                         |                      |                                                 |            | ±0.18 |                      | PPM/°C        |

| Gain Error Matching                      |                      |                                                 |            | 0.003 |                      | %FSR          |

| Transition Noise                         |                      |                                                 |            | 65    |                      | $\mu V_{RMS}$ |

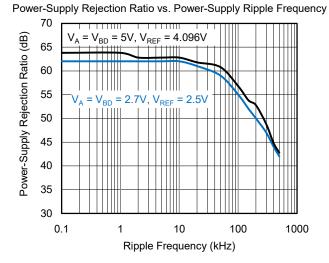

| Power Supply Rejection Ratio             | PSRR                 |                                                 |            | 70    |                      | dB            |

| Sampling Dynamics                        |                      |                                                 | r          |       |                      |               |

| Conversion Time                          | t <sub>CONV</sub>    |                                                 |            | 18    |                      | CCLK          |

| A                                        | t <sub>SAMPLE1</sub> | Manual-trigger mode                             | 3          |       |                      |               |

| Acquisition Time                         | t <sub>SAMPLE2</sub> | Auto-trigger mode                               |            | 3     |                      | CCLK          |

| Throughput Rate                          |                      |                                                 |            |       | 1                    | MSPS          |

| Dynamic Characteristics                  |                      |                                                 |            |       | l l                  |               |

| <b>T</b> ( ) (4)                         | TUD                  | V <sub>IN</sub> = 2.5V <sub>PP</sub> at 1kHz    |            | -86.7 | -73.3                | 15            |

| Total Harmonic Distortion <sup>(4)</sup> | THD                  | V <sub>IN</sub> = 2.5V <sub>PP</sub> at 10kHz   |            | -85.9 | -72.7                | dB            |

| Oinn al ta Nais a Datia                  |                      | V <sub>IN</sub> = 2.5V <sub>PP</sub> at 1kHz    | 73.3       | 81.1  |                      |               |

| Signal-to-Noise Ratio                    | SNR                  | V <sub>IN</sub> = 2.5V <sub>PP</sub> at 10kHz   | 74.1       | 80.6  |                      | dB            |

|                                          | 0.0.0                | V <sub>IN</sub> = 2.5V <sub>PP</sub> at 1kHz    | 71.3       | 80.0  |                      | 15            |

| Signal-to-Noise + Distortion             | SINAD                | V <sub>IN</sub> = 2.5V <sub>PP</sub> at 10kHz   | 71.9       | 79.4  |                      | dB            |

| Spurious-Free Dynamic                    | 0500                 | V <sub>IN</sub> = 2.5V <sub>PP</sub> at 1kHz    | 72         | 89.1  |                      |               |

| Range                                    | SFDR                 | V <sub>IN</sub> = 2.5V <sub>PP</sub> at 10kHz   | 71.1       | 89.1  |                      | dB            |

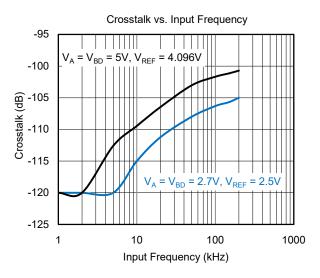

| Orecetelly                               |                      | V <sub>IN</sub> = 2.5V <sub>PP</sub> at 1kHz    |            | 120   |                      |               |

| Crosstalk                                |                      | V <sub>IN</sub> = 2.5V <sub>PP</sub> at 100kHz  |            | 106   |                      | dB            |

|                                          |                      | IN <sub>x</sub> - COM with MUXOUT tied to ADCIN |            | 17    |                      |               |

| -3dB Small-Signal Bandwidth              |                      | ADCIN - COM                                     |            | 30    |                      | MHz           |

# **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>A</sub> = 2.7V, V<sub>BD</sub> = 2.7V, V<sub>REF</sub> = 2.5V, and f<sub>SAMPLE</sub> = 1MSPS, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted.)

| PARAMETER SYMBO                   |                                 | SYMBOL          | CONDITIONS                                                                                       | MIN                   | TYP            | MAX                   | UNITS |

|-----------------------------------|---------------------------------|-----------------|--------------------------------------------------------------------------------------------------|-----------------------|----------------|-----------------------|-------|

| Clock                             |                                 |                 |                                                                                                  | I                     |                |                       |       |

| Internal Con<br>Frequency (7      | version Clock                   |                 |                                                                                                  | 17.3                  | 21             | 25.1                  | MHz   |

|                                   |                                 |                 | Used as I/O clock only                                                                           |                       |                | 42                    | MHz   |

| SCLK Exterr                       | nal Serial Clock <sup>(8)</sup> |                 | Used as both I/O clock and conversion<br>clock                                                   | 1                     |                | 42                    | MHz   |

| External Vo                       | Itage Reference In              | put             |                                                                                                  |                       |                |                       |       |

| Input                             | (REF+) - (REF-)                 |                 |                                                                                                  | 1.2                   |                | 2.525                 |       |

| Reference<br>Range <sup>(5)</sup> | (REF-) - AGND                   | $V_{REF}$       |                                                                                                  | -0.1                  |                | 0.1                   | V     |

| Resistance <sup>(</sup>           | 6)                              |                 | Reference input                                                                                  |                       | 50             |                       | kΩ    |

| Digital Inpu                      | t/Output                        |                 |                                                                                                  | I                     |                |                       |       |

| Logic Family                      | 1                               |                 |                                                                                                  |                       | CMOS           |                       |       |

| High-Level I                      | nput Voltage                    | VIH             | 2.7V < V <sub>BD</sub> < V <sub>A</sub>                                                          | $0.8 \times V_{BD}$   |                | V <sub>BD</sub> + 0.3 | V     |

| Low-Level Ir                      | nput Voltage                    | VIL             | 2.7V < V <sub>BD</sub> < V <sub>A</sub>                                                          | -0.3                  |                | 0.1 × V <sub>BD</sub> | V     |

| Input Curren                      | t                               | I <sub>I</sub>  | V <sub>IN</sub> = V <sub>BD</sub> or DGND                                                        | -1                    |                | 1                     | μA    |

| Input Capaci                      | itance                          | Cı              |                                                                                                  |                       | 3              |                       | pF    |

| High-Level C                      | Output Voltage                  | V <sub>OH</sub> | $V_A \ge V_{BD} \ge 2.7V$ , $I_O = 1mA$                                                          | V <sub>BD</sub> - 0.4 |                | V <sub>BD</sub>       | V     |

| Low-Level O                       | utput Voltage                   | V <sub>OL</sub> | $V_A \ge V_{BD} \ge 2.7V$ , $I_O = -1mA$                                                         | 0                     |                | 0.4                   | V     |

| SDO Pin Ca                        | pacitance                       | Co              | 3-state high impedance state                                                                     |                       | 3              |                       | pF    |

| Load Capac                        | itance                          | CL              |                                                                                                  |                       |                | 20                    | pF    |

| Data Format                       | t                               |                 |                                                                                                  |                       | Straight binar | у                     |       |

| Power Supp                        | bly Requirements                |                 |                                                                                                  | I.                    |                |                       | I.    |

| Analog Supp                       | oly Voltage <sup>(5)</sup>      | V <sub>A</sub>  |                                                                                                  | 2.7                   |                | 3.6                   | V     |

| Digital I/O S                     | upply Voltage                   | V <sub>BD</sub> |                                                                                                  | 2.7                   |                | V <sub>A</sub> + 0.2  | V     |

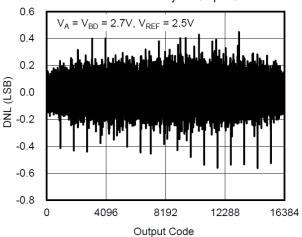

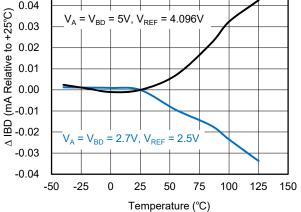

|                                   |                                 |                 | f <sub>SAMPLE</sub> = 1MSPS                                                                      |                       | 5.9            | 8.5                   |       |

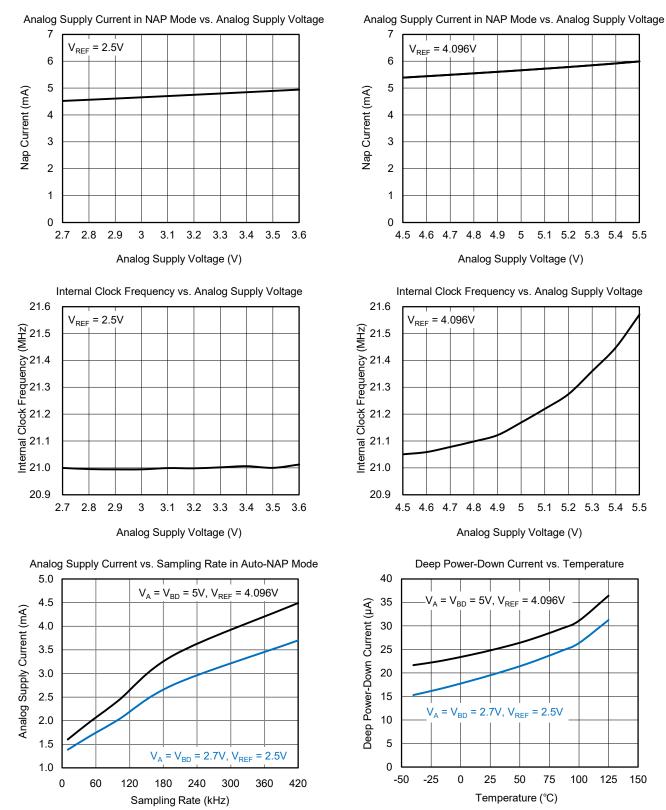

| Analog Supply Current             |                                 |                 | f <sub>SAMPLE</sub> = 500kSPS in Auto-Nap mode                                                   |                       | 4.6            | 7                     | mA    |

|                                   |                                 | IA              | Nap mode, SCLK = V <sub>BD</sub> or DGND                                                         |                       | 2.4            | 4                     | mA    |

|                                   |                                 |                 | Deep PD mode, SCLK = V <sub>BD</sub> or DGND                                                     |                       | 20             | 48                    | μA    |

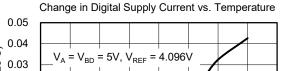

| Digital I/O Supply Current        |                                 |                 | f <sub>SAMPLE</sub> = 1MSPS                                                                      |                       | 1.5            | 2.8                   |       |

|                                   |                                 | I <sub>BD</sub> | f <sub>SAMPLE</sub> = 500kSPS in Auto-Nap mode                                                   |                       | 1.1            | 2.2                   | mA    |

|                                   |                                 |                 | $V_A$ = 2.7V, $V_{BD}$ = 2.7V, $f_{SAMPLE}$ = 1MSPS                                              |                       | 20             | 30.6                  |       |

| Power Dissi                       | pation                          |                 | V <sub>A</sub> = 2.7V, V <sub>BD</sub> = 2.7V, f <sub>SAMPLE</sub> = 500kSPS<br>in Auto-Nap mode |                       | 15.4           |                       | mW    |

#### NOTES:

1. Ideal input range, do not consider gain error or offset error.

2. LSB = Least Significant Bit.

3. The measurement is performed relative to an ideal full-scale input (IN<sub>X</sub> - COM) of 2.5V at  $V_A$  = 2.7V.

4. Accumulate the first nine harmonics of the input frequency.

5. The chip operates with V<sub>A</sub> from 2.7V to 5.5V and V<sub>REF</sub> from 1.2V to V<sub>A</sub> (maximum V<sub>REF</sub>  $\leq$  4.2V). However, when V<sub>A</sub> is between 3.6V and 4.5V, the chip may not meet the specifications shown in the Electrical Characteristics table.

6. Vary ±30%.

7. Sampling rate is up to 1MSPS in auto-trigger mode, while the internal conversion clock frequency is 21MHz.

8. Guaranteed by design and laboratory test, not tested in production.

# ELECTRICAL CHARACTERISTICS (continued)

(V<sub>A</sub> = 5V, V<sub>BD</sub> = 2.7V to 5V, V<sub>REF</sub> = 4.096V, and  $f_{SAMPLE}$  = 1MSPS, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted.)

| PARAMETER                                | SYMBOL               | CONDITIONS                                       | MIN        | ТҮР    | MAX                  | UNITS         |  |

|------------------------------------------|----------------------|--------------------------------------------------|------------|--------|----------------------|---------------|--|

| Analog Input                             |                      |                                                  |            |        |                      |               |  |

| Full-Scale Input Voltage (1)             |                      | IN <sub>x</sub> - COM, ADCIN - COM               | 0          |        | V <sub>REF</sub>     | V             |  |

|                                          |                      | IN <sub>x</sub> , ADCIN                          | AGND - 0.2 |        | V <sub>A</sub> + 0.2 |               |  |

| Absolute Input Voltage                   |                      | СОМ                                              | AGND - 0.2 |        | AGND + 0.2           | V             |  |

| Input Capacitance                        |                      | ADCIN                                            |            | 40     |                      | pF            |  |

| Input Leakage Current                    |                      | Unselected ADC input                             | -1         |        | 1                    | μA            |  |

| System Performance                       | 1                    |                                                  | II         |        |                      |               |  |

| Resolution                               |                      |                                                  |            | 14     |                      | Bits          |  |

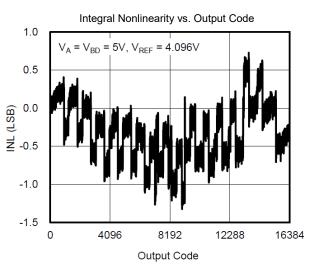

| Integral Nonlinearity                    | INL                  |                                                  | -6         | ±2     | 6                    | LSB (2)       |  |

| Differential Nonlinearity                | DNL                  |                                                  |            | ±0.7   | 2.5                  | LSB (2)       |  |

| Offset Error <sup>(3)</sup>              | Eo                   |                                                  | -4.3       | ±0.8   | 4.3                  | mV            |  |

| Offset Error Drift                       |                      |                                                  |            | ±1     |                      | PPM/°C        |  |

| Offset Error Matching                    |                      |                                                  |            | ±0.5   |                      | mV            |  |

| Gain Error                               | E <sub>G</sub>       |                                                  |            | -0.08  |                      | %FSR          |  |

| Gain Error Drift                         |                      |                                                  |            | ±0.18  |                      | PPM/°C        |  |

| Gain Error Matching                      |                      |                                                  |            | ±0.005 |                      | %FSR          |  |

| Transition Noise                         |                      |                                                  |            | 60     |                      | $\mu V_{RMS}$ |  |

| Power Supply Rejection Ratio             | PSRR                 |                                                  |            | 73     |                      | dB            |  |

| Sampling Dynamics                        |                      | -                                                | 1 1        |        |                      |               |  |

| Conversion Time                          | t <sub>CONV</sub>    |                                                  |            | 18     |                      | CCLK          |  |

| A                                        | t <sub>SAMPLE1</sub> | Manual-trigger mode                              | 3          |        |                      | 00114         |  |

| Acquisition Time                         | t <sub>SAMPLE2</sub> | Auto-trigger mode                                |            | 3      |                      | CCLK          |  |

| Throughput Rate                          |                      |                                                  |            |        | 1                    | MSPS          |  |

| Dynamic Characteristics                  | •                    | •                                                |            |        |                      |               |  |

| Total Harmonic Distortion <sup>(4)</sup> | TUD                  | $V_{IN}$ = 4.096 $V_{PP}$ at 1kHz                |            | -87.9  | -72.3                |               |  |

| Total Harmonic Distortion                | THD                  | V <sub>IN</sub> = 4.096V <sub>PP</sub> at 10kHz  |            | -85.7  | -72                  | dB            |  |

| Circulto Noise Datia                     |                      | V <sub>IN</sub> = 4.096V <sub>PP</sub> at 1kHz   | 74.7       | 81.5   |                      |               |  |

| Signal-to-Noise Ratio                    | SNR                  | V <sub>IN</sub> = 4.096V <sub>PP</sub> at 10kHz  | 74.6       | 81.8   |                      | dB            |  |

| Circulto Noise + Distortion              | CINIAD               | V <sub>IN</sub> = 4.096V <sub>PP</sub> at 1kHz   | 71.8       | 80.5   |                      | -ID           |  |

| Signal-to-Noise + Distortion             | SINAD                | V <sub>IN</sub> = 4.096V <sub>PP</sub> at 10kHz  | 71.9       | 80.2   |                      | dB            |  |

| Spurious-Free Dynamic                    |                      | V <sub>IN</sub> = 4.096V <sub>PP</sub> at 1kHz   | 70.9       | 90.4   |                      | ٩D            |  |

| Range                                    | SFDR                 | V <sub>IN</sub> = 4.096V <sub>PP</sub> at 10kHz  | 70.6       | 89.1   |                      | dB            |  |

| Croastelly                               |                      | V <sub>IN</sub> = 4.096V <sub>PP</sub> at 1kHz   |            | 120    |                      | D۲            |  |

| Crosstalk                                |                      | V <sub>IN</sub> = 4.096V <sub>PP</sub> at 100kHz |            | 101    |                      | dB            |  |

| 2dB Small Signal Bandwidth               |                      | IN <sub>x</sub> - COM with MUXOUT tied to ADCIN  |            | 22     |                      | N411-         |  |

| -3dB Small-Signal Bandwidth              |                      | ADCIN - COM                                      |            | 40     |                      | MHz           |  |

# ELECTRICAL CHARACTERISTICS (continued)

(V<sub>A</sub> = 5V, V<sub>BD</sub> = 2.7V to 5V, V<sub>REF</sub> = 4.096V, and f<sub>SAMPLE</sub> = 1MSPS, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted.)

| PARAMETER SYMBOL                  |                                 | SYMBOL          | CONDITIONS                                                                                    | MIN                   | TYP            | MAX                   | UNITS |

|-----------------------------------|---------------------------------|-----------------|-----------------------------------------------------------------------------------------------|-----------------------|----------------|-----------------------|-------|

| Clock                             |                                 |                 |                                                                                               |                       |                |                       |       |

| Internal Con<br>Frequency (7      | version Clock                   |                 |                                                                                               | 17.3                  | 21.2           | 25.7                  | MHz   |

|                                   |                                 |                 | Used as I/O clock only                                                                        |                       |                | 50                    |       |

| SCLK Exterr                       | nal Serial Clock <sup>(8)</sup> |                 | Used as both I/O clock and conversion clock                                                   | 1                     |                | 42                    | MHz   |

| External Vo                       | Itage Reference Ir              | nput            |                                                                                               |                       |                |                       |       |

| Input                             | (REF+) - (REF-)                 | M               |                                                                                               | 1.2                   | 4.096          | 4.2                   | Ň     |

| Reference<br>Range <sup>(5)</sup> | (REF-) - AGND                   | $V_{REF}$       |                                                                                               | -0.1                  |                | 0.1                   | V     |

| Resistance <sup>(</sup>           | 6)                              |                 | Reference input                                                                               |                       | 50             |                       | kΩ    |

| Digital Inpu                      | t/Output                        |                 |                                                                                               |                       |                |                       |       |

| Logic Family                      | 1                               |                 |                                                                                               |                       | CMOS           | 1                     |       |

| High-Level Ir                     | nput Voltage                    | VIH             | 2.7V < V <sub>BD</sub> < V <sub>A</sub>                                                       | $0.8 \times V_{BD}$   |                | V <sub>BD</sub> + 0.3 | V     |

| Low-Level In                      | put Voltage                     | VIL             | 2.7V < V <sub>BD</sub> < V <sub>A</sub>                                                       | -0.3                  |                | 0.1 × V <sub>BD</sub> | V     |

| Input Curren                      | t                               | I,              | V <sub>IN</sub> = V <sub>BD</sub> or DGND                                                     | -1                    |                | 1                     | μA    |

| Input Capaci                      | itance                          | Cı              |                                                                                               |                       | 3              |                       | pF    |

| High-Level C                      | Output Voltage                  | V <sub>OH</sub> | $V_A \ge V_{BD} \ge 2.7V$ , $I_O = 1mA$                                                       | V <sub>BD</sub> - 0.3 |                | V <sub>BD</sub>       | V     |

| Low-Level O                       | utput Voltage                   | V <sub>OL</sub> | $V_A \ge V_{BD} \ge 2.7V$ , $I_O = -1mA$                                                      | 0                     |                | 0.3                   | V     |

| SDO Pin Ca                        | pacitance                       | Co              | HIZ state                                                                                     |                       | 3              |                       | pF    |

| Load Capaci                       | itance                          | CL              |                                                                                               |                       |                | 20                    | pF    |

| Data Format                       |                                 |                 |                                                                                               | 1                     | Straight binar | y                     |       |

| Power Supp                        | bly Requirements                |                 |                                                                                               |                       |                |                       |       |

| Analog Supp                       | bly Voltage <sup>(5)</sup>      | V <sub>A</sub>  |                                                                                               | 4.5                   | 5              | 5.5                   | V     |

| Digital I/O Su                    | upply Voltage                   | V <sub>BD</sub> |                                                                                               | 2.7                   |                | V <sub>A</sub> + 0.2  | V     |

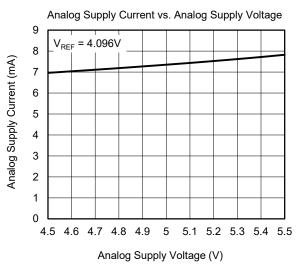

|                                   |                                 |                 | f <sub>SAMPLE</sub> = 1MSPS                                                                   |                       | 7.5            | 11                    |       |

| Analog Supply Current             |                                 |                 | f <sub>SAMPLE</sub> = 500kSPS in Auto-Nap mode                                                |                       | 5.8            | 8                     | mA    |

|                                   |                                 | I <sub>A</sub>  | Nap mode, SCLK = V <sub>BD</sub> or DGND                                                      |                       | 2.6            | 4                     | mA    |

|                                   |                                 |                 | Deep PD mode, SCLK = V <sub>BD</sub> or DGND                                                  |                       | 25.2           | 55                    | μA    |

| Digital I/O Supply Current        |                                 |                 | f <sub>SAMPLE</sub> = 1MSPS                                                                   |                       | 3.1            | 5.5                   |       |

|                                   |                                 | I <sub>BD</sub> | f <sub>SAMPLE</sub> = 500kSPS in Auto-Nap mode                                                |                       | 2.3            | 4                     | mA    |

|                                   |                                 |                 | $V_A = 5V, V_{BD} = 5V, f_{SAMPLE} = 1MSPS$                                                   |                       | 28.6           | 44.6                  |       |

| Power Dissip                      | pation                          |                 | V <sub>A</sub> = 5V, V <sub>BD</sub> = 5 V, f <sub>SAMPLE</sub> = 500kSPS in<br>Auto-Nap mode |                       | 21.9           |                       | mW    |

#### NOTES:

1. Ideal input range, do not consider gain error or offset error.

2. LSB = Least Significant Bit.

3. The measurement is performed relative to an ideal full-scale input (IN<sub>X</sub> - COM) of 4.096V at  $V_A$  = 5V.

4. Accumulate the first nine harmonics of the input frequency.

5. The chip operates with V<sub>A</sub> from 2.7V to 5.5V and V<sub>REF</sub> from 1.2V to V<sub>A</sub> (maximum V<sub>REF</sub>  $\leq$  4.2V). However, when V<sub>A</sub> is between 3.6V and 4.5V, the chip may not meet the specifications shown in the Electrical Characteristics table.

6. Vary ±30%.

7. Sampling rate is up to 1MSPS in auto-trigger mode, while the internal conversion clock frequency is 21MHz.

8. Guaranteed by design and laboratory test, not tested in production.

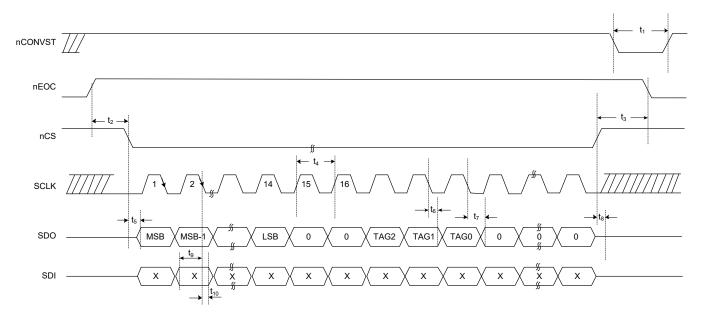

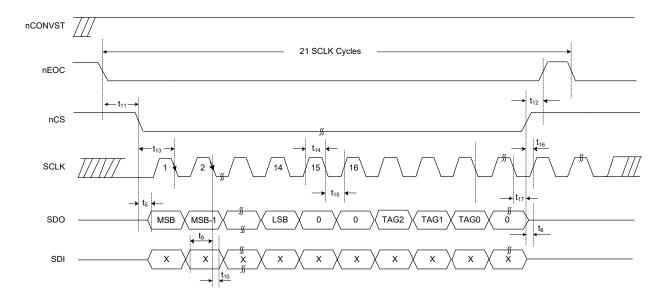

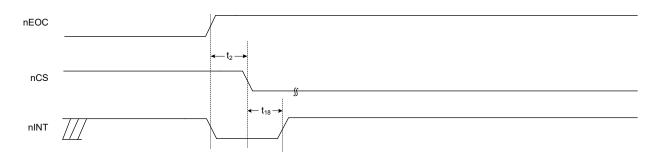

## TIMING REQUIREMENTS

(V\_A = V\_{BD} = 2.7V, T\_A = -40^{\circ}C to +125°C, unless otherwise noted.)  $^{(1)\,(2)}$

| PARAMETER                                                          | SYMBOL                         | CONDITIONS                                          | MIN  | TYP | MAX                                  | UNITS |

|--------------------------------------------------------------------|--------------------------------|-----------------------------------------------------|------|-----|--------------------------------------|-------|

|                                                                    | £                              | External, f <sub>CCLK</sub> = 1/2 f <sub>SCLK</sub> | 0.5  |     | 21                                   | N411- |

| Frequency, Conversion Clock, CCLK                                  | f <sub>CCLK</sub>              | Internal                                            | 17.3 | 21  | 25.1                                 | MHz   |

| Pulse Duration, nCONVST Low                                        | t <sub>1</sub>                 |                                                     | 40   |     |                                      | ns    |

| nCS Hold Time with Respect to nEOC <sup>(3)</sup>                  | t <sub>2</sub>                 | Read while sampling                                 | 20   |     |                                      | ns    |

| Setup Time, Rising Edge of nCS to EOS                              | t <sub>3</sub>                 | Read while sampling                                 | 20   |     |                                      | ns    |

|                                                                    |                                | I/O clock only                                      | 23.8 |     |                                      |       |

|                                                                    |                                | I/O and conversion clocks                           | 23.8 |     | 1000                                 |       |

| Cycle Time, SCLK                                                   | t <sub>4</sub>                 | I/O clock, daisy-chain mode                         | 23.8 |     |                                      | ns    |

|                                                                    |                                | I/O and conversion clocks, daisy-chain mode         | 23.8 |     | 1000                                 |       |

| Delay Time, Falling Edge of nCS to SDO Valid,<br>SDO MSB Output    | t <sub>5</sub>                 | C <sub>LOAD</sub> = 10pF                            |      |     | 13                                   | ns    |

| Delay Time, Falling Edge of SCLK to SDO Invalid                    | t <sub>6</sub>                 | C <sub>LOAD</sub> = 10pF                            | 7.5  |     |                                      | ns    |

| Delay Time, Falling Edge of SCLK to SDO Valid                      | t <sub>7</sub>                 | C <sub>LOAD</sub> = 10pF                            |      |     | 21                                   | ns    |

| Delay Time, Rising Edge of nCS to SDO 3-State                      | t <sub>8</sub>                 | C <sub>LOAD</sub> = 10pF                            |      |     | 8                                    | ns    |

| Setup Time, SDI to Falling Edge of SCLK                            | t <sub>9</sub>                 |                                                     | 8    |     |                                      | ns    |

| Hold Time, SDI to Falling Edge of SCLK                             | t <sub>10</sub>                |                                                     | 4    |     |                                      | ns    |

| nCS Hold Time with Respect to EOS                                  | t <sub>11</sub>                | Read while converting                               | 25   |     |                                      | ns    |

| Setup Time, Rising Edge of nCS to nEOC <sup>(3)</sup>              | t <sub>12</sub>                | Read while converting                               | 1    |     |                                      | CCLK  |

| Setup Time, Falling Edge of nCS to First Falling<br>Edge of SCLK   | t <sub>13</sub>                |                                                     | 5    |     |                                      | ns    |

| Pulse Duration, SCLK Low                                           | t <sub>14</sub>                |                                                     | 8    |     | t <sub>SCLK</sub> - t <sub>WH2</sub> | ns    |

| Pulse Duration, SCLK High                                          | t <sub>15</sub>                |                                                     | 8    |     | $t_{SCLK}$ - $t_{WL2}$               | ns    |

| Hold Time, Last Falling Edge of SCLK before<br>Rising Edge of nCS  | t <sub>16</sub>                |                                                     | 2    |     |                                      | ns    |

| Setup Time, Last Falling Edge of SCLK before<br>Rising Edge of nCS | t <sub>17</sub>                |                                                     | 15   |     |                                      | ns    |

| Delay Time, Falling Edge of nCS to Deactivation of nINT            | t <sub>18</sub>                | C <sub>LOAD</sub> = 10pF                            |      |     | 40                                   | ns    |

| Setup Time, Rising Edge of SCLK to Rising Edge<br>of nCS           | t <sub>19</sub> <sup>(4)</sup> |                                                     | 10   |     |                                      | ns    |

| Hold Time, Rising Edge of SCLK to Rising Edge of<br>nCS            | $t_{20}^{(4)}$                 |                                                     | 2    |     |                                      | ns    |

#### NOTES:

1. All input signals are specified with rising up time which is 1.5ns and falling down time which is 1.5ns (10% to 90% of V<sub>BD</sub>), and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

2. Refer to the timing diagrams.

3. The EOS is the end of sampling. The nEOC is the end of conversion. They are the inverse of each other.

4. When sending 4-bit or 16-bit commands, this applies to the 5<sup>th</sup> or 17<sup>th</sup> rising SCLK.

# **TIMING REQUIREMENTS (continued)**

$(V_A = V_{BD} = 5V, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted.) <sup>(1) (2)</sup>

| PARAMETER                                                          | SYMBOL                         | CONDITIONS                                          | MIN  | TYP  | MAX                                         | UNITS |

|--------------------------------------------------------------------|--------------------------------|-----------------------------------------------------|------|------|---------------------------------------------|-------|

|                                                                    | £                              | External, f <sub>CCLK</sub> = 1/2 f <sub>SCLK</sub> | 0.5  |      | 21                                          | MHz   |

| Frequency, Conversion Clock, CCLK                                  | f <sub>CCLK</sub>              | Internal                                            | 17.3 | 21.2 | 25.7                                        | IVITZ |

| Pulse Duration, nCONVST Low                                        | t <sub>1</sub>                 |                                                     | 40   |      |                                             | ns    |

| nCS Hold Time with Respect to nEOC <sup>(3)</sup>                  | t <sub>2</sub>                 | Read while sampling                                 | 20   |      |                                             | ns    |

| Setup Time, Rising Edge of nCS to EOS                              | t <sub>3</sub>                 | Read while sampling                                 | 20   |      |                                             | ns    |

|                                                                    |                                | I/O clock only                                      | 20   |      |                                             |       |

|                                                                    |                                | I/O and conversion clocks                           | 23.8 |      | 1000                                        |       |

| Cycle Time, SCLK                                                   | t <sub>4</sub>                 | I/O clock, daisy-chain mode                         | 20   |      |                                             | ns    |

|                                                                    |                                | I/O and conversion clocks, daisy-chain mode         | 23.8 |      | 1000                                        |       |

| Delay Time, Falling Edge of nCS to SDO Valid,<br>SDO MSB Output    | t <sub>5</sub>                 | C <sub>LOAD</sub> = 10pF                            |      |      | 9                                           | ns    |

| Delay Time, Falling Edge of SCLK to SDO Invalid                    | t <sub>6</sub>                 | C <sub>LOAD</sub> = 10pF                            | 2    |      |                                             | ns    |

| Delay Time, Falling Edge of SCLK to SDO Valid                      | t <sub>7</sub>                 | C <sub>LOAD</sub> = 10pF                            |      |      | 12                                          | ns    |

| Delay Time, Rising Edge of nCS to SDO 3-State                      | t <sub>8</sub>                 | C <sub>LOAD</sub> = 10pF                            |      |      | 6                                           | ns    |

| Setup Time, SDI to Falling Edge of SCLK                            | t <sub>9</sub>                 |                                                     | 8    |      |                                             | ns    |

| Hold Time, SDI to Falling Edge of SCLK                             | t <sub>10</sub>                |                                                     | 4    |      |                                             | ns    |

| nCS Hold Time with Respect to EOS                                  | t <sub>11</sub>                | Read while converting                               | 20   |      |                                             | ns    |

| Setup Time, Rising Edge of nCS to nEOC <sup>(3)</sup>              | t <sub>12</sub>                | Read while converting                               | 1    |      |                                             | CCLK  |

| Setup Time, Falling Edge of nCS to First Falling<br>Edge of SCLK   | t <sub>13</sub>                |                                                     | 5    |      |                                             | ns    |

| Pulse Duration, SCLK Low                                           | t <sub>14</sub>                |                                                     | 8    |      | $t_{\text{SCLK}} \text{ - } t_{\text{WH2}}$ | ns    |

| Pulse Duration, SCLK High                                          | t <sub>15</sub>                |                                                     | 8    |      | $t_{\rm SCLK}$ - $t_{\rm WL2}$              | ns    |

| Hold Time, Last Falling Edge of SCLK before<br>Rising Edge of nCS  | t <sub>16</sub>                |                                                     | 2    |      |                                             | ns    |

| Setup Time, Last Falling Edge of SCLK before<br>Rising Edge of nCS | t <sub>17</sub>                |                                                     | 10   |      |                                             | ns    |

| Delay Time, Falling Edge of nCS to Deactivation of nINT            | t <sub>18</sub>                | C <sub>LOAD</sub> = 10pF                            |      |      | 20                                          | ns    |

| Setup Time, Rising Edge of SCLK to Rising Edge<br>of nCS           | t <sub>19</sub> <sup>(4)</sup> |                                                     | 10   |      |                                             | ns    |

| Hold Time, Rising Edge of SCLK to Rising Edge of<br>nCS            | $t_{20}^{(4)}$                 |                                                     | 2    |      |                                             | ns    |

#### NOTES:

1. All input signals are specified with rising up time which is 1.5ns and falling down time which is1.5ns (10% to 90% of  $V_{BD}$ ), and timed from a voltage level of ( $V_{IL} + V_{IH}$ )/2.

2. Refer to the timing diagrams.

3. The EOS is the end of sampling. The nEOC is the end of conversion. They are the inverse of each other.

4. When sending 4-bit or 16-bit commands, this applies to the 5<sup>th</sup> or 17<sup>th</sup> rising SCLK.

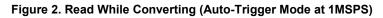

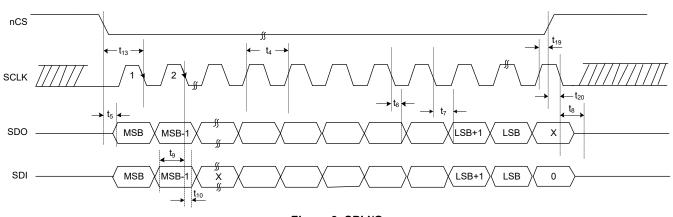

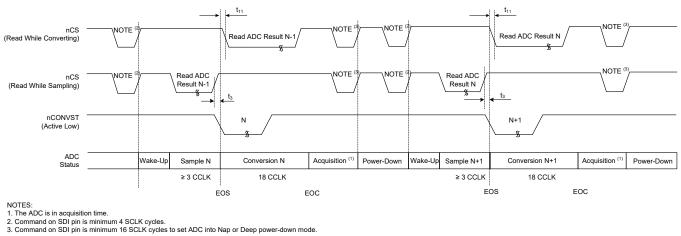

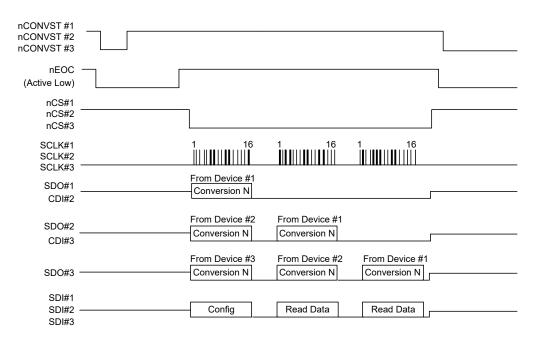

### TIMING DIAGRAM

Figure 1. Read While Sampling (Manual-Trigger Mode)

# **TIMING DIAGRAM (continued)**

Figure 3. SPI I/O

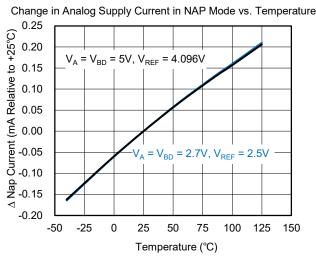

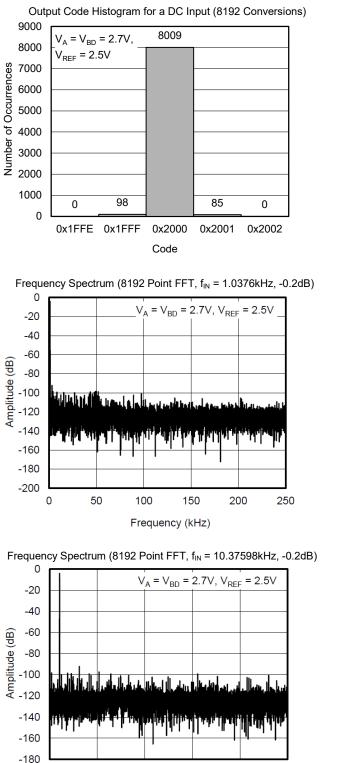

## **TYPICAL PERFORMANCE CHARACTERISTICS: DC PERFORMANCE**

$T_A = +25^{\circ}C, V_{REF} (REF+ - REF-) = 4.096V \text{ when } V_A = V_{BD} = 5V \text{ or } V_{REF} (REF+ - REF-) = 2.5V \text{ when } V_A = V_{BD} = 2.7V, f_{SCLK} = 21MHz, and f_{SAMPLE} = 500kSPS, unless otherwise noted.$

SG Micro Corp

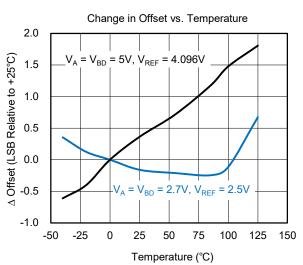

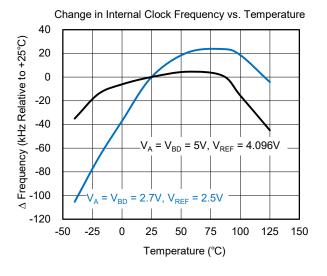

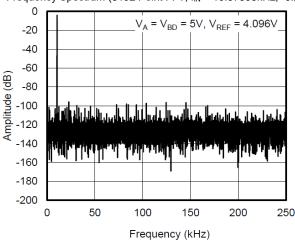

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25^{\circ}C, V_{REF} (REF+ - REF-) = 4.096V \text{ when } V_A = V_{BD} = 5V \text{ or } V_{REF} (REF+ - REF-) = 2.5V \text{ when } V_A = V_{BD} = 2.7V, f_{SCLK} = 21MHz, and f_{SAMPLE} = 500kSPS, unless otherwise noted.$

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25^{\circ}C, V_{REF} (REF+ - REF-) = 4.096V \text{ when } V_A = V_{BD} = 5V \text{ or } V_{REF} (REF+ - REF-) = 2.5V \text{ when } V_A = V_{BD} = 2.7V, f_{SCLK} = 21MHz, and f_{SAMPLE} = 500kSPS, unless otherwise noted.$

SG Micro Corp

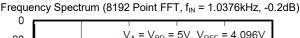

## **TYPICAL PERFORMANCE CHARACTERISTICS: AC PERFORMANCE**

$T_A = +25^{\circ}C, V_{REF} (REF+ - REF-) = 4.096V \text{ when } V_A = V_{BD} = 5V \text{ or } V_{REF} (REF+ - REF-) = 2.5V \text{ when } V_A = V_{BD} = 2.7V, f_{SCLK} = 21MHz, and f_{SAMPLE} = 500kSPS, unless otherwise noted.$

SG Micro Corp

0

50

100

200

250

150

Frequency (kHz)

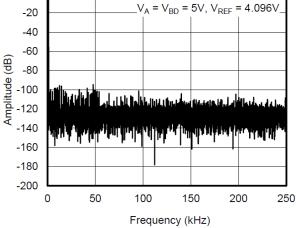

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25^{\circ}C$ ,  $V_{REF}$  (REF+ - REF-) = 4.096V when  $V_A = V_{BD} = 5V$  or  $V_{REF}$  (REF+ - REF-) = 2.5V when  $V_A = V_{BD} = 2.7V$ ,  $f_{SCLK} = 21MHz$ , and  $f_{SAMPLE} = 500kSPS$ , unless otherwise noted.

SG Micro Corp

### **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25^{\circ}C$ ,  $V_{REF}$  (REF+ - REF-) = 4.096V when  $V_A = V_{BD} = 5V$  or  $V_{REF}$  (REF+ - REF-) = 2.5V when  $V_A = V_{BD} = 2.7V$ ,  $f_{SCLK} = 21MHz$ , and  $f_{SAMPLE} = 500kSPS$ , unless otherwise noted.

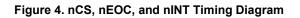

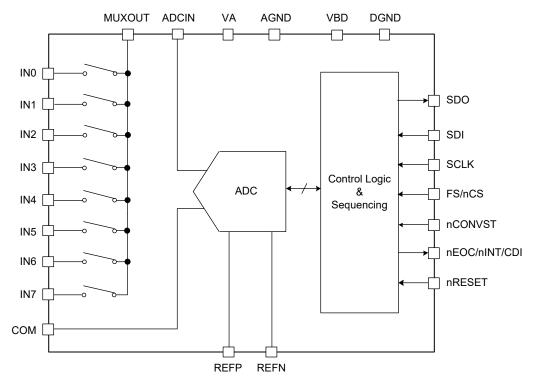

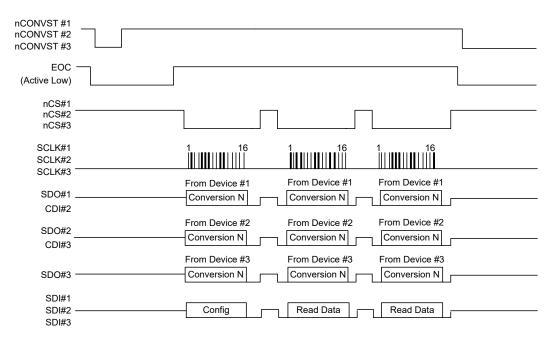

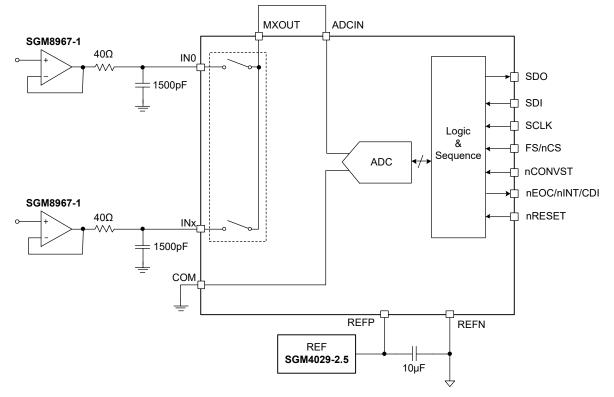

# FUNCTIONAL BLOCK DIAGRAM

Figure 5. Block Diagram

## **DETAILED DESCRIPTION**

#### Overview

The SGM5202-14 is a low-power, high-speed, successive approximation register (SAR) analog-to-digital converter (ADC). It needs to work with an external voltage reference.

The SGM5202-14 has 8 single-ended input channels. All inputs share the same common pin (COM pin).

The SGM5202-14 can be driven by either an internal clock, or an external clock (SCLK).

The SGM5202-14 has two working modes, manual channel select mode and auto channel select mode.

### **Signal Conditioning**

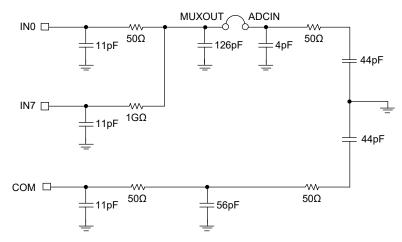

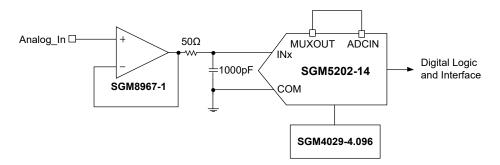

For the input signal pre-conditioning, it is recommended to add an amplifier or a PGA (Programmable Gain Amplifier) between the MUXOUT pin and ADCIN pin.

### **Analog Input**

The input signal applied to INx and COM must be limited to the range listed in the Electrical Characteristics table.

The SGM5202-14 is a capacitor array SAR ADC. During the sampling period, there is an input current flowing into the ADC. The peak input current depends on the sampling rate, reference voltage, input voltage and signal source impedance.

A driver amplifier is usually recommended to buffer the signal source. It makes the analog input source to charge the equivalent input capacitor (48pF) to a 14-bit accuracy level in the acquisition time (120ns). When the input capacitor is fully charged, no further current flows. An equivalent input circuit is shown in Figure 6.

#### **Driver Amplifier Choice**

In a demo circuit, the SGM8967-1 is used for the source-follower (unity-gain) configuration, which is shown in Figure 7 with the recommended RC filter values. Low-bandwidth input signals with low-pass filters can be used to minimize noise.

NOTE: IN0 is assumed to be on, and IN7 is assumed to be off.

#### Figure 6. Equivalent Input Circuit

### **Device Functional Modes**

#### Reference

The SGM5202-14 must be operated with an external voltage reference. The available range is 1.2V to 4.2V. It is recommended to place a  $10\mu$ F decoupling capacitor between the reference output and the ADC REF input pin.

#### **Converter Operation**

The ADC conversion of SGM5202-14 is driven by the conversion clock (CCLK) source.

The CCLK source can be selected by software either from an internal oscillator or an external clock (SCLK).

When the CCLK is from the internal oscillator, its minimum frequency is 17.3MHz. The minimum sampling time is 3 CCLK cycles. The minimum conversion time is 18 CCLK cycles.

When the CCLK is from the external clock (SCLK), its maximum frequency is 42MHz. The frequency of SCLK is divided by a factor of two, because the CCLK is toggled on

the rising edge of SCLK. In manual-trigger mode, the start of a conversion is triggered by a specific rising edge of SCLK. It will take a minimum 20ns to set up between the falling edge of nCONVST and the rising edge of SCLK. The minimum conversion time is 18 CCLK cycles.

When the SCLK is used to drive ADC conversion, it must meet the minimum high time and low time requirements. The SCLK must meet the minimum rise time, fall time and low jitter to get the best converter performance.

#### Manual Channel Select Mode

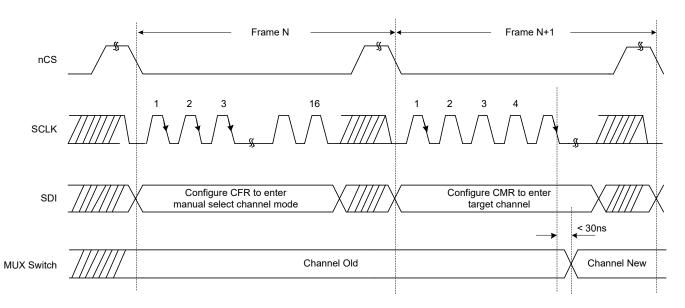

To enter the manual channel select mode, it needs to take two steps. The first step is to set the Configuration register (CFR) to enable the manual channel select mode. The second step is to set the target channel number by configuring the Command register (CMR). Figure 8 shows a demo of the channel switching timing sequence in manual channel select mode.

#### Figure 8. Manual Channel Select Mode Timing

## **DETAILED DESCRIPTION (continued)**

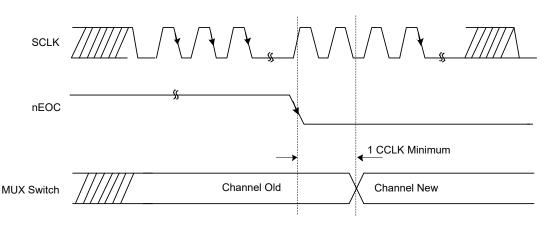

#### Auto Channel Select Mode

If the chip is configured to work in auto channel select mode, the chip scans all channels in a fixed order and repeats the cycle. The first channel of the cycle scanning starts the channel in manual channel mode. For example, if in manual channel mode, channel 3 is the conversion channel, the auto scanning sequence is 3, 4, 5, 6, 7, 3, and so forth. Figure 9 shows a demo of the channel switching timing sequence in auto channel select mode. The chip quits the scanning cycle after CFR bit D[11] is cleared to 0.

#### Start of a Conversion

The input signal is sampled on the falling edge of nCONVST, and the pin should be kept low for minimum of 60ns. After the input signal is sampled, the conversion is started at the same time. The conversion time is 18 CCLK cycles. The minimum time between two nCONVST falling pulses is 21 CCLKs. The time between a conversion completed and a new falling edge of nCONVST is the acquisition time.

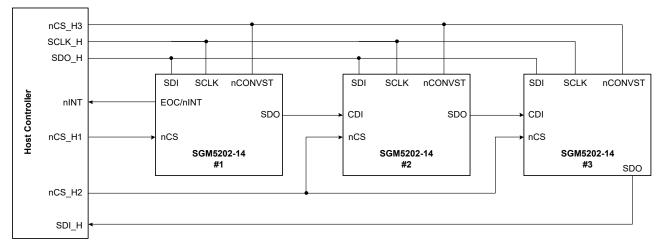

To allow multiple chips to sample simultaneously, the nCONVST pins of all chips can be controlled by one common

logic controller's output (please consider the driving ability of controller's output pin).

A conversion also can be triggered internally without an nCONVST signal. To let the chip work in auto-trigger mode, configure the CFR bit D[9] to 0. Under this auto-trigger mode, when a conversion is completed, it will take 3 more CCLK cycles (if the CFR bit D[8] is set to 0, see Table 4 and Table 5 for details), the next conversion is automatically triggered. Total acquisition time and conversion time are 21 CCLK cycles (if the CFR bit D[8] is set to 0, see Table 4 and Table 5 for details).

The different conversion modes are shown in Table 1.

Note that when the chip is configured to work with manual channel select and auto-trigger mode, it is usually used for a single channel conversion. If there is an input channel switching in this mode, the chip must be set to manual-trigger mode before an input MUX switching. After the channel switching is completed, the chip can be re-configured to work with manual channel select and auto-trigger mode.

#### Table 1. Different Conversion Types

| Mode      | Select Channel                                                                                                                                                                                      | Start Conversion                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Automatic | Auto Channel Select <sup>(1)</sup> : The chip scans the input channels<br>automatically. There is no need to write channel number to CMR.<br>More details refer to Auto Channel Select Mode section | Auto-Trigger Mode: Start a conversion with sequenced CCLK automatically |

| Manual    | Manual Channel Select: Select the channel number by CMR command                                                                                                                                     | Manual-Trigger Mode: Start a conversion with nCONVST                    |

NOTE:

1. It is recommended that auto channel select mode should be worked with auto-trigger mode and TAG bit output enabled.

## **DETAILED DESCRIPTION (continued)**

#### Status Output Pin (nEOC/nINT)

The function of the nEOC/nINT pin is software configurable. When the pin is used as nEOC output and its active polarity is set low, the pin will keep low throughout the conversion and go high if the conversion is completed. In manual-trigger mode, the pin goes low immediately once the nCONVST goes low, the pin will go high once the conversion is completed. In auto-trigger mode, after finishing the previous conversion, the pin goes high, and the pin will keep high for the first 3 CCLK cycles in the next conversion process frame.

If the pin of nEOC/nINT is configured as an interrupt output and active low, it goes low at the end of a conversion, and will go high by the next read cycle.

The function of the pin nEOC/nINT is set by CFR bit D[6]. The output polarity of the pin is set by CFR bit D[7].

#### Power-Down Modes

The chip has 3 power-down modes, including Nap, Deep, and Auto-Nap. They are all controlled by CFR according bits (refer to Table 5 for details).

Once the Nap power-down mode is enabled, the power consumption will reduce to around 2.6mA in 200ns. There are

several ways to call the chip to quit this power-down mode, disable this mode, issue a wake-up command, reset CFR to default value, or reset the chip (software or hardware, see Table 4 and Table 5 for further information). It will take the chip 3 CCLK cycles to wake up from Nap power-down mode.

If the Deep power-down mode is enabled, the chip will be shut down and the power consumption will drop to about  $25.2\mu$ A in 50ns. The wake-up time from this mode is about  $150\mu$ s. The methods of calling the chip to wake up are the same as waking from Nap power-down mode.

Once the Auto-Nap power-down mode is enabled, the chip will go to Nap power-down automatically after the next conversion is completed. The power consumption will reduce to around 2.6mA in 200ns. To call the chip to quit Auto-Nap power-down mode, besides the same method as the same as quitting Nap power-down mode, issuing a manual channel select command or starting a conversion also can call the chip to wake up. It will take the chip 3 CCLK cycles to wake up from Auto-Nap power-down mode.

Table 2 shows a comparison of the three power-down modes.

| Power-Down Type     | Power<br>Consumption<br>at V <sub>A</sub> = 5V | Power-Down<br>by         | Power-Down<br>Time | Wake-Up by                                                                                    | Wake-Up Time | Enable              |

|---------------------|------------------------------------------------|--------------------------|--------------------|-----------------------------------------------------------------------------------------------|--------------|---------------------|

| Normal Operation    | 7.5mA                                          | —                        | —                  | —                                                                                             | —            | —                   |

| Deep Power-Down     | 25.2µA                                         | Setting CFR bit<br>D[2]  | 50ns               | Wake-up command 1011b                                                                         | 150µs        | Set CFR bit<br>D[2] |

| Nap Power-Down      | 2.6mA                                          | Setting CFR bit<br>D[3]  | 200ns              | Wake-up command 1011b                                                                         | 3 CCLKs      | Set CFR bit<br>D[3] |

| Auto-Nap Power-Down | 2.6mA                                          | nEOC (end of conversion) | 200ns              | nCONVST, any channel select<br>command, default command<br>1111b, or wake-up command<br>1011b | 3 CCLKs      | Set CFR bit<br>D[4] |

#### Table 2. Comparison of Power-Down Modes

## **DETAILED DESCRIPTION (continued)**

#### Auto-Nap and Acquisition Time

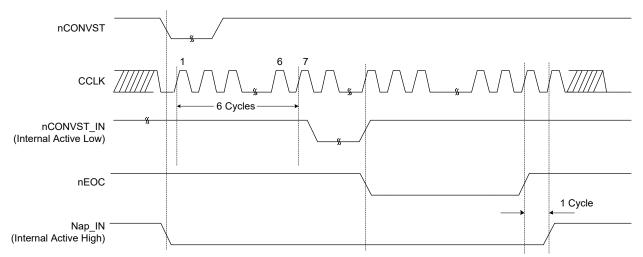

Figure 10 shows the timing diagram for nCONVST, nEOC and Auto-Nap power-down signals in manual-trigger mode. The nCONVST signal triggers the chip to wake up. It will take at least 3 CCLK cycles (3 Conversion Clock Cycles) to wake up and 3 CCLK cycles to acquire input.

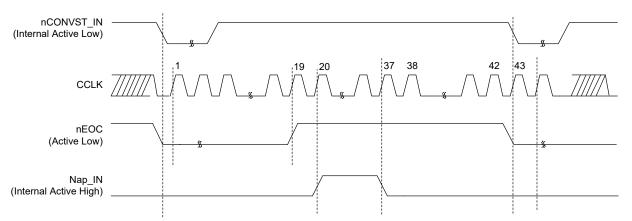

The SGM5202-14 supports two kinds of sampling rate 1MSPS and 500kSPS in auto-trigger mode. In 1MSPS sampling mode, it works in 21 CCLK cycles per conversion. In 500kSPS sampling mode, it works in 42 CCLK cycles per conversion.

The Nap power-down and Deep power-down are both available in 1MSPS and 500kSPS sampling modes. The

Auto-Nap power-down is only available in 500kSPS sampling mode, because there is no time for the core to power down in 1MSPS sampling rate.

Figure 11 shows a timing diagram for the conversion sequence in auto-trigger mode with Auto-Nap power-down signals in 500kSPS sampling rate. For 16-bit word output, two consecutive conversions are 42 CCLK cycles apart. Nap\_IN (active high, the signal powers down the ADC core) goes low 6 CCLK cycles ahead of the falling edge of nCONVST\_IN (internal signal, active low). Nap\_IN calls up the ADC core. It takes 3 CCLK cycles to power up the ADC core, and another 3 CCLK cycles are acquisition time. After the conversion is completed, the chip goes power-down automatically.

Figure 10. Timing Diagram for nCONVST, nEOC, and Auto-Nap Power-Down Signals in Manual-Trigger Mode (3 CCLKs for Acquisition)

Figure 11. Timing Diagram for Conversion Start and Auto-Nap Power-Down Signals in Auto-Trigger Mode (500kSPS Sampling and 3 CCLKs for Acquisition)

Table 3 lists the total of the acquisition time and conversion time for the different combinations of triggers and power-down modes.

#### Table 3. Total Acquisition + Conversion Times

SGM5202-14

| Mode                                    | Acquisition + Conversion Time                                                   |

|-----------------------------------------|---------------------------------------------------------------------------------|

| Auto-Trigger at 1MSPS                   | = 21 CCLK                                                                       |

| Manual-Trigger                          | ≥ 21 CCLK                                                                       |

| Manual-Trigger with Deep Power-Down     | ≥ 4 SCLK + 1µs + 3 CCLK + 18 CCLK + 16 SCLK + 150µs                             |

| Manual-Trigger with Nap Power-Down      | ≥ 4 SCLK + 3 CCLK + 3 CCLK + 18 CCLK + 16 SCLK + 200ns                          |

| Manual Trigger with Auto Nan Power Down | ≥ 4 SCLK + 3 CCLK + 3 CCLK + 18 CCLK + 1 CCLK + 200ns (using wake-up to resume) |

| Manual-Trigger with Auto-Nap Power-Down | ≥ 3 CCLK + 3 CCLK + 18 CCLK + 1 CCLK + 200ns (using nCONVST to resume)          |

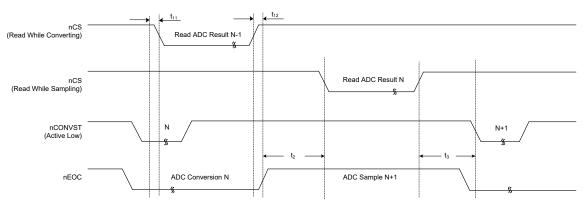

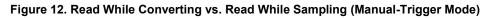

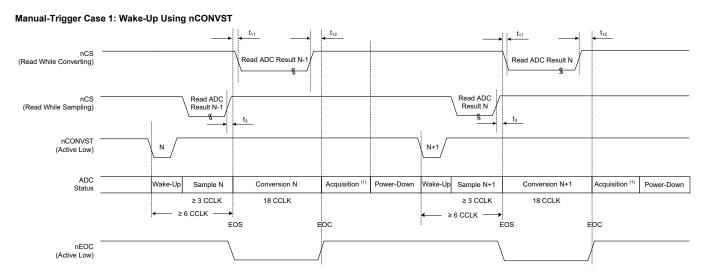

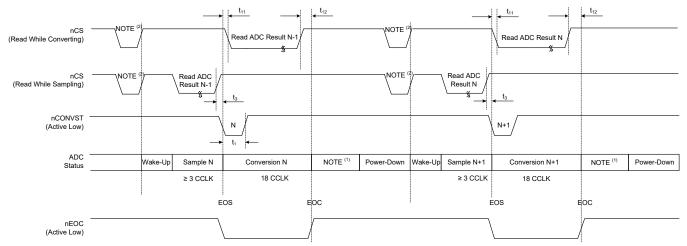

Figure 12 to Figure 14 show the different combinations of various trigger and power-down modes.

#### Manual-Trigger Case 2: Wake-Up Using WAKEUP Command

NOTES:

The time between the end of a conversion and Auto-Nap power-down is 1 CCLK cycle.

Command on SDI pin is minimum 4 CCLK cycles.

#### Figure 14. Read While Converting vs. Read While Sampling with Auto-Nap Power-Down

### Programming

#### **Digital Interface**