## SGM71612R81/SGM71612R82/SGM71612R83 8 Channels, 16-Bit, SPI Interface, Voltage-Output DAC with 10ppm/°C On-Chip Reference

#### GENERAL DESCRIPTION

The SGM71612R81/SGM71612R82/SGM71612R83 family is a 16-bit, 8 channels, voltage-output digital-to-analog converter (DAC). These chips are guaranteed monotonic by design.

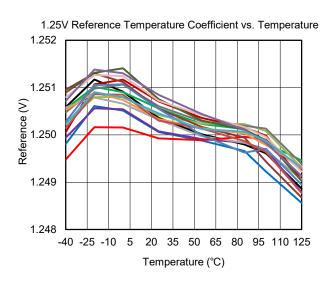

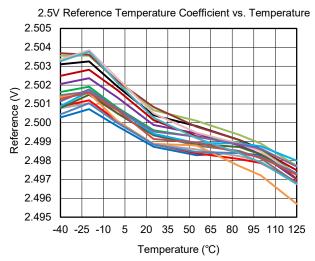

The SGM71612R81Z has an on-chip 1.25V 10ppm/°C reference, giving a full-scale output range of 2.5V. The SGM71612R82Z/SGM71612R82M/SGM71612R83M have an on-chip 2.5V 10ppm/°C reference, giving a full-scale output range of 5V.

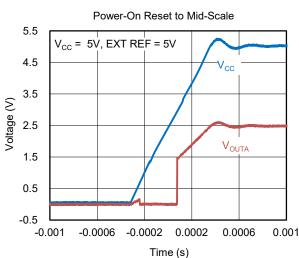

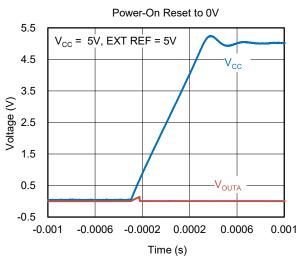

The chips have a power-on control circuit, which can ensure that DAC has a fixed output when the system is powered on. The SGM71612R81Z and SGM71612R82Z output 0V when the system is powered up, and the SGM71612R82M/SGM71612R83M outputs mid-scale when the system is powered up.

The chips have an nLDAC pin that allows the DAC to update the output simultaneously. And the chips have an nCLR pin that allows the DAC to be updated to a configurable state, zero-code, mid-scale, or full-scale.

The SGM71612R81/SGM71612R82/SGM71612R83 family uses a 3-wire SPI-compatible interface, and its operation data rate is up to 50MHz.

The SGM71612R81Z and SGM71612R82Z are available in Green TSSOP-16, TQFN-4×4-16BL and FOCSP-2.6×2.6-16B packages. The SGM71612R82M and SGM71612R83M are available in Green TSSOP-16 and TQFN-4×4-16BL packages.

#### **FEATURES**

- Power Supply Range: 2.7V to 5.5V

- On-Chip 1.25V/2.5V, 10ppm/°C Reference

- + SGM71612R81Z: 1.25V

- SGM71612R82Z/SGM71612R82M/SGM71612R83M:

2.5V

- Power Down to 500nA (TYP) at 5V, 300nA (TYP) at 3V

- Monotonicity Guaranteed by Design

- Power-On Reset to Zero-Scale or Mid-Scale

- SGM71612R81Z/SGM71612R82Z:

Power-On Reset to Zero

- SGM71612R82M/SGM71612R83M:

Power-On Reset to Mid-Scale

- 3 Power-Down Modes

- Hardware nLDAC and nLDAC Override Function

- nCLR Function to Programmable Code

- Rail-to-Rail Buffered Voltage-Output Operation

- Available in Green TSSOP-16, TQFN-4×4-16BL and FOCSP-2.6×2.6-16B Packages

#### **APPLICATIONS**

Process Control and DCS Systems

Data Acquisition Systems

Lab Instrumentations

## **PACKAGE/ORDERING INFORMATION**

| MODEL        | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER      | PACKAGE<br>MARKING                 | PACKING<br>OPTION   |

|--------------|------------------------|-----------------------------------|-------------------------|------------------------------------|---------------------|

|              | T000D 40               | 4000 1 . 40500                    | SGM71612R81ZXTS16G/TR   | SGM01N<br>XTS16<br>XXXXX           | Tape and Reel, 4000 |

|              | TSSOP-16               | -40°C to +125°C                   | SGM71612R81ZXTS16SG/TR  | SGM01N<br>XTS16<br>XXXXX           | Tape and Reel, 250  |

|              | TQFN-4×4-16BL          | -40°C to +125°C                   | SGM71612R81ZXTSG16G/TR  | SGM010<br>XTSG16<br>XXXXX          | Tape and Reel, 3000 |

| SGM71612R81Z | TQFN-4^4-10DL          | -40 C to +125 C                   | SGM71612R81ZXTSG16SG/TR | SGM010<br>XTSG16<br>XXXXX          | Tape and Reel, 250  |

|              | FOCSP-2.6×2.6-16B      | 40°C to ±135°C                    | SGM71612R81ZXG/TR       | SGM<br>71612R81Z<br>XXXXX<br>XX#XX | Tape and Reel, 5000 |

|              | FOGSF-2.0^2.0-10B      | -40 C to +125 C                   | SGM71612R81ZXSG/TR      | SGM<br>71612R81Z<br>XXXXX<br>XX#XX | Tape and Reel, 250  |

|              | TSSOR 46               | -40°C to +125°C                   | SGM71612R82ZXTS16G/TR   | SGM0DC<br>XTS16<br>XXXXX           | Tape and Reel, 4000 |

|              | TSSOP-16               | -40 0 10 1123 0                   | SGM71612R82ZXTS16SG/TR  | SGM0DC<br>XTS16<br>XXXXX           | Tape and Reel, 250  |

|              | TQFN-4×4-16BL          | 40°C to ±125°C                    | SGM71612R82ZXTSG16G/TR  | SGM0DD<br>XTSG16<br>XXXXX          | Tape and Reel, 3000 |

| SGM71612R82Z | 1Q114-4-4-10DE         | -40°C to +125°C                   | SGM71612R82ZXTSG16SG/TR | SGM0DD<br>XTSG16<br>XXXXX          | Tape and Reel, 250  |

|              | FOOSD 2 6×2 6 46D      | 4000 / 40-700                     | SGM71612R82ZXG/TR       | SGM<br>71612R82Z<br>XXXXX<br>XX#XX | Tape and Reel, 5000 |

|              | FOCSP-2.6×2.6-16B      | -40 C to +125 C                   | SGM71612R82ZXSG/TR      | SGM<br>71612R82Z<br>XXXXX<br>XX#XX | Tape and Reel, 250  |

|              | TSSOD 16               | 40°C to 1405°C                    | SGM71612R82MXTS16G/TR   | SGM0EJ<br>XTS16<br>XXXXX           | Tape and Reel, 4000 |

| SCM74642D92M | TSSOP-16               | -40°C to +125°C                   | SGM71612R82MXTS16SG/TR  | SGM0EJ<br>XTS16<br>XXXXX           | Tape and Reel, 250  |

| SGM71612R82M | TQFN-4×4-16BL          | -40°C to +125°C                   | SGM71612R82MXTSG16G/TR  | SGM0EK<br>XTSG16<br>XXXXX          | Tape and Reel, 3000 |

|              | I GLIV-TOTE            | - <del></del>                     | SGM71612R82MXTSG16SG/TR | SGM0EK<br>XTSG16<br>XXXXX          | Tape and Reel, 250  |

## SGM71612R81 8 Channels, 16-Bit, SPI Interface, Voltage-Output DAC SGM71612R82/SGM71612R83 with 10ppm/°C On-Chip Reference

| MODEL         | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER      | PACKAGE<br>MARKING        | PACKING<br>OPTION   |

|---------------|------------------------|-----------------------------------|-------------------------|---------------------------|---------------------|

|               | TSSOP-16               | -40°C to +125°C                   | SGM71612R83MXTS16G/TR   | SGM0M4<br>XTS16<br>XXXXX  | Tape and Reel, 4000 |

| SGM71612R83M  | 1330F-10               | -40 C t0 +125 C                   | SGM71612R83MXTS16SG/TR  | SGM0M4<br>XTS16<br>XXXXX  | Tape and Reel, 250  |

| 3GW/ 1012R03W | TOFN-4×4-16BL          | EN 404 40DL 4000 to 140500        | SGM71612R83MXTSG16G/TR  | SGM0M5<br>XTSG16<br>XXXXX | Tape and Reel, 3000 |

|               | 1 QFIV-4*4-10DL        | -40°C to +125°C                   | SGM71612R83MXTSG16SG/TR | SGM0M5<br>XTSG16<br>XXXXX | Tape and Reel, 250  |

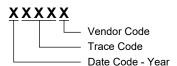

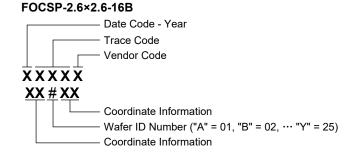

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code. XX#XX = Coordinate Information and Wafer ID Number.

TSSOP-16/TQFN-4×4-16BL

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

## SGM71612R81 8 Channels, 16-Bit, SPI Interface, Voltage-Output DAC SGM71612R82/SGM71612R83 with 10ppm/°C On-Chip Reference

#### **ABSOLUTE MAXIMUM RATINGS**

| Input Voltage Range                            | -0.3V to 6V                    |

|------------------------------------------------|--------------------------------|

|                                                |                                |

| Digital Input Voltage Range                    | 0.3V to $V_{CC}$ + 0.3V        |

| Output Voltage Range                           | 0.3V to $V_{CC}$ + 0.3V        |

| V <sub>REFIN</sub> /V <sub>REFOUT</sub> to GND | 0.3V to V <sub>CC</sub> + 0.3V |

| Package Thermal Resistance                     |                                |

| TSSOP-16, θ <sub>JA</sub>                      | 92°C/W                         |

| TQFN-4×4-16BL, θ <sub>JA</sub>                 | 34°C/W                         |

| FOCSP-2.6×2.6-16B, θ <sub>JA</sub>             | 58°C/W                         |

| Junction Temperature                           | +150°C                         |

| Storage Temperature Range                      | 65°C to +150°C                 |

| Lead Temperature (Soldering, 10s)              | +260°C                         |

| ESD Susceptibility                             |                                |

| HBM                                            | 4000V                          |

| CDM                                            | 1000V                          |

#### RECOMMENDED OPERATING CONDITIONS

Operating Temperature Range .....-40°C to +125°C

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

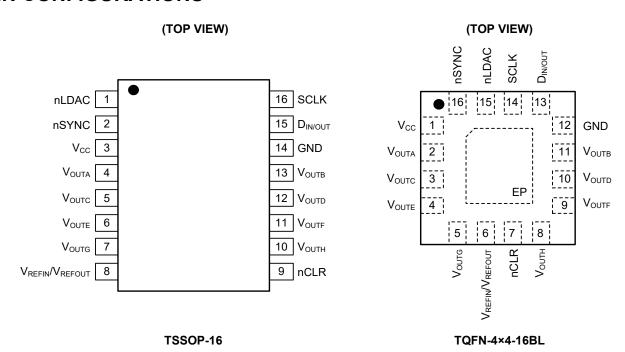

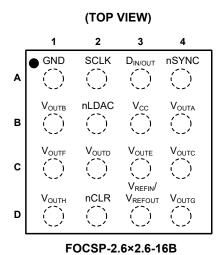

### **PIN CONFIGURATIONS**

## **PIN DESCRIPTION**

|          | PIN           |                       |                        |                                                                                                                                                                                                                     |

|----------|---------------|-----------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP-16 | TQFN-4×4-16BL | FOCSP-<br>2.6×2.6-16B | NAME                   | FUNCTION                                                                                                                                                                                                            |

| 1        | 15            | B2                    | nLDAC                  | Active low. Set this pin high and then set it low. On the falling edge of nLDAC, the DAC outputs are updated simultaneously. If the simultaneous update function of hardware is not used, this pin can be kept low. |

| 2        | 16            | A4                    | nSYNC                  | Frame Synchronization Input Pin. Active low. During 32-bit data shifting in, the pin must be kept low.                                                                                                              |

| 3        | 1             | В3                    | $V_{CC}$               | Power Supply Input.                                                                                                                                                                                                 |

| 4        | 2             | B4                    | V <sub>OUTA</sub>      |                                                                                                                                                                                                                     |

| 5        | 3             | C4                    | Voutc                  | Analog Output Valtage from DAC                                                                                                                                                                                      |

| 6        | 4             | C3                    | V <sub>OUTE</sub>      | Analog Output Voltage from DAC.                                                                                                                                                                                     |

| 7        | 5             | D4                    | $V_{OUTG}$             |                                                                                                                                                                                                                     |

| 8        | 6             | D3                    | $V_{REFIN}/V_{REFOUT}$ | Analog Voltage Reference Input and Reference Output.                                                                                                                                                                |

| 9        | 7             | D2                    | nCLR                   | Active low. Set this pin high and then set it low. On the falling edge of nCLR, the DAC register is updated with the data contained in the clear code register. When nCLR is low, all nLDAC pulses are invalid.     |

| 10       | 8             | D1                    | V <sub>OUTH</sub>      |                                                                                                                                                                                                                     |

| 11       | 9             | C1                    | V <sub>OUTF</sub>      | Analog Output Valtage from DAC                                                                                                                                                                                      |

| 12       | 10            | C2                    | Voutd                  | Analog Output Voltage from DAC.                                                                                                                                                                                     |

| 13       | 11            | B1                    | V <sub>OUTB</sub>      |                                                                                                                                                                                                                     |

| 14       | 12            | A1                    | GND                    | Ground.                                                                                                                                                                                                             |

| 15       | 13            | A3                    | D <sub>IN/OUT</sub>    | Serial Data Input/Output Pin.                                                                                                                                                                                       |

| 16       | 14            | A2                    | SCLK                   | Serial Clock Input Pin. Data is clocked on the falling edge of SCLK.                                                                                                                                                |

| _        | Exposed Pad   | _                     | EP                     | Exposed Pad. This pad should be connected to GND.                                                                                                                                                                   |

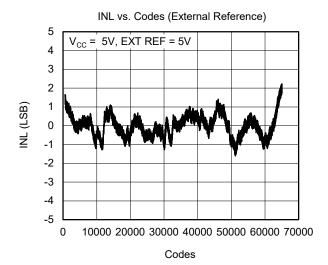

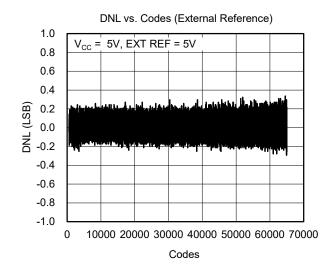

## **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 4.5V \text{ to } 5.5V, R_L = 2k\Omega \text{ to GND, } C_L = 200pF \text{ to GND, } V_{REFIN} = V_{CC}, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.})$

| PAR                   | PARAMETER        |      | CONDITIONS                                                           | MIN   | TYP  | MAX             | UNITS  |

|-----------------------|------------------|------|----------------------------------------------------------------------|-------|------|-----------------|--------|

| Static Perforn        | nance (1)        | _    |                                                                      |       |      |                 |        |

| Resolution            |                  |      |                                                                      | 16    |      |                 | Bits   |

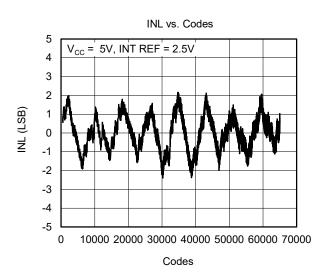

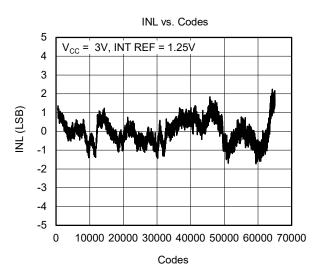

| Relative Accuracy INI |                  | INL  |                                                                      |       | 1.8  | 6               | LSB    |

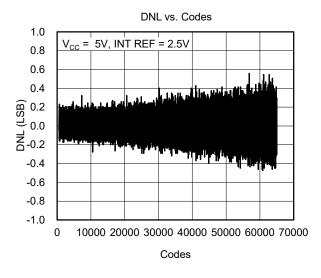

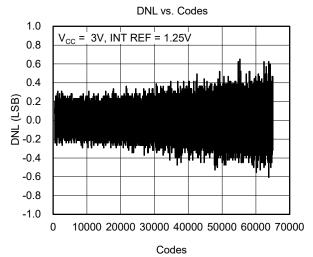

| Differential No       | nlinearity       | DNL  | Guaranteed monotonic by design                                       |       |      | 1               | LSB    |

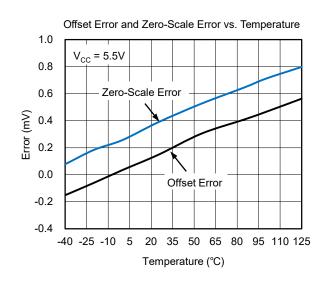

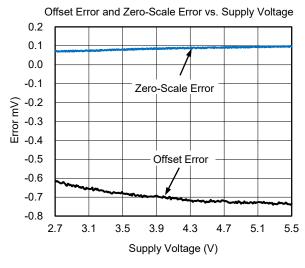

| Zero-Code Err         | or               |      | All 0s loaded to DAC register                                        |       | 0.5  | 4               | mV     |

| Zero-Code Err         | or Drift         |      |                                                                      |       | 5.5  |                 | μV/°C  |

| Full-Scale Erro       | or               |      | All 1s loaded to DAC register                                        |       | 0.1  | 0.4             | % FSR  |

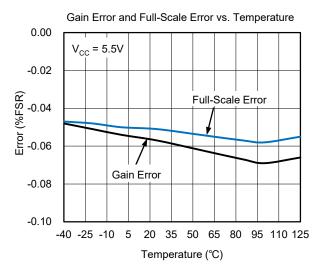

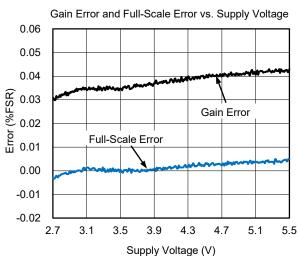

| Gain Error            |                  |      |                                                                      |       |      | 0.4             | % FSR  |

| Gain Tempera          | ture Coefficient |      | Of FSR/°C                                                            |       | 1.5  |                 | ppm    |

| Offset Error          |                  |      |                                                                      |       | 0.7  | 5               | mV     |

| Power Supply          | Rejection Ratio  | PSRR | V <sub>CC</sub> ± 10%                                                |       | -100 |                 | dB     |

|                       | External         |      | Due to full-scale output change, $R_L = 2k\Omega$ to GND or $V_{CC}$ |       | 5    |                 | μV     |

|                       | Reference        |      | Due to load current change                                           |       | 18   |                 | μV/mA  |

| DC Crosstalk          |                  |      | Due to powering down (per channel)                                   |       | 10   |                 | μV     |

|                       | Internal         |      | Due to full-scale output change, $R_L = 2k\Omega$ to GND or $V_{CC}$ |       | 5    |                 | μV     |

|                       | Reference        |      | Due to load current change                                           |       | 40   |                 | μV/mA  |

| Output Chara          | cteristics (2)   |      |                                                                      |       |      |                 |        |

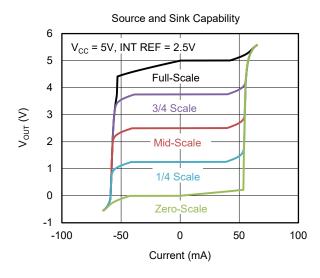

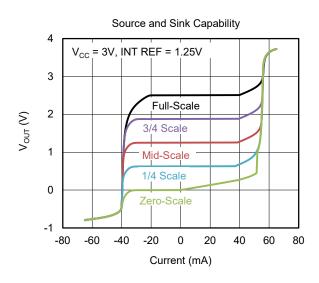

| Output Voltage        | Range            |      |                                                                      | 0     |      | Vcc             | V      |

| 0 : : : 1             | 1.04-1-104-      |      | R <sub>L</sub> = ∞                                                   |       | 2    |                 |        |

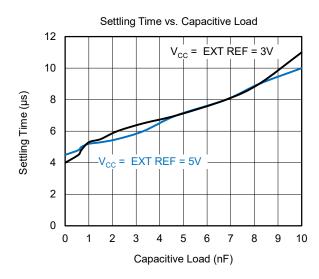

| Capacitive Loa        | id Stability     |      | $R_L = 2k\Omega$                                                     |       | 10   |                 | nF     |

| DC Output Imp         | edance           |      |                                                                      |       | 0.15 |                 | Ω      |

| Short-Circuit C       | urrent           |      | V <sub>CC</sub> = 5V                                                 |       | 56   |                 | mA     |

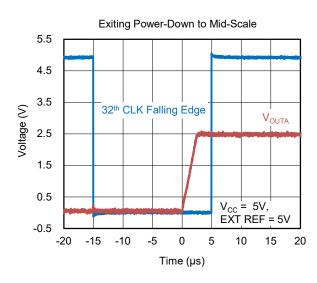

| Power-Up Time         | e                |      | Coming out of power-down mode, V <sub>CC</sub> = 5V                  |       | 15   |                 | μs     |

| Reference Inp         | outs             |      |                                                                      |       |      |                 |        |

| Reference Cur         | rent             |      | V <sub>REF</sub> = V <sub>CC</sub> = 5.5V (per DAC channel)          |       | 25   | 37.5            | μA     |

| Reference Inpu        | ut Range         |      |                                                                      | 0     |      | V <sub>CC</sub> | V      |

| Reference Inpu        | ut Impedance     |      |                                                                      |       | 28   |                 | kΩ     |

| Reference Ou          | tputs            |      |                                                                      |       |      |                 |        |

| Output Voltage        |                  |      | At ambient                                                           | 2.495 |      | 2.505           | V      |

| Reference TC          | (2)              |      |                                                                      |       | 10   | 25              | ppm/°C |

| Reference Out         | put Impedance    |      |                                                                      |       | 0.3  |                 | Ω      |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 4.5V \text{ to } 5.5V, R_L = 2k\Omega \text{ to GND, } C_L = 200pF \text{ to GND, } V_{REFIN} = V_{CC}, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER          | SYMBOL          | С                                     | CONDITIONS                                                                                                         |     | TYP | MAX | UNITS |

|--------------------|-----------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Logic Inputs (2)   |                 | •                                     |                                                                                                                    |     | •   | •   | •     |

| Input Current      |                 | All digital inputs                    |                                                                                                                    |     |     | 1   | μΑ    |

| Input Low Voltage  | V <sub>IL</sub> | V <sub>CC</sub> = 5V                  |                                                                                                                    |     |     | 0.8 | V     |

| Input High Voltage | V <sub>IH</sub> | V <sub>CC</sub> = 5V                  |                                                                                                                    | 2.0 |     |     | V     |

| Pin Capacitance    |                 |                                       |                                                                                                                    |     | 5   |     | pF    |

| Power Requirements | •               |                                       |                                                                                                                    |     | •   | •   | •     |

| Power Supply Range | V <sub>cc</sub> | All digital inputs a excludes load cu | at 0 or V <sub>CC</sub> , DAC active,<br>rrent                                                                     | 4.5 |     | 5.5 | V     |

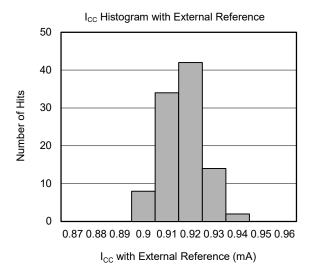

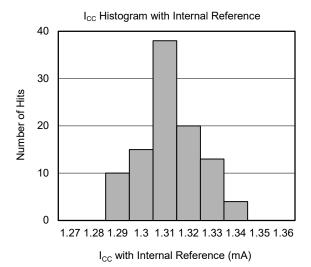

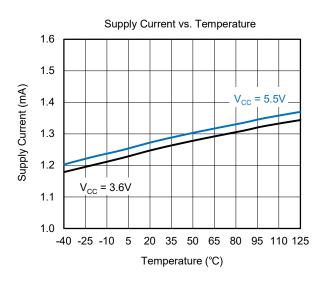

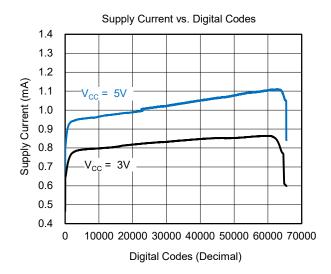

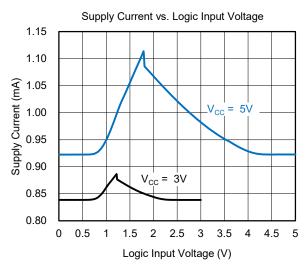

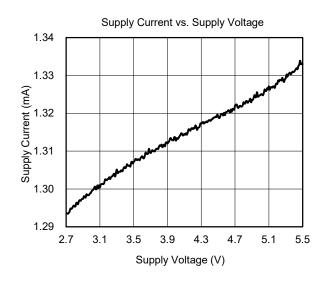

|                    |                 | Normal mode (3)                       | $V_{CC}$ = 4.5V to 5.5V, $V_{IH}$ = $V_{CC}$ and $V_{IL}$ = GND, internal reference off                            |     | 1   | 1.3 | m A   |

| Supply Current     | Icc             | Normal mode **                        | $V_{\text{CC}}$ = 4.5V to 5.5V, $V_{\text{IH}}$ = $V_{\text{CC}}$ and $V_{\text{IL}}$ = GND, internal reference on |     | 1.4 | 1.9 | - mA  |

|                    |                 | All power-down modes (4)              | $V_{CC}$ = 4.5V to 5.5V,<br>$V_{IH}$ = $V_{CC}$ and $V_{IL}$ = GND                                                 |     | 0.5 | 10  | μΑ    |

#### NOTES:

- 1. Linearity calculated uses a reduced code range of SGM71612R81/SGM71612R82/SGM71612R83 family (code 512 to 65,024). Output unloaded.

- 2. Guaranteed by design. Not production tested.

- 3. Interface inactive. All DACs are active. DAC outputs unloaded.

- 4. All 8 DACs are powered down.

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.7 \text{V to } 3.6 \text{V}, R_L = 2 \text{k}\Omega \text{ to GND, } C_L = 200 \text{pF to GND, } V_{REFIN} = V_{CC}, T_A = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER             |                               | SYMBOL | CONDITIONS                                                           | MIN      | TYP  | MAX             | UNITS  |

|-----------------------|-------------------------------|--------|----------------------------------------------------------------------|----------|------|-----------------|--------|

| Static Performa       | nce <sup>(1)</sup>            |        | ,                                                                    | <u> </u> |      |                 |        |

| Resolution            |                               |        |                                                                      | 16       |      |                 | Bits   |

| Relative Accurac      | sy .                          | INL    |                                                                      |          | 1.8  | 6               | LSB    |

| Differential Nonli    | nearity                       | DNL    | Guaranteed monotonic by design                                       |          |      | 1               | LSB    |

| Zero-Code Error       |                               |        | All 0s loaded to DAC register                                        |          | 0.3  | 3               | mV     |

| Zero-Code Error       | Drift                         |        |                                                                      |          | 1.2  |                 | μV/°C  |

| Full-Scale Error      |                               |        | All 1s loaded to DAC register                                        |          | 0.1  | 0.4             | % FSR  |

| Gain Error            |                               |        |                                                                      |          |      | 0.4             | % FSR  |

| Gain Temperatur       | re Coefficient                |        | Of FSR/°C                                                            |          | 3.3  |                 | ppm    |

| Offset Error          |                               |        |                                                                      |          | 0.7  | 3.5             | mV     |

| Power Supply Re       | ejection Ratio <sup>(2)</sup> | PSRR   | V <sub>CC</sub> ± 10%                                                |          | -90  |                 | dB     |

|                       | External                      |        | Due to full-scale output change, $R_L = 2k\Omega$ to GND or $V_{CC}$ |          | 5    |                 | μV     |

|                       | Reference                     |        | Due to load current change                                           |          | 18   |                 | μV/mA  |

| DC Crosstalk (2)      |                               |        | Due to powering down (per channel)                                   |          | 8    |                 | μV     |

|                       | Internal                      |        | Due to full-scale output change, $R_L = 2k\Omega$ to GND or $V_{CC}$ |          | 5    |                 | μV     |

|                       | Reference                     |        | Due to load current change                                           |          | 40   |                 | μV/mA  |

| Output Characte       | eristics <sup>(2)</sup>       |        |                                                                      |          |      |                 |        |

| Output Voltage F      | Range                         |        |                                                                      | 0        |      | Vcc             | V      |

| Canacitiva Laad       | Ctobility                     |        | R <sub>L</sub> = ∞                                                   |          | 2    |                 | nF     |

| Capacitive Load       | Stability                     |        | $R_L = 2k\Omega$                                                     |          | 10   |                 |        |

| DC Output Imped       | dance                         |        |                                                                      |          | 0.15 |                 | Ω      |

| Short-Circuit Cur     | rent                          |        | V <sub>CC</sub> = 3V                                                 |          | 40   |                 | mA     |

| Power-Up Time         |                               |        | Coming out of power-down mode, V <sub>CC</sub> = 3V                  |          | 15   |                 | μs     |

| Reference Input       | ts                            |        |                                                                      |          |      |                 |        |

| Reference Curre       | nt                            |        | V <sub>REF</sub> = V <sub>CC</sub> (per DAC channel)                 |          | 12.5 | 25              | μΑ     |

| Reference Input Range |                               |        |                                                                      | 0        |      | V <sub>CC</sub> | V      |

| Reference Input       | Impedance                     |        |                                                                      |          | 28   |                 | kΩ     |

| Reference Outp        | uts                           |        |                                                                      |          |      |                 |        |

| Output Voltage        |                               |        | At ambient                                                           | 1.245    |      | 1.255           | V      |

| Reference TC (2)      |                               |        |                                                                      |          | 10   | 25              | ppm/°C |

| Reference Outpu       | ıt Impedance                  |        |                                                                      |          | 0.3  |                 | Ω      |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.7 \text{V to } 3.6 \text{V}, R_L = 2 \text{k}\Omega \text{ to GND}, C_L = 200 \text{pF to GND}, V_{REFIN} = V_{CC}, T_A = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER          | SYMBOL          | С                                     | CONDITIONS                                                                                                              |     | TYP | MAX | UNITS |

|--------------------|-----------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Logic Inputs (2)   | <u> </u>        | •                                     |                                                                                                                         |     |     |     | •     |

| Input Current      |                 | All digital inputs                    |                                                                                                                         |     |     | 1   | μΑ    |

| Input Low Voltage  | V <sub>IL</sub> | V <sub>CC</sub> = 3V                  |                                                                                                                         |     |     | 0.8 | V     |

| Input High Voltage | V <sub>IH</sub> | V <sub>CC</sub> = 3V                  |                                                                                                                         | 2.0 |     |     | V     |

| Pin Capacitance    |                 |                                       |                                                                                                                         |     | 5   |     | pF    |

| Power Requirements |                 |                                       |                                                                                                                         |     |     |     |       |

| Power Supply Range | V <sub>CC</sub> | All digital inputs a excludes load cu | at 0 or V <sub>CC</sub> , DAC active,<br>rrent                                                                          | 2.7 |     | 3.6 | V     |

|                    |                 | Normal mode (3)                       | $V_{CC}$ = 2.7 to 3.6V,<br>$V_{IH}$ = $V_{CC}$ and $V_{IL}$ = GND,<br>internal reference off                            |     | 0.8 | 1.3 | mA    |

| Supply Current     | I <sub>cc</sub> | Normal Mode V                         | $V_{\text{CC}}$ = 2.7 to 3.6V,<br>$V_{\text{IH}}$ = $V_{\text{CC}}$ and $V_{\text{IL}}$ = GND,<br>internal reference on |     | 1.3 | 1.9 | IIIA  |

|                    |                 | All power-down modes (4)              | $V_{CC}$ = 2.7 to 3.6V,<br>$V_{IH}$ = $V_{CC}$ and $V_{IL}$ = GND                                                       |     | 0.3 | 10  | μΑ    |

#### NOTES:

- 1. Linearity calculated uses a reduced code range of SGM71612R81/SGM71612R82/SGM71612R83 family (code 512 to 65,024). Output unloaded.

- 2. Guaranteed by design. Not production tested.

- 3. Interface inactive. All DACs are active. DAC outputs unloaded.

- 4. All 8 DACs are powered down.

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 2.7V \text{ to } 5.5V, R_L = 2k\Omega \text{ to GND, } C_L = 200pF \text{ to GND, } V_{REFIN} = V_{CC}, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                     | SYMBOL                    | CONDITIONS                                                     | MIN       | TYP | MAX   | UNITS |                  |

|-------------------------------|---------------------------|----------------------------------------------------------------|-----------|-----|-------|-------|------------------|

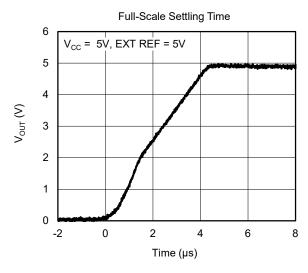

| Output Voltage Settling Time  |                           | 1/4 to 3/4 scale settling to ±2LSB (16-bit re                  | solution) |     | 4     |       | μs               |

| Slew Rate                     |                           |                                                                |           |     | 1     |       | V/µs             |

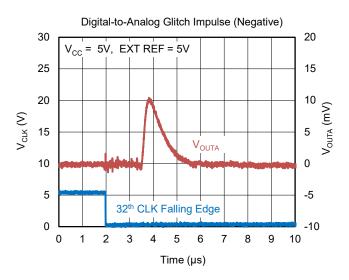

| Digital-to-Analog Glitch      |                           | 1LSB (16-bit resolution) change around carry                   | major     |     | 2.3   |       | n\/ o            |

| Impulse                       |                           | From code 0xEA00 to code 0xE9FF (16-bit resolution)            |           | 12  |       | nV-s  |                  |

| Digital Feedthrough           |                           |                                                                |           |     | 0.05  |       | nV-s             |

| Digital Crosstalk             |                           |                                                                |           |     | 0.003 |       | nV-s             |

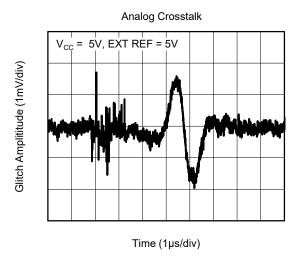

| Analog Crosstalk              |                           |                                                                |           |     | 2.4   |       | nV-s             |

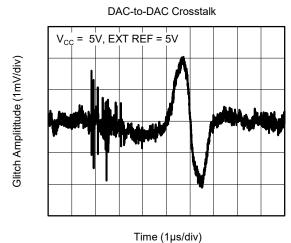

| DAC-to-DAC Crosstalk          |                           |                                                                |           |     | 2.4   |       | nV-s             |

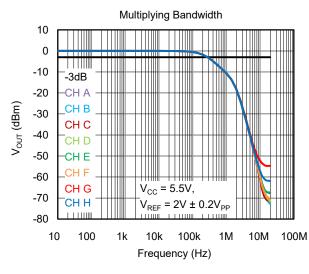

| Multiplying Bandwidth         |                           | $V_{REF} = 2V \pm 0.2V_{PP}$                                   |           |     | 270   |       | kHz              |

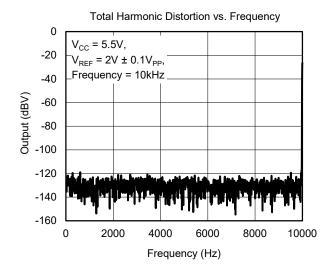

| Total Harmonic Distortion     | THD                       | V <sub>REF</sub> = 2V ± 0.1V <sub>PP</sub> , frequency = 10kHz |           |     | -80   |       | dB               |

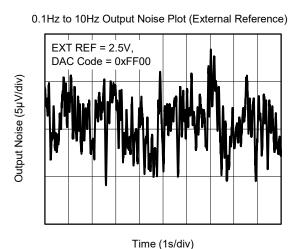

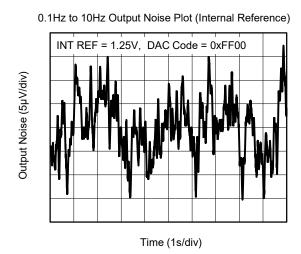

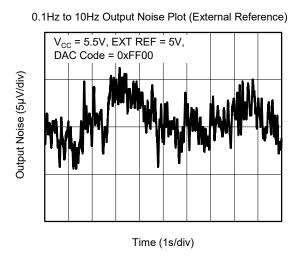

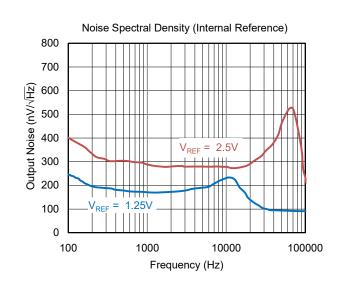

| Output Noine Spectral Density | DAO and a Occident Danish |                                                                | 1kHz      |     | 110   |       | ///              |

| Output Noise Spectral Density |                           | DAC code = 0x8400 (16-bit resolution)                          |           |     | 100   |       | nV/√Hz           |

| Output Noise                  |                           | 0.1Hz to 10Hz, DAC code = 0x0000                               |           |     | 2     |       | μV <sub>PP</sub> |

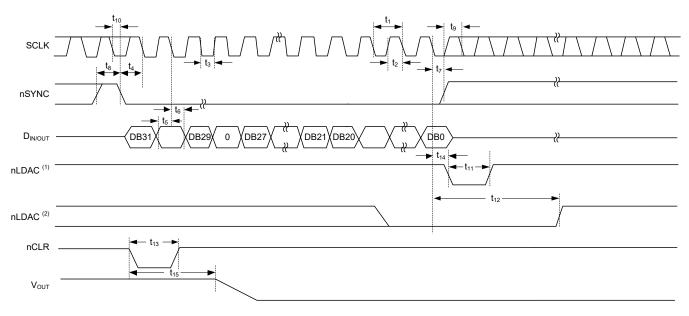

### **TIMING CHARACTERISTICS**

$(V_{CC} = 2.7 \text{V to } 5.5 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}.$  All input signals are specified with  $t_r = t_f = 1 \text{ns/V}$  (10% to 90% of  $V_{CC}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ , unless otherwise noted.) (1)

| PARAMETER                               | SYMBOL             | CONDITIONS | MIN | TYP | MAX | UNITS |

|-----------------------------------------|--------------------|------------|-----|-----|-----|-------|

| SCLK Cycle Time                         | t <sub>1</sub> (2) |            | 20  |     |     | ns    |

| SCLK High Time                          | t <sub>2</sub>     |            | 8   |     |     | ns    |

| SCLK Low Time                           | t <sub>3</sub>     |            | 8   |     |     | ns    |

| nSYNC to SCLK Falling Edge Setup Time   | t <sub>4</sub>     |            | 13  |     |     | ns    |

| Data Setup Time                         | t <sub>5</sub>     |            | 4   |     |     | ns    |

| Data Hold Time                          | t <sub>6</sub>     |            | 4   |     |     | ns    |

| SCLK Falling Edge to nSYNC Rising Edge  | t <sub>7</sub>     |            | 0   |     |     | ns    |

| Minimum nSYNC High Time                 | t <sub>8</sub>     |            | 15  |     |     | ns    |

| nSYNC Rising Edge to SCLK Fall Ignore   | t <sub>9</sub>     |            | 13  |     |     | ns    |

| SCLK Falling Edge to nSYNC Fall Ignore  | t <sub>10</sub>    |            | 0   |     |     | ns    |

| nLDAC Pulse Width Low                   | t <sub>11</sub>    |            | 10  |     |     | ns    |

| SCLK Falling Edge to nLDAC Rising Edge  | t <sub>12</sub>    |            | 15  |     |     | ns    |

| nCLR Pulse Width Low                    | t <sub>13</sub>    |            | 5   |     |     | ns    |

| SCLK Falling Edge to nLDAC Falling Edge | t <sub>14</sub>    |            | 0   |     |     | ns    |

| nCLR Pulse Activation Time              | t <sub>15</sub>    |            | 300 |     |     | ns    |

#### NOTES:

- 1. Refer to Figure 1 and Figure 2.

- 2. The SCLK frequency is 50MHz (MAX) at  $V_{CC}$  = 2.7V to 5.5V. Guaranteed by design, not production tested.

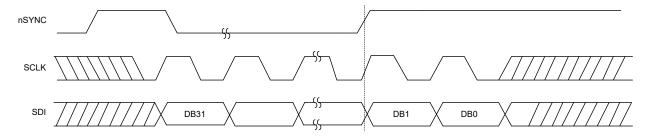

#### TIMING DIAGRAMS

#### NOTES:

- 1. Asynchronous load update mode. DAC is updated on the falling edge of nLDAC.

- Synchronous load update mode. nLDAC can be tied low permanently.

Once 3-wire SPI read function is enabled, DB28 must be '0', otherwise DB28 will be ignored by DAC.

Figure 1. Serial Write Operation

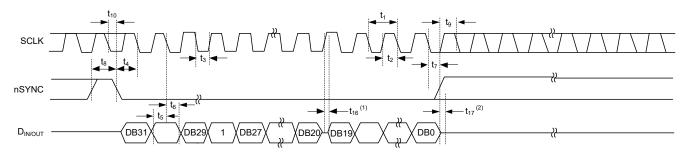

#### NOTES:

- 1. When DB28 = 1, this is a read operation, the data DB[19:0] is read from DAC. On the 12<sup>th</sup> rising edge of SCLK, the D<sub>IN/OUT</sub> switches from input to output,

- the data of internal register is put on the bus on each rising edge of SCLK. 2. On the rising edge of nSYNC, the  $D_{\text{IN/OUT}}$  is turned off to HI-Z.

- 3. Before issuing a read sequence, it is necessary to enable read function by setting read enable control register firstly.

Figure 2. Serial Read Operation

#### TYPICAL PERFORMANCE CHARACTERISTICS

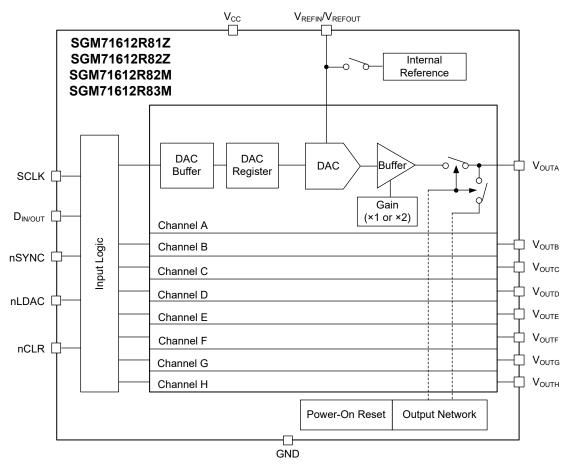

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 3. Block Diagram

#### **DETAILED DESCRIPTION**

#### **DAC Section**

The SGM71612R81/SGM71612R82/SGM71612R83 family is a CMOS DAC, which is the string architecture with a programmable gain amplifier output buffer. The device has an on-chip 1.25V/2.5V, 10ppm/°C reference.

The output codes of the SGM71612R81/SGM71612R82/SGM71612R83 family are straight binary. The ideal output voltage is given by:

$$V_{OUT} = V_{REFIN} \times \left(\frac{D}{2^N}\right) \times Gain$$

(1)

where:

D = Equal decimal value is 0 to 65,535.

N = 16.

Gain = Output gain setting. (If using the internal reference, Gain = 2. If using the external reference, Gain = 1.)

#### **Internal Reference**

The SGM71612R81Z has an on-chip 1.25V, 10ppm/°C reference. If the internal reference is enabled, it gives a full-scale output of 2.5V.

The SGM71612R82Z, SGM71612R82M and SGM71612R83M have an on-chip 2.5V, 10ppm/°C reference. If the internal reference is enabled, it gives a full-scale output of 5V.

For SGM71612R81/SGM71612R82 family, the internal reference is disabled by default when the chip is powered on, and for SGM71612R83 family, its internal reference is enabled by default when the chip is powered on. The internal reference can be enabled/disabled by setting the control register (see Table 1). When using the internal reference, all channels must be powered down at the same time. The individual channel power-down is not supported if the internal reference is enabled.

#### **Output Amplifier**

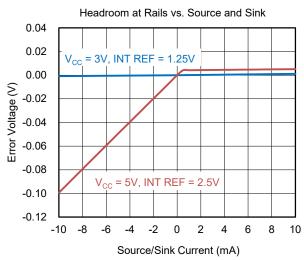

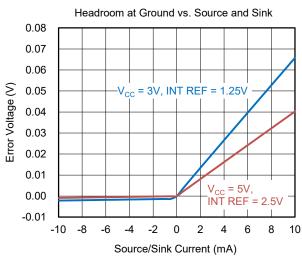

The output buffer amplifier has the rail-to-rail output.

#### **Serial Interface**

The SGM71612R81/SGM71612R82/SGM71612R83 family has a 3-wire SPI-compatible interface.

For the detail operation timing sequence, please see Figure 1 and Figure 2. To prepare a new write sequence, nSYNC must be pulled up at least 15ns before the new write sequence, so that the falling edge of nSYNC can initiate the new write sequence.

**Table 1. Command Definitions**

|    | DB[2 | 7:24] |    | Description                                                        |

|----|------|-------|----|--------------------------------------------------------------------|

| С3 | C2   | C1    | C0 | Description                                                        |

| 0  | 0    | 0     | 0  | Write to input register n                                          |

| 0  | 0    | 0     | 1  | Update DAC register n                                              |

| 0  | 0    | 1     | 0  | Write to input register n, update all (software load DAC function) |

| 0  | 0    | 1     | 1  | Write to and update DAC channel n                                  |

| 0  | 1    | 0     | 0  | Set power-down modes register                                      |

| 0  | 1    | 0     | 1  | Set clear code register                                            |

| 0  | 1    | 1     | 0  | Set nLDAC register                                                 |

| 0  | 1    | 1     | 1  | Reset (power-on reset)                                             |

| 1  | 0    | 0     | 0  | Set internal reference register                                    |

| 1  | 0    | 0     | 1  | Set read enable control register                                   |

| 1  | 0    | 1     | 0  | Reserved                                                           |

| _  | _    | _     | _  | Reserved                                                           |

| 1  | 1    | 1     | 1  | Reserved                                                           |

**Table 2. Address Commands**

|    | DB[2 | 3:20] |    | Selected DAC Channel |

|----|------|-------|----|----------------------|

| A3 | A2   | A1    | A0 | Selected DAC Charmer |

| 0  | 0    | 0     | 0  | DAC A                |

| 0  | 0    | 0     | 1  | DAC B                |

| 0  | 0    | 1     | 0  | DAC C                |

| 0  | 0    | 1     | 1  | DAC D                |

| 0  | 1    | 0     | 0  | DAC E                |

| 0  | 1    | 0     | 1  | DAC F                |

| 0  | 1    | 1     | 0  | DAC G                |

| 0  | 1    | 1     | 1  | DAC H                |

| 1  | 1    | 1     | 1  | All DACs             |

#### Input Shift Register

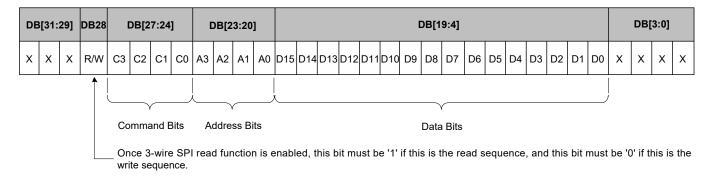

The input shift register is a 32-bit data. The first 3-bit DB[31:29] are Don't care bits. The second bit DB28 is a read or write command bit. The third 4-bit DB[27:24] are command bits C3 to C0 (see Table 1). The meaning of left bits is different from commands.

If C3 to C0 are DAC output data updating associated, the fourth 4-bit DB[23:20] are DAC address bits A3 to A0 (see Table 2). And the following 16-bit DB[19:4] are the DAC data bits. The final 4-bit DB[3:0] are not used data bits (see Figure 4).

If C3 to C0 is command to set the internal reference register, please refer to Table 3 and Table 4.

If C3 to C0 is command to set the power-down modes register, please refer to Table 5, Table 6 and Table 7.

If C3 to C0 is command to set the clear code register, please refer to Table 8 and Table 9.

If C3 to C0 is command to set the nLDAC register, please refer to Table 10 and Table 11.

If C3 to C0 is command to set the read enable control register, please refer to Table 12 and Table 13.

All 32-bit data are locked into the input register on the 32<sup>nd</sup> falling edge of SCLK.

#### nSYNC Interrupt

In a normal write sequence, the nSYNC line must be kept low for at least 32 falling edges of SCLK, and the DAC is updated on the 32<sup>nd</sup> falling edge. However, if nSYNC goes high before the 32<sup>nd</sup> falling edge, this write operation will be invalid and ignored. An example is shown in Figure 5.

**Figure 4. Input Register Contents**

Figure 5. nSYNC Interrupt Facility

#### **Internal Reference Register**

The SGM71612R81/SGM71612R82 family on-chip internal voltage is off by default at power-on, while the SGM71612R83M on-chip internal voltage is on by default at power-on. In Table 1, the command '1000' (C3 to C0) is used to set the internal reference register. Table 3 shows how to enable or disable the internal reference. Table 4 shows the data format for setting the internal reference register.

#### **Power-On Reset**

The SGM71612R81Z and SGM71612R82Z reset to 0V output when the chip is powered up. The SGM71612R82M and SGM71612R83M reset to mid-scale output when the chip is powered up.

There is a software reset that can perform the same DAC reset function. And during the reset, any nLDAC and nCLR operations are invalid.

**Table 3. Internal Reference Register**

| Internal Reference Register (DB0) | Description                                                |

|-----------------------------------|------------------------------------------------------------|

| 0                                 | Reference off (default for SGM71612R81/SGM71612R82 family) |

| 1                                 | Reference on (default for SGM71612R83M only)               |

#### Table 4. 32-Bit Input Shift Register Format for Reference Set-Up Command

MSB LSB

| DB31 to DB29 | DB28 | DB27 | DB26    | DB25       | DB24  | DB23 | DB22 | DB21                     | DB20 | DB19 to DB1 | DB0                         |

|--------------|------|------|---------|------------|-------|------|------|--------------------------|------|-------------|-----------------------------|

| Х            | 0/1  | 1    | 0       | 0          | 0     | Х    | Х    | Х                        | Х    | X           | 1/0                         |

| Don't cares  | W/R  | Com  | mand bi | its (C3 to | o C0) | A    |      | its (A3 to /<br>'t cares | A0)  | Don't cares | Internal reference register |

#### NOTE:

#### **Power-Down Modes**

The SGM71612R81/SGM71612R82/SGM71612R83 family has 3 power-down modes.

Table 5 shows these power-down modes configurations. And the operation data format is shown in Table 6 and Table 7. In Table 6, some or all DACs can be powered down to the selected modes by setting the according bits to '1'. Note that when the internal reference is enabled, the chip only supports all channels powered down at the same time. During power-down, the content of DAC register is retained.

To exit the power-down mode, configure the target DAC channels to normal operation mode.

Table 5. Power-Down Modes Register

| DB9 | DB8 | Operating Mode   |

|-----|-----|------------------|

| 0   | 0   | Normal operation |

| DB9 | DB8 | Power-Down Modes |

| 0   | 1   | 1kΩ to GND       |

| 1   | 0   | 100kΩ to GND     |

| 1   | 1   | Three-state      |

Table 6. 32-Bit Input Shift Register Format for Power-Down/Power-Up Write Operation

MSB LSB

| DB31<br>to<br>DB29 | DB28 | DB27 | DB26    | DB25    | DB24   | DB23 | DB22    | DB21              | DB20 | DB19<br>to<br>DB10 | DB9         | DB8 | DB7      | DB6      | DB5      | DB4      | DB3               | DB2 | DB1      | DB0      |

|--------------------|------|------|---------|---------|--------|------|---------|-------------------|------|--------------------|-------------|-----|----------|----------|----------|----------|-------------------|-----|----------|----------|

| Х                  | 0    | 0    | 1       | 0       | 0      | Х    | X       | X                 | Х    | Х                  | PD1         | PD0 | DAC<br>H | DAC<br>G | DAC<br>F | DAC<br>E | DAC<br>D          |     | DAC<br>B | DAC<br>A |

| Don't cares        | W    | Comm | nand bi | its (C3 | to C0) | Addr | ess bit | s (A3 to<br>cares | A0)  | Don't cares        | Power<br>mo |     | F        | Power-   |          |          | up cha<br>1 to se |     | election | n        |

#### NOTE:

1. Once 3-wire SPI read function is enabled, DB28 = '0' represents that this is a write sequence, and DB28 = '1' represents that this is a read sequence. Otherwise, 3-wire SPI read function is disabled (default), DB28 will be ignored.

Table 7. 32-Bit Input Shift Register Format for Power-Down/Power-Up Read Operation

| MSB                |      |      |         |          |       |      |                    |                   |      |                    |      |      |      |      |      |      |         |        |         |          |        |      |      |      |      | LSB  |

|--------------------|------|------|---------|----------|-------|------|--------------------|-------------------|------|--------------------|------|------|------|------|------|------|---------|--------|---------|----------|--------|------|------|------|------|------|

| DB31<br>to<br>DB29 | DB28 | DB27 | DB26    | DB25     | DB24  | DB23 | DB22               | DB21              | DB20 | DB19<br>to<br>DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9     | DB8    | DB7     | DB6      | DB5    | DB4  | DB3  | DB2  | DB1  | DB0  |

| Х                  | 1    | 0    | 1       | 0        | 0     | Х    | х                  | х                 | х    | 0000               | PDH1 | PDH0 | PDG1 | PDG0 | PDF1 | PDF0 | PDE1    | PDE0   | PDD1    | PDD0     | PDC1   | PDC0 | PDB1 | PDB0 | PDA1 | PDA0 |

| Don't cares        | R    | Comr | mand bi | ts (C3 t | o C0) | Add  | ress bits<br>Don't | s (A3 to<br>cares | A0)  |                    |      |      |      |      |      | Powe | r-down/ | power- | up char | nnel sel | ection |      |      |      |      |      |

#### NOTE:

#### **Clear Code Register**

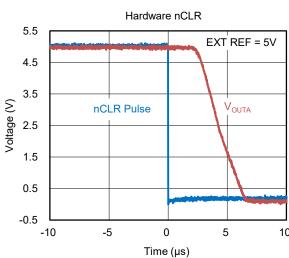

The outputs of the SGM71612R81/SGM71612R82/SGM71612R83 family can be cleared asynchronously by hardware pin nCLR. The nCLR is active low and the falling edge is sensitive. If the nCLR pin goes from high to low, the chip clears the input register and resets DAC register to the users' configured data that is set in clear code register. And the chip resets the output according to the setting of clear code register at the same time.

The nCLR pin can be used to set the DAC register and output asynchronously. The nCLR status is set in clear code register (see Table 8).

To set clear code register, please refer to command format in Table 9.

When the nCLR pin is hold high, a full valid write operation can call the chip to exit the clear code mode. In the operation sequence, the part quits the clear code mode on the 32<sup>nd</sup> falling edge of SCLK.

It will take the chip about 300ns to start changing the output from receiving the nCLR falling edge. More details please refer to Electrical Characteristics tables.

Table 8. Clear Code Register

| CR1 (DB1) | CR0 (DB0) | Clears to Code   |

|-----------|-----------|------------------|

| 0         | 0         | 0x0000 (default) |

| 0         | 1         | 0x8000           |

| 1         | 0         | 0xFFFF           |

| 1         | 1         | No operation     |

Table 9. 32-Bit Input Shift Register Format for Clear Code Operation

MSB LSB

| DB31<br>to<br>DB29 | DB28 | DB27 | DB26     | DB25        | DB24 | DB23 | DB22                | DB21                | DB20 | DB19<br>to<br>DB2 | DB1       | DB0        |

|--------------------|------|------|----------|-------------|------|------|---------------------|---------------------|------|-------------------|-----------|------------|

| Х                  | 0/1  | 0    | 1        | 0           | 1    | Х    | Х                   | Х                   | Х    | Х                 | CR1       | CR0        |

| Don't cares        | W/R  | Со   | mmand bi | ts (C3 to 0 | CO)  | А    | ddress bit<br>Don't | s (A3 to A<br>cares | 0)   | Don't cares       | Clear cod | e register |

#### NOTE:

#### **nLDAC** Function

There are two ways of updating DAC output by using hardware nLDAC pin.

The first way is that the nLDAC pin can be tied or kept low for a while (specified in Figure 1), after a full write command performing, the DAC is updated on the 32<sup>nd</sup> falling edge of SCLK.

The second way is that the nLDAC is kept high during the 32-bit write sequence, then a pulse of nLDAC is given (see Figure 1), the DAC output is updated asynchronously.

There are also software ways to control DAC updating, which is equal to nLDAC pin operation. Please refer to Table 10 and Table 11.

In Table 11, when according DAC channel bit is set to '0', the DAC output load mode is determined by nLDAC pin operation. When according DAC channel bit is set to '1', it is equal to the nLDAC pin connected to low, and the DAC is updated on the 32<sup>nd</sup> falling edge of SCLK.

Table 10. nLDAC Register

| Load DAC Reg            | jister       | nLDAC Operation                                                                              |

|-------------------------|--------------|----------------------------------------------------------------------------------------------|

| nLDAC Bits (DB7 to DB0) | nLDAC Pin    | ILDAC Operation                                                                              |

| 0                       | 1/0          | DAC update determined by nLDAC hardware pin operation                                        |

| 1                       | X—Don't care | DAC channels update, regardless the nLDAC pin. It is equal to the nLDAC pin connected to '0' |

Table 11. 32-Bit Input Shift Register Format for nLDAC Operation

MSB LSB

| DB31<br>to<br>DB29 | DB28 | DB27 | DB26    | DB25     | DB24  | DB23 | DB22                | DB21 | DB20 | DB19<br>to<br>DB8 | DB7      | DB6        | DB5      | DB4      | DB3      | DB2      | DB1      | DB0      |

|--------------------|------|------|---------|----------|-------|------|---------------------|------|------|-------------------|----------|------------|----------|----------|----------|----------|----------|----------|

| Х                  | 0/1  | 0    | 1       | 1        | 0     | Х    | Х                   | Х    | Х    | Х                 | DAC<br>H | DAC<br>G   | DAC<br>F | DAC<br>E | DAC<br>D | DAC<br>C | DAC<br>B | DAC<br>A |

| Don't cares        | W/R  | Comr | nand bi | ts (C3 t | o C0) | Add  | lress bits<br>Don't | `    | A0)  | Don't cares       | If set   | to '1', re | gardles  | s of har | dware r  | nLDAC    | pin ope  | ration.  |

#### NOTE:

#### 3-Wire SPI Read Function

The SGM71612R81/SGM71612R82/SGM71612R83 family supports 3-wire SPI read function. This function is valid when the control bit of the read control register is set to '1', and this function is disabled when the control bit of the read control register is set to '0'. Once the read function is enabled, the DB28 bit of every 32-bit reading data stream must be '1' to tell

DAC that this is a read operation. The detailed sequence of the read operation is shown in Figure 2. Correspondingly, once the read function is enabled, the DB28 bit of every 32-bit writing data stream must be '0' to tell DAC that this is a write operation, and the detailed sequence of the write operation is shown in Figure 1.

Table 12. Read Enable Control Register

| Internal Read Enable Control Register (DB0) | Description                                |

|---------------------------------------------|--------------------------------------------|

| 0                                           | Disable 3-wire SPI read function (default) |

| 1                                           | Enable 3-wire SPI read function            |

#### Table 13. 32-Bit Input Shift Register Format for Read Enable Control Register Set-Up Command

MSB LSB

| DB31 to DB29 | DB28 | DB27 | DB26   | DB25       | DB24  | DB23 | DB22 | DB21                     | DB20 | DB19 to DB1 | DB0                                   |

|--------------|------|------|--------|------------|-------|------|------|--------------------------|------|-------------|---------------------------------------|

| Х            | 0/1  | 1    | 0      | 0          | 1     | Х    | Х    | Х                        | Х    | X           | 1/0                                   |

| Don't cares  | W/R  | Com  | mand b | its (C3 to | o C0) | Α    |      | its (A3 to a<br>'t cares | A0)  | Don't cares | Internal read enable control register |

#### NOTE:

1. Once 3-wire SPI read function is enabled, DB28 = '0' represents that this is a write sequence, and DB28 = '1' represents that this is a read sequence. Otherwise, 3-wire SPI read function is disabled (default), DB28 will be ignored.

#### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| APRIL 2024 – REV.A.1 to REV.A.2                 | Page   |

|-------------------------------------------------|--------|

| Updated Tape and Reel Information section       | 31, 32 |

| OCTOBER 2023 – REV.A to REV.A.1                 | Page   |

| Updated Package/Ordering Information section    | 2, 3   |

| Changes from Original (SEPTEMBER 2023) to REV.A | Page   |

| Changed from product preview to production data | All    |

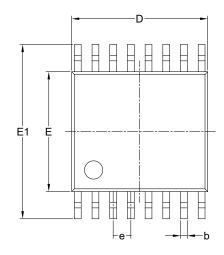

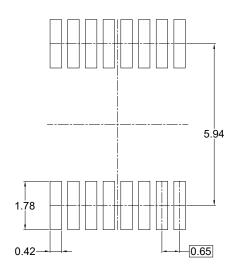

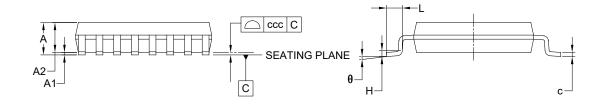

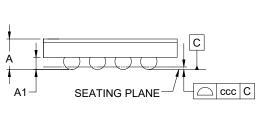

# PACKAGE OUTLINE DIMENSIONS TSSOP-16

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions In Millimeters |     |       |  |  |  |

|--------|---------------------------|-----|-------|--|--|--|

|        | MIN                       | MOD | MAX   |  |  |  |

| Α      | -                         | -   | 1.200 |  |  |  |

| A1     | 0.050                     | -   | 0.150 |  |  |  |

| A2     | 0.800                     | -   | 1.050 |  |  |  |

| b      | 0.190                     | -   | 0.300 |  |  |  |

| С      | 0.090                     | -   | 0.200 |  |  |  |

| D      | 4.860                     | -   | 5.100 |  |  |  |

| E      | 4.300                     | -   | 4.500 |  |  |  |

| E1     | 6.200                     | -   | 6.600 |  |  |  |

| е      | 0.650 BSC                 |     |       |  |  |  |

| L      | 0.450                     | -   | 0.750 |  |  |  |

| Н      | 0.250 TYP                 |     |       |  |  |  |

| θ      | 0°                        | -   | 8°    |  |  |  |

| ccc    | 0.100                     |     |       |  |  |  |

#### NOTES:

- 1. This drawing is subject to change without notice.

- 2. The dimensions do not include mold flashes, protrusions or gate burrs.

- 3. Reference JEDEC MO-153.

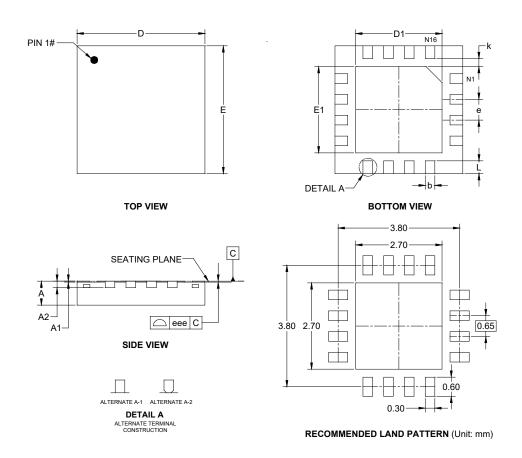

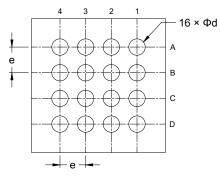

# PACKAGE OUTLINE DIMENSIONS TQFN-4×4-16BL

| Symbol | Dimensions In Millimeters |               |       |  |  |  |

|--------|---------------------------|---------------|-------|--|--|--|

|        | MIN                       | MOD           | MAX   |  |  |  |

| Α      | 0.700                     | -             | 0.800 |  |  |  |

| A1     | 0.000                     | -             | 0.050 |  |  |  |

| A2     | 0.203 REF                 |               |       |  |  |  |

| b      | 0.250                     | -             | 0.350 |  |  |  |

| D      | 3.900                     | -             | 4.100 |  |  |  |

| E      | 3.900                     | -             | 4.100 |  |  |  |

| D1     | 2.600                     | 2.700         | 2.800 |  |  |  |

| E1     | 2.600                     | 0 2.700 2.800 |       |  |  |  |

| е      | 0.650 BSC                 |               |       |  |  |  |

| k      | 0.250 REF                 |               |       |  |  |  |

| L      | 0.300                     | - 0.500       |       |  |  |  |

| eee    | 0.080                     |               |       |  |  |  |

NOTE: This drawing is subject to change without notice.

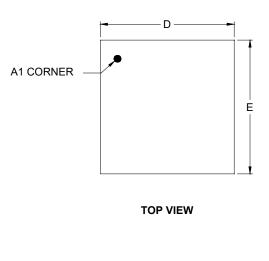

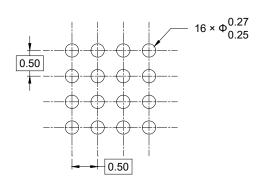

# PACKAGE OUTLINE DIMENSIONS FOCSP-2.6×2.6-16B

RECOMMENDED LAND PATTERN (Unit: mm)

SIDE VIEW

**BOTTOM VIEW**

| Symbol | Dimensions In Millimeters |     |       |  |  |  |

|--------|---------------------------|-----|-------|--|--|--|

|        | MIN                       | MOD | MAX   |  |  |  |

| Α      | -                         | -   | 0.628 |  |  |  |

| A1     | 0.216                     | -   | 0.256 |  |  |  |

| D      | 2.575                     | -   | 2.635 |  |  |  |

| E      | 2.575                     | -   | 2.635 |  |  |  |

| d      | 0.289 - 0.349             |     |       |  |  |  |

| е      | 0.500 BSC                 |     |       |  |  |  |

| ccc    | 0.050                     |     |       |  |  |  |

NOTE: This drawing is subject to change without notice.

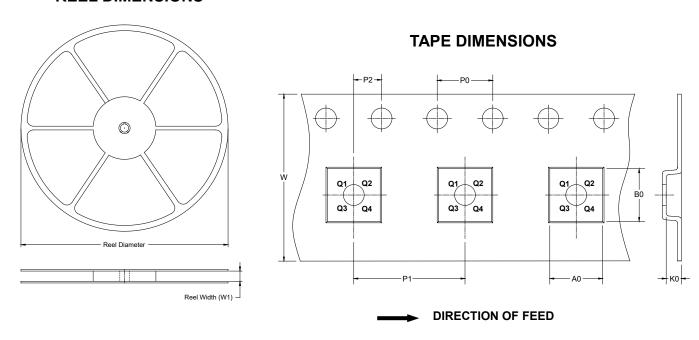

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type      | Reel<br>Diameter | MPQ  | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------|------------------|------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TSSOP-16          | 13"              | 4000 | 12.4                     | 6.80       | 5.40       | 1.50       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| TSSOP-16          | 13"              | 250  | 12.4                     | 6.80       | 5.40       | 1.50       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| TQFN-4×4-16BL     | 13"              | 3000 | 12.4                     | 4.30       | 4.30       | 1.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q2               |

| TQFN-4×4-16BL     | 13"              | 250  | 12.4                     | 4.30       | 4.30       | 1.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q2               |

| FOCSP-2.6×2.6-16B | 13"              | 5000 | 12.4                     | 2.72       | 2.72       | 0.70       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| FOCSP-2.6×2.6-16B | 7"               | 250  | 12.4                     | 2.72       | 2.72       | 0.70       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

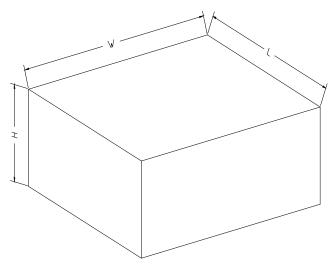

#### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-------------|----------------|---------------|----------------|--------------|

| 7" (Option) | 368            | 227           | 224            | 8            |

| 7"          | 442            | 410           | 224            | 18           |

| 13"         | 386            | 280           | 370            | 5            |