# SGM41295S DC Bias Controller for EML

# **GENERAL DESCRIPTION**

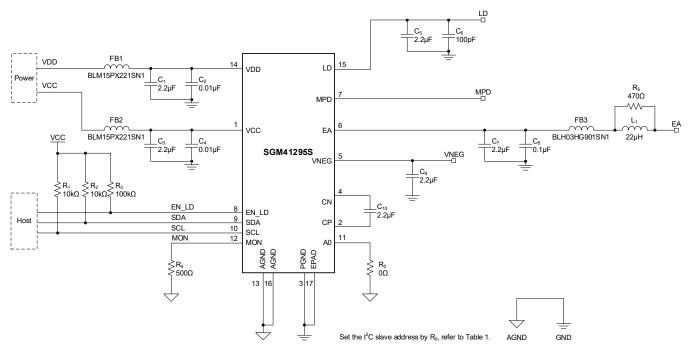

The SGM41295S provides DC bias for the laser diode, EA bias, and MPD bias monitor circuits, and it also provides an unregulated negative output generated by an inverting charge pump which is equal to negative input voltage.

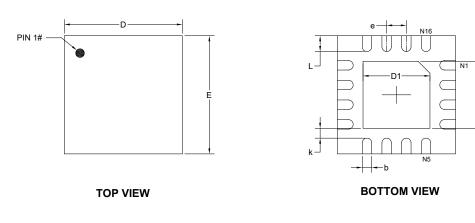

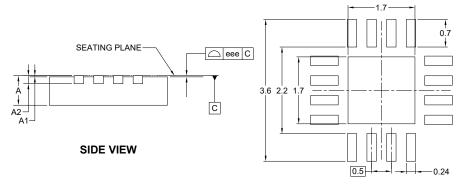

The SGM41295S is available in a Green TQFN- $3\times3-16L$  package. It operates over an ambient temperature range of  $-40^{\circ}C$  to  $+105^{\circ}C$ .

# **APPLICATIONS**

EML Fiber Modules

AOC and Transponders for Telecom and Data Center Interconnection

# FEATURES

- Negative Charge Pump Output (-1×) with 150mA Maximum Loading Current

- Digitally Programmable EAM Bias and LD Driving Current Source

- Voltage Sources for EAM Bias (-0.2V to -3.2V, 12.5mV/Step) with 100mA Maximum Loading Current

- Current Sources for LD (0mA to 239.5mA, 0.5mA/Step or 0mA to 119.75mA, 0.25mA/Step)

- Backside MPD Current Monitoring (0mA to 10mA)

- Support I<sup>2</sup>C Interface and up to 1MHz I<sup>2</sup>C Clock Frequency

- No Inrush Current during Startup

- Charge Pump Output Short Protection

- LD Short/Open and EAM Short Monitoring

- +140°C Over-Temperature Alert Bit

- +160°C Over-Temperature Shutdown

- Available in a Green TQFN-3×3-16L Package

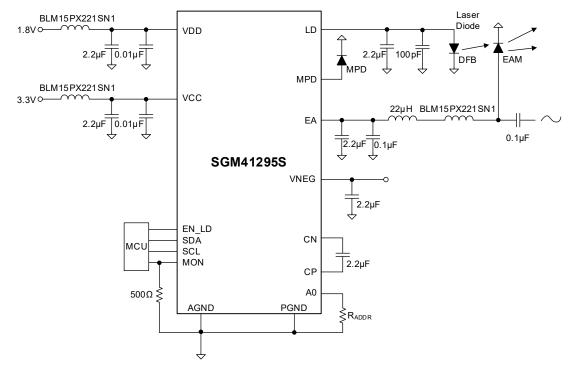

# TYPICAL APPLICATION

Figure 1. Typical Application Circuit

# **DC Bias Controller for EML**

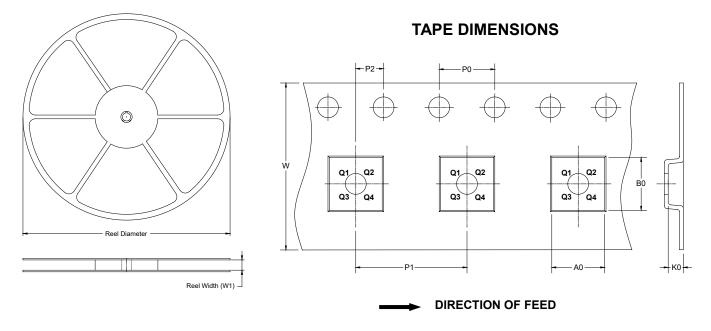

### **PACKAGE/ORDERING INFORMATION**

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM41295S | TQFN-3×3-16L           | -40°C to +105°C                   | SGM41295SGTQ16G/TR | 0LBTQ<br>XXXXX     | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

| XXXX |             |

|------|-------------|

|      | Vendor Code |

|      |             |

Х

Trace Code

— Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , V <sub>DD</sub> , SDA, SCL | 0.3V to 6V                              |

|----------------------------------------------|-----------------------------------------|

| V <sub>NEG</sub>                             | 6V to 0.3V                              |

| MON, V <sub>CP</sub> , EN_LD, A0             | 0.3V to V <sub>CC</sub> + 0.3V          |

| MPD, V <sub>EA</sub> , V <sub>CN</sub>       | $\dots$ V <sub>NEG</sub> - 0.3V to 0.3V |

| LD                                           | 0.3V to V <sub>DD</sub> + 0.3V          |

| Package Thermal Resistance                   |                                         |

| TQFN-3×3-16L, θ <sub>JA</sub>                | 39.9°C/W                                |

| TQFN-3×3-16L, θ <sub>JB</sub>                | 13.8°C/W                                |

| TQFN-3×3-16L, θ <sub>JC (TOP)</sub>          | 42.5°C/W                                |

| TQFN-3×3-16L, θ <sub>JC (BOT)</sub>          |                                         |

| Junction Temperature                         | +150°C                                  |

| Storage Temperature Range                    | 65°C to +150°C                          |

| Lead Temperature (Soldering, 10s)            | +260°C                                  |

| ESD Susceptibility <sup>(1) (2)</sup>        |                                         |

| НВМ                                          | ±2000V                                  |

| CDM                                          | ±1000V                                  |

#### NOTES:

1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### **RECOMMENDED OPERATING CONDITIONS**

| V <sub>CC</sub>                      | 2.85V to 5.5V  |

|--------------------------------------|----------------|

| V <sub>DD</sub>                      | 1.5V to 5.5V   |

| MON Current Output Range             | 0mA to 10mA    |

| MON Voltage Output Range             | 0V to 3.3V     |

| SCL, SDA Pull-Up Voltage             | 2.5V (MIN)     |

| Operating Junction Temperature Range | 40°C to +125°C |

| Operating Ambient Temperature Range  | 40°C to +105°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

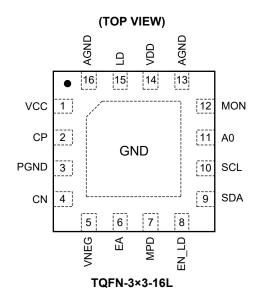

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN    | NAME           | TYPE | FUNCTION                                                                                                                              |

|--------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VCC            | Ρ    | Power Supply for the Chip.                                                                                                            |

| 2      | СР             | I/O  | Fly Capacitor Positive Connection.                                                                                                    |

| 3      | PGND           | G    | Power Ground.                                                                                                                         |

| 4      | CN             | I/O  | Fly Capacitor Negative Connection.                                                                                                    |

| 5      | VNEG           | 0    | Charge Pump Output.                                                                                                                   |

| 6      | EA             | 0    | EAM Biasing Output. The output voltage of EA is programmable via the I <sup>2</sup> C interface.                                      |

| 7      | MPD            | Ι    | MPD Current Monitor Input. Cathode of MPD is connected to ground and anode of MPD is connected to this pin.                           |

| 8      | EN_LD          | Ι    | Laser Bias Enable. Logic low disables the laser bias only (not EAM bias). Logic high enables the laser bias. Don't leave it floating. |

| 9      | SDA            | 10   | Data for the I <sup>2</sup> C Compatible Interface.                                                                                   |

| 10     | SCL            | ю    | Clock for the I <sup>2</sup> C Compatible Interface.                                                                                  |

| 11     | A0             | 0    | Slave Address Programming. To program the address, a resistor is connected between this pin and ground.                               |

| 12     | MON            | 0    | Multiplexed Monitor Output. There are three monitor signals selected via I <sup>2</sup> C interface.                                  |

| 13, 16 | AGND           | G    | Analog Ground.                                                                                                                        |

| 14     | VDD            | Р    | Power Supply for Laser Diode Current Source.                                                                                          |

| 15     | LD             | 0    | Laser Biasing Output. The current of LD is programmable via the I <sup>2</sup> C interface.                                           |

| -      | Exposed<br>Pad | G    | Exposed Pad. Used for circuit ground connection.                                                                                      |

NOTE: I: input, O: output, I/O: input or output, G: ground, P: power for the circuit.

# **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = 3.3V, V<sub>DD</sub> = 1.8V, Full = -40°C to +105°C, typical values are at  $T_J$  = +25°C, unless otherwise noted.)

| PARAMETERS                                      | SYMBOL                         | CONDITIONS                                                                                                              | TEMP  | MIN                     | ТҮР   | MAX  | UNITS                |

|-------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|-------------------------|-------|------|----------------------|

| Power Supply                                    |                                |                                                                                                                         |       |                         |       |      |                      |

| Supply Voltage Range                            | Vcc                            |                                                                                                                         | Full  | 2.85                    |       | 5.5  | V                    |

|                                                 | V <sub>UVLO_R</sub>            | V <sub>cc</sub> rising                                                                                                  | +25°C | 2.55                    | 2.65  | 2.75 |                      |

| V <sub>cc</sub> Under-Voltage Lockout Threshold | $V_{\text{UVLO}_F}$            | V <sub>cc</sub> falling                                                                                                 | +25°C |                         | 2.5   |      | - V                  |

| Power-Up Blanking Time                          | t <sub>BLANK</sub>             |                                                                                                                         | +25°C |                         | 10    |      | ms                   |

| Operating Quiescent Current                     | lα                             | I <sub>LD</sub> and EA disabled, no switching (test mode)                                                               | +25°C |                         | 100   | 150  | μA                   |

| LD Current Source                               |                                |                                                                                                                         |       |                         |       |      |                      |

| Maximum Output Current                          | I <sub>LD_MAX</sub>            | V <sub>LD</sub> = 1.5V                                                                                                  | +25°C |                         | 239.5 |      | mA                   |

| Current Programming Resolution                  | I <sub>RES_MAX</sub>           | V <sub>LD</sub> = 1.5V, LD current gain = 1,<br>8-bit DAC programming<br>V <sub>LD</sub> = 1.5V, LD current gain = 1/2, | +25°C | 0.1                     | 0.5   | 0.9  | - mA                 |

|                                                 |                                | 8-bit DAC programming                                                                                                   | +25°C | 0.05                    | 0.25  | 0.45 |                      |

| LD Current Source Accuracy                      |                                | $V_{LD}$ = 1.5V, $I_{LD}$ = 100mA<br>$V_{LD}$ = 1.5V, $I_{LD}$ = 100mA, 10Hz to                                         | +25℃  | -3                      |       | 3    | %                    |

| LD Current Source Noise                         | I <sub>NOISE</sub>             | $v_{LD} = 1.5v, i_{LD} = 100mA, 10HZ to 10kHz$                                                                          | +25°C |                         | 2.8   |      | $\mu A_{\text{RMS}}$ |

| LD Current Source Output DC Impedance           |                                | $V_{LD}$ = 1.2V to 1.5V, $I_{LD}$ = 100mA                                                                               | +25℃  |                         | 10    |      | kΩ                   |

| LD Current Source Full Temperature Drift        |                                | I <sub>LD</sub> = 100mA                                                                                                 | Full  |                         | 13    |      | µA/°C                |

| LD Current Source Headroom Voltage              | $V_{\text{LD}\_\text{ROOM}}$   | $V_{DD}$ = 1.8V, $I_{LD}$ = 200mA                                                                                       | +25°C |                         | 0.15  | 0.26 | V                    |

| LD Current Source Soft-Start Time               | t <sub>ss_LD</sub>             | V <sub>DD</sub> = 1.8V, I <sub>LD</sub> = 239.5mA                                                                       | +25°C |                         | 280   | 500  | μs                   |

| LD Current Source Open Detection Threshold      | $V_{LD\_OPEN}$                 | $V_{DD}$ - $V_{LD}$ falling                                                                                             | +25℃  |                         | 50    |      | mV                   |

| LD Current Source Short Detection Threshold     | $V_{\text{SHORT\_LD}}$         | V <sub>LD</sub> falling                                                                                                 | +25°C | 0.55                    | 0.6   | 0.65 | V                    |

| EAM Negative Voltage Bias                       |                                |                                                                                                                         |       |                         |       |      |                      |

| EA Output Voltage Range                         | V <sub>EA</sub>                | 8-bit DAC programming                                                                                                   | Full  | V <sub>NEG</sub> + 0.25 |       | -0.2 | V                    |

| EA Output Voltage DAC Accuracy                  |                                | V <sub>EA</sub> = -2V                                                                                                   | +25°C | -1                      |       | 1    | %                    |

| Voltage Difference between EA and VNEG          |                                |                                                                                                                         | Full  | 0.25                    |       | 4    | V                    |

| EA Output Voltage DAC Resolution                |                                |                                                                                                                         | +25°C | 0                       | 12.5  | 25   | mV                   |

| EA Output Voltage Full Temperature Drift        |                                | $V_{EA} = -2V$                                                                                                          | Full  |                         | 34    |      | µV/°C                |

| EA Maximum Output Current                       | $I_{EA_{MAX}}$                 |                                                                                                                         | +25°C | 100                     |       |      | mA                   |

| EA Noise                                        | V <sub>NOISE</sub>             | V <sub>EA</sub> = -2V, I <sub>EA</sub> = 50mA, 10Hz to<br>10kHz                                                         | +25°C |                         | 70    |      | $\mu V_{\text{RMS}}$ |

| EA Short Detection Threshold                    | $V_{\text{SHORT}\_\text{EAM}}$ | V <sub>EA</sub> rising                                                                                                  | +25°C |                         | -100  |      | mV                   |

| EA DC Impedance                                 |                                | $V_{EA}$ = -2V, $I_{EA}$ = 0mA to 100mA                                                                                 | +25℃  |                         | 0.05  |      | Ω                    |

| EA Voltage Change Slew Rate                     |                                |                                                                                                                         | +25°C |                         | 3.1   |      | mV/µs                |

| Negative Charge Pump                            |                                |                                                                                                                         |       |                         |       |      |                      |

| Switching Frequency                             | fs                             | I <sub>OUT</sub> = 100mA                                                                                                | +25°C |                         | 2     |      | MHz                  |

| Maximum Load Current                            | I <sub>NEG_MAX</sub>           |                                                                                                                         | +25°C | 150                     |       |      | mA                   |

| Output Impedance                                |                                | I <sub>OUT</sub> = 100mA                                                                                                | +25°C |                         | 1.9   |      | Ω                    |

| MPD Pin                                         |                                |                                                                                                                         |       |                         |       |      |                      |

| Current Range                                   |                                |                                                                                                                         | +25°C | 0                       |       | 10   | mA                   |

| Voltage Range                                   |                                |                                                                                                                         | +25°C | V <sub>NEG</sub> + 1    |       | 0    | V                    |

# **DC Bias Controller for EML**

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 3.3V, V_{DD} = 1.8V, Full = -40^{\circ}C$  to +105°C, typical values are at T<sub>J</sub> = +25°C, unless otherwise noted.)

| PARAMETERS                                                                   | SYMBOL                | CONDITIONS                                       | TEMP       | MIN   | TYP   | MAX | UNITS                |

|------------------------------------------------------------------------------|-----------------------|--------------------------------------------------|------------|-------|-------|-----|----------------------|

| Multiplexed Monitor Output<br>(EA current sampling ratio 40:1 or 20:1. LD vo | ltage sampli          | ng ratio 2.1 TX MPD current samp                 | ling ratio | 1·1 ) |       |     |                      |

|                                                                              |                       | $I_{EA} = 60 \text{mA}$ , sampling ratio = 40:1  |            | -5    |       | 5   |                      |

|                                                                              |                       | I <sub>EA</sub> = 60mA, sampling ratio = 20:1    | +25°C      | -5    |       | 5   | -                    |

| MON Pin Current Accuracy                                                     |                       | I <sub>MPD</sub> = 3mA                           | +25°C      | -5    |       | 5   | %                    |

|                                                                              |                       | I <sub>MPD</sub> = 10mA                          | +25°C      | -5    |       | 5   |                      |

|                                                                              |                       | I <sub>MPD</sub> = 250μA (1:8)                   | +25°C      | -5    |       | 5   |                      |

|                                                                              |                       | I <sub>EA</sub> = 60mA, sampling ratio = 40:1    | Full       | -1    |       | 1   |                      |

|                                                                              |                       | I <sub>EA</sub> = 60mA, sampling ratio = 20:1    | Full       | -1    |       | 1   |                      |

| MON Pin Current Full Temperature Drift                                       |                       | I <sub>MPD</sub> = 3mA                           | Full       | -0.5  |       | 0.5 | %                    |

|                                                                              |                       | I <sub>MPD</sub> = 10mA                          | Full       | -0.5  |       | 0.5 |                      |

|                                                                              |                       | I <sub>MPD</sub> = 250μA (1:8)                   | Full       | -0.5  |       | 0.5 |                      |

|                                                                              |                       | I <sub>EA</sub> = 60mA, sampling ratio = 40:1    | +25°C      |       | 0.015 |     |                      |

| MON Pin Current Noise                                                        |                       | I <sub>EA</sub> = 60mA, sampling ratio = 20:1    | +25°C      |       | 0.025 |     | $\mu A_{\text{RMS}}$ |

|                                                                              |                       | I <sub>MPD</sub> = 3mA                           | +25°C      |       | 0.03  |     |                      |

| MON Pin Leakage Current                                                      | I <sub>MON_LEAK</sub> | Monitor function disabled, forcing 1V on MON pin | +25°C      |       | 0.01  | 0.2 | μA                   |

| Logic EN_LD, SDA, SCL                                                        |                       |                                                  |            |       |       |     |                      |

| Input High Threshold                                                         | VIH                   |                                                  | Full       | 2.2   |       |     | V                    |

| Input Low Threshold                                                          | VIL                   |                                                  | Full       |       |       | 0.8 | V                    |

| Output Low Voltage                                                           | V <sub>OL</sub>       | I <sub>SINK</sub> = 200μA                        | Full       |       |       | 0.4 | V                    |

| Thermal Detection                                                            |                       |                                                  |            |       |       |     |                      |

| Thermal Alert Threshold                                                      |                       |                                                  |            |       | 140   |     | °C                   |

| Thermal Shutdown Threshold                                                   |                       |                                                  |            |       | 160   |     | °C                   |

| Thermal Shutdown Hysteresis                                                  |                       |                                                  |            |       | 20    |     | °C                   |

# I<sup>2</sup>C INTERFACE TIMING CHARACTERISTICS (1)

| PARAMETER                                                                             | SYMBOL              | CONDITIONS     | TEMP  | MIN                    | TYP | MAX  | UNITS |

|---------------------------------------------------------------------------------------|---------------------|----------------|-------|------------------------|-----|------|-------|

|                                                                                       |                     | Standard mode  | +25°C |                        |     | 100  | kHz   |

| SCL Clock Frequency                                                                   | f <sub>SCL</sub>    | Fast mode      | +25°C |                        |     | 400  | kHz   |

|                                                                                       |                     | Fast mode plus | +25°C |                        |     | 1    | MHz   |

|                                                                                       |                     | Standard mode  | +25°C | 4.7                    |     |      | μs    |

| LOW Period of the SCL Clock                                                           | t <sub>LOW</sub>    | Fast mode      | +25°C | 1.3                    |     |      | μs    |

|                                                                                       |                     | Fast mode plus | +25°C | 0.5                    |     |      | μs    |

|                                                                                       |                     | Standard mode  | +25°C | 4.0                    |     |      | μs    |

| HIGH Period of the SCL Clock                                                          | t <sub>HIGH</sub>   | Fast mode      | +25°C | 600                    |     |      | ns    |

|                                                                                       |                     | Fast mode plus | +25°C | 260                    |     |      | ns    |

|                                                                                       |                     | Standard mode  | +25°C | 4.7                    |     |      | μs    |

| Bus Free Time between a STOP and a START Conditions                                   | t <sub>BUF</sub>    | Fast mode      | +25°C | 1.3                    |     |      | μs    |

|                                                                                       |                     | Fast mode plus | +25°C | 0.5                    |     |      | μs    |

|                                                                                       |                     | Standard mode  | +25°C | 4.0                    |     |      | μs    |

| Hold Time for a Repeated START Condition                                              | t <sub>hd;STA</sub> | Fast mode      | +25°C | 600                    |     |      | ns    |

|                                                                                       |                     | Fast mode plus | +25°C | 260                    |     |      | ns    |

|                                                                                       |                     | Standard mode  | +25°C | 4.7                    |     |      | μs    |

| Setup Time for a Repeated START Condition                                             | t <sub>su;STA</sub> | Fast mode      | +25°C | 600                    |     |      | ns    |

|                                                                                       |                     | Fast mode plus | +25°C | 260                    |     |      | ns    |

|                                                                                       |                     | Standard mode  | +25°C | 250                    |     |      | ns    |

| Data Setup Time                                                                       | t <sub>su;DAT</sub> | Fast mode      | +25°C | 100                    |     |      | ns    |

|                                                                                       |                     | Fast mode plus | +25°C | 50                     |     |      | ns    |

|                                                                                       |                     | Standard mode  | +25°C | 0.05                   |     | 3.45 | μs    |

| Data Hold Time                                                                        | t <sub>hd;DAT</sub> | Fast mode      | +25°C | 0.05                   |     | 0.9  | μs    |

|                                                                                       |                     | Fast mode plus | +25°C | 0                      |     | 0.33 | μs    |

|                                                                                       |                     | Standard mode  | +25°C | 20 + 0.1C <sub>B</sub> |     | 1000 | ns    |

| Rise Time of SCL Signal after a Repeated START Condition and after an Acknowledge Bit | t <sub>RCL1</sub>   | Fast mode      | +25°C | 20 + 0.1C <sub>B</sub> |     | 1000 | ns    |

|                                                                                       |                     | Fast mode plus | +25°C | 10                     |     | 120  | ns    |

|                                                                                       |                     | Standard mode  | +25°C | 20 + 0.1C <sub>B</sub> |     | 1000 | ns    |

| Rise Time of SCL Signal                                                               | t <sub>RCL</sub>    | Fast mode      | +25°C | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |

| -                                                                                     |                     | Fast mode plus | +25°C | 10                     |     | 120  | ns    |

|                                                                                       |                     | Standard mode  | +25°C | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |

| Fall Time of SCL Signal                                                               | t <sub>FCL</sub>    | Fast mode      | +25°C | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |

|                                                                                       |                     | Fast mode plus | +25°C | 10                     |     | 120  | ns    |

|                                                                                       |                     | Standard mode  | +25°C | 20 + 0.1C <sub>B</sub> |     | 1000 | ns    |

| Rise Time of SDA Signal                                                               | t <sub>RDA</sub>    | Fast mode      | +25°C | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |

|                                                                                       |                     | Fast mode plus | +25°C | 10                     |     | 120  | ns    |

|                                                                                       |                     | Standard mode  | +25°C | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |

| Fall Time of SDA Signal                                                               | t <sub>FDA</sub>    | Fast mode      | +25°C | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |

|                                                                                       |                     |                |       |                        |     |      |       |

# I<sup>2</sup>C INTERFACE TIMING CHARACTERISTICS <sup>(1)</sup> (continued)

| PARAMETER                       | SYMBOL              | SYMBOL CONDITIONS TEMP MIN |       |     |  | MAX | UNITS |

|---------------------------------|---------------------|----------------------------|-------|-----|--|-----|-------|

|                                 |                     | Standard mode              | +25°C | 4.0 |  |     | μs    |

| Setup Time for STOP Condition   | t <sub>su;STO</sub> | Fast mode                  | +25°C | 600 |  |     | ns    |

|                                 |                     | Fast mode plus             | +25°C | 260 |  |     | ns    |

|                                 |                     | Standard mode              | +25°C |     |  | 0.4 |       |

| Capacitive Load for SDA and SCL | C <sub>B</sub>      | Fast mode                  | +25°C |     |  | 0.2 | nF    |

|                                 |                     | Fast mode plus             | +25°C |     |  | 0.1 |       |

#### NOTE:

1. Industry standard I<sup>2</sup>C timing characteristics according to I<sup>2</sup>C-Bus Specification. Not tested in production.

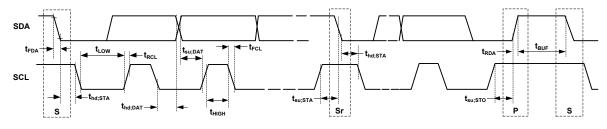

# I<sup>2</sup>C INTERFACE TIMING DIAGRAM

Figure 2. Serial Interface Timing for F/S-Mode

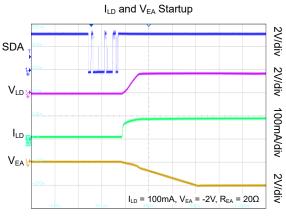

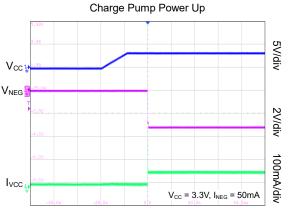

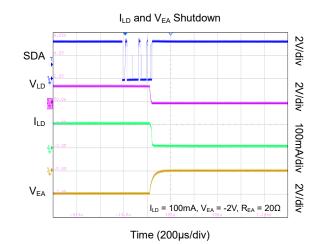

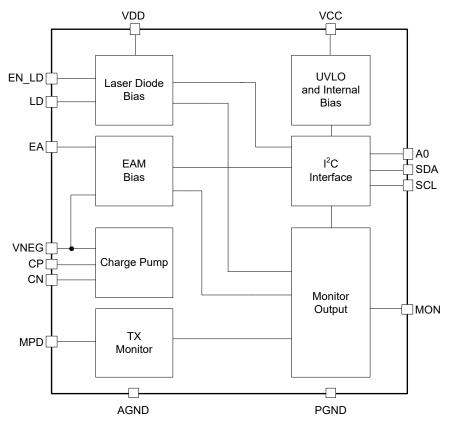

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_J$  = +25°C,  $V_{CC}$  = 3.3V,  $V_{DD}$  = 1.8V, unless otherwise noted.

Time (200µs/div)

Time (10ms/div)

Charge Pump and V<sub>EA</sub> Ripple  $V_{NEG}$   $V_{EA}$   $V_{EA}$

Time (500ns/div)

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_J$  = +25°C,  $V_{CC}$  = 3.3V,  $V_{DD}$  = 1.8V, unless otherwise noted.

# SGM41295S

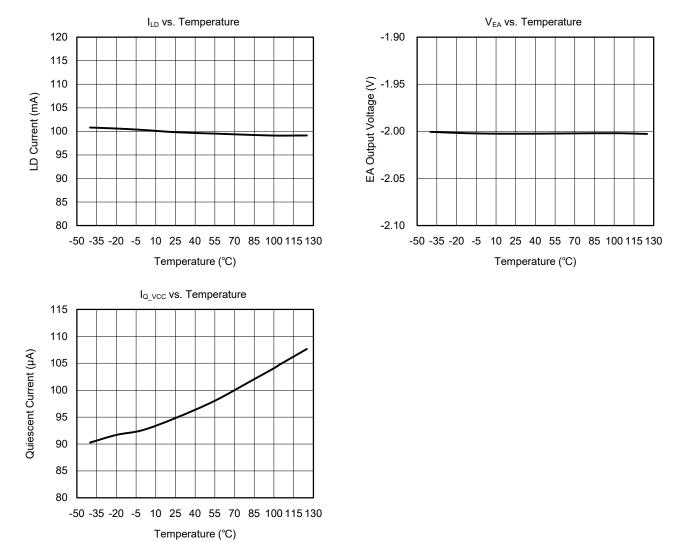

# FUNCTIONAL BLOCK DIAGRAM

Figure 3. Block Diagram

# **DETAILED DESCRIPTION**

The SGM41295S provides DC bias for the laser diode, EA bias, and MPD bias monitor circuits, and it also provides an unregulated negative output generated by an inverting charge pump which is equal to negative input voltage. This chip supports  $I^2C$  interface and other features such as Laser Diode (LD) open/short monitor, EAM short monitor, over-temperature alert, over-temperature protection and so on.

#### **Negative Charge Pump**

The SGM41295S uses a switched capacitor charge pump to get an unregulated negative voltage with an absolute value of V<sub>CC</sub>. The switching signal, which drives the charge pump, is created by an integrated oscillator within the control circuit block. The charge pump switching frequency is from 60kHz to 2MHz. The SGM41295S will automatically adjust the frequency according to V<sub>CC</sub> and V<sub>NEG</sub> voltage gap. The oscillator frequency will compensate the output ripple at heavy load condition. When the absolute value of V<sub>NEG</sub> is smaller than 0.7 × V<sub>CC</sub>, the charge pump will treat it as over current condition. SGM41295S will limit the input current. The equivalent output resistance of the charge pump is about 1.9 $\Omega$ .

#### **Enable and Disable**

In order to enable the LD current source, 3 conditions have to be met:

1. VCC voltage is higher than UVLO threshold for longer than 10ms.

2. Logic high on EN\_LD pin.

3. Setting  $LD_EN = '1'$ , by enabling the corresponding bit of the register 0x03h Bit[0].

Pulling EN\_LD pin low, setting LD\_EN = '0', or setting VCC voltage lower than UVLO threshold can disable the LD current source.

In order to enable the EA, 2 conditions have to be met:

1. VCC voltage is higher than UVLO threshold for longer than 10ms.

2. Setting EA\_EN = '1', by enabling the corresponding bit of the register 0x03h Bit[1].

Either setting  $EA_EN = '0'$  or VCC voltage lower than UVLO threshold can disable the EA.

#### **Programming LD Current Source**

The LD current source is programmed with 8-bit DAC. The added offset current is 112mA, 96mA, 80mA, 64mA, 48mA, 32mA, 16mA or 0mA respectively, which is set by Bit[2:0] in register 0x05h. The LD current is calculated with the following equation:

$$I_{LD} = k \times (I_{OFFSET} + 128 \times (Code/256))$$

(1)

where k is the LD current gain (1 or 1/2), the  $I_{OFFSET}$  is the added offset current, and Code is from 0 to 255.

For example, setting Bit[7:0] = 00000010 in register 0x05h and Bit[7:0] =10001000 in register 0x20h can set  $I_{LD}$  = 100mA. When V<sub>CC</sub> is lower than 3V, the recommended maximum set current of LD current source is 200mA.

#### **Programming EA Voltage**

The EA voltage is programmed with 8-bit linear coded DAC and is calculated with the following equation:

$$V_{EA} = -3.2 \times (Code/256)$$

(2)

where Code is from 0 to 255.

For example, setting Bit[7:0] = 10100000 in register 0x21h (Code = A0) can set  $V_{EA0}$  = -2V.

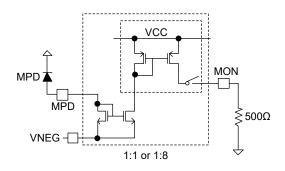

#### **MPD Pin Application**

EML backside MPD current is monitored by sinking current to VNEG through MPD pin. Please refer to Figure 4 for more detail. When the input current is large, it is recommended to reduce the load resistance.

Figure 4. MPD Pin Application

# **DETAILED DESCRIPTION (continued)**

#### **Multiplexed Monitor Output**

There are three monitor signals multiplexed for output, and they are selected via the  $l^2C$  interface. One of those analog values monitored is selected by setting the register 0x06h, and the selected one is transferred to the MON pin.

#### EAM Current Sampling

EAM current is sampled and converted into current source in 40:1 or 20:1 ratio. Connect a resistor between MON pin and GND to convert the sampled current into voltage for ADC conversion. The transfer function is shown below:

$$I_{MONx} = \frac{I_{EA}}{S}$$

(3)

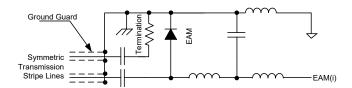

where,  $I_{MONx}$  is the MON pin output current. S is the sampling ratio which can be set by  $I^2C$  interface. Figure 5 shows the typical application circuit of EAM bias.

Figure 5. Typical Application Circuit of EAM Bias

#### FAULT Flag and OT Status Read

LD open status can be read through Bit[4] in register 0x01h. LD current source short status can be read through Bit[5] in register 0x01h. EA pin short status can be read through Bit[3] in register 0x01h. OT\_Alert status can be read through Bit[2] in register 0x01h.

When any abnormal event occurs, including LD open, LD current source short, EA pin short and over-temperature alert, the shared flag is set to high, which then can be read through the Fault bit (Bit[1] in register 0x01h).

#### **Under-Voltage Lockout (UVLO)**

The SGM41295S integrates an under-voltage lockout block. When VCC voltage is higher than UVLO threshold for longer than 10ms, the device is enabled. The device will be disabled as soon as the VCC voltage falls below the UVLO threshold, and then the device stops responding to any instruction sent to it.

#### I<sup>2</sup>C Reset

Setting Bit[2] in register 0x00h to high can reset all digital settings to defaults.

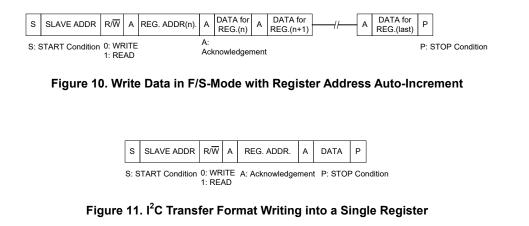

#### I<sup>2</sup>C Serial Interface Description

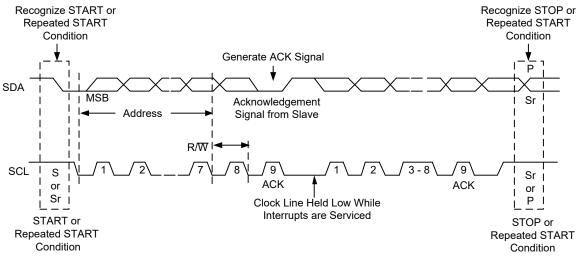

The SGM41295S communicates through an industry standard  $I^2C$  compatible interface, to receive data in slave mode.  $I^2C$  is a 2-wire serial interface developed by Philips Semiconductor (see  $I^2C$ -Bus Specification).

The bus consists of a data line (SDA) and a clock line (SCL) with pull-up structures. When the bus is idle, both SDA and SCL lines are pulled high. All the  $I^2C$  compatible devices are connected to the  $I^2C$  bus through open-drain I/O pins, SDA and SCL pins. A master device, usually a microcontroller or a digital signal processor, controls the bus.

The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. A slave device receives and/or transmits data on the bus under control of the master device.

The SGM41295S works as a slave and supports the following data transfer modes, as defined in the  $l^2$ C-Bus Specification: standard mode (100kbps), fast mode (400kbps) and fast-mode plus (1000kbps). The data transfer protocols for standard mode, fast mode and fast-mode plus are exactly the same, therefore they are referred to as F/S-mode plus in this document. The SGM41295S supports 7-bit addressing, and the LSB enables the write or read function (see Table 1).

# **DETAILED DESCRIPTION (continued)**

The device that initiates the communication is called a master, and the devices controlled by the master are slaves. The master generates the serial clock on SCL, controls the bus access, and generates START and STOP conditions (see Figure 6). A START initiates a new data transfer to a slave. Transitioning SDA from high to low while SCL remains high generates a START condition. A STOP condition ends a data transfer to slave. Transitioning SDA from low to high while SCL remains high generates a STOP condition.

The master then generates the SCL pulses, and transmits the 7-bit address and the read/write direction bit  $R/\overline{W}$  on the SDA line. During all transmissions, the master ensures that the data is valid. A valid data condition requires the SDA line to be stable during the entire high period of the clock pulse (see Figure 7). All devices recognize the address sent by the master and compare it to their internal fixed addresses. Only the slave device with a matching address generates an Acknowledgment, ACK, (see Figure 8) by pulling the SDA line low during the entire high period of the SCL cycle. Upon detecting this ACK, the master knows that communication link with a slave has been established.

This device could be programmed for eight slave addresses by connecting a resistor  $R_{ADDR}$  between the A0 pin and ground, which is shown in Table 1. And ±5% accuracy resistor is suitable for most applications.

The master generates further SCL cycles to either transmit data to the slave  $(R/\overline{W} \text{ bit } = 0)$  or receive data from the slave  $(R/\overline{W})$  bit = 1). In either case, the receiver needs to acknowledge the data sent by the transmitter. So an ACK signal can either be generated by the master or by the slave, depending on which one is the receiver. 9-bit valid data sequences consisting of 8-bit data and 1-bit ACK can continue as long as necessary. To terminate the data transfer, the master generates a STOP condition by pulling the SDA line from low to high while the SCL line is high (see Figure 9). This releases the bus and stops the communication link with the addressed slave. All I<sup>2</sup>C compatible devices must recognize the STOP condition. Upon the receipt of a STOP condition, all devices know that the bus is released, and they wait for a START condition followed by a matching address.

| (MSB) |   | so | GM41295S | ADDRESS |   |   | (LSB) | 8-Bit Write Value<br>(Hex) | R <sub>ADDR</sub> (kΩ) |

|-------|---|----|----------|---------|---|---|-------|----------------------------|------------------------|

| 0     | 0 | 1  | 1        | 0       | 0 | 0 | R/W   | 0x30                       | 0                      |

| 0     | 0 | 1  | 1        | 0       | 0 | 1 | R/W   | 0x32                       | 4.64                   |

| 0     | 0 | 1  | 1        | 0       | 1 | 0 | R/W   | 0x34                       | 9.1                    |

| 0     | 0 | 1  | 1        | 0       | 1 | 1 | R/W   | 0x36                       | 15.4                   |

| 0     | 0 | 1  | 1        | 1       | 0 | 0 | R/W   | 0x38                       | 25.5                   |

| 0     | 0 | 1  | 1        | 1       | 0 | 1 | R/W   | 0x3A                       | 44.2                   |

| 0     | 0 | 1  | 1        | 1       | 1 | 0 | R/W   | 0x3C                       | 86.6                   |

| 0     | 0 | 1  | 1        | 1       | 1 | 1 | R/W   | 0x3E                       | 300                    |

#### Table 1. SGM41295S Slave Address Byte

### SGM41295S

**DETAILED DESCRIPTION (continued)**

#### DATA CLK S Р STOP Condition START Condition Figure 6. START and STOP Conditions DATA CLK Data Line Stable; Change of Data Valid Data Allowed Figure 7. Bit Transfer on the Serial Interface Data Output by Transmitter Not Acknowledgement Data Output by Receiver Acknowledgement SCL from Master 8 9 S Clock Pulse for START Acknowledgement Condition Figure 8. Acknowledgement on the I<sup>2</sup>C Bus Recognize START or Repeated START Condition

### SGM41295S

# **CONTROLS AND LOGIC DIAGRAMS**

| s     | SLAVE ADDR      | R/W   | А    | REG. ADDR(n). | А | Sr | SLAVE ADDR                    | R/W              | А | DATA for REG.(n) | DATA for<br>REG.(n+1) | <u>}//</u> | A | DATA for<br>REG.(last) | Ā | Ρ |  |

|-------|-----------------|-------|------|---------------|---|----|-------------------------------|------------------|---|------------------|-----------------------|------------|---|------------------------|---|---|--|

| S: \$ | START Condition | 0: WF | RITE |               |   |    | owledgement<br>eated START Co | 1: RE<br>ndition |   |                  |                       |            |   | A: Not Ac<br>P: STOP   |   |   |  |

Figure 12. Read Data in F/S-Mode with Register Address Auto-Increment

## **REGISTER MAP**

| Image: Provide the second se | Addr   | Byte Name  | Bit<br>No. | Default<br>Hex | RW   | Function                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Image: Constraint of the second of  |        |            | 7:3        | 00             | RW   | Reserved.                                                                                                                                                        |

| 0x01h     F     1     R     Reserved.       0x01h     Status     5     0     R     LD Short Flag. This flag will be set high when LD is shorted to GND.       3     0     R     LD Short Flag. This flag will be set high when LD is open.       2     0     R     LD Short Flag. This flag will be set high when do is open.       2     0     R     LD Short Flag. This flag will be set high when die temperature is higher th +140°C. Fault flag will be set high when of a temperature is higher th +140°C. Fault flag will be set high when certain abnormal events happen.       0     x     R     EN_LD P in Status.       0x02h     Sample Ratio     7.1     00     RW       0     x     R     EN_LD.V P in Status.       0x02h     LD EN     0     RW     Reserved.       0x03h     LD EN     1     1 RW     Reserved.       0x04h     MPD     7.1     00     RW     Reserved.       0x04h     MPD     7.1     00     R     Reserved.       0x04h     MPD     Rate     7.1     00     R     Reserved. </td <td>0x00h</td> <td>Soft Reset</td> <td>2</td> <td>0</td> <td>RW</td> <td>1: Generate Reset. Reset all digital settings to defaults.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00h  | Soft Reset | 2          | 0              | RW   | 1: Generate Reset. Reset all digital settings to defaults.                                                                                                       |

| 0x01h     Final Status     6     0     R     Reserved.       0x01h     Status     6     0     R     LD Open Flag. This flag will be set high when LD is shorted to GND.       1     0     R     Vr.A. Short Flag. This flag will be set high when Ver, is shorted to GND.       1     0     R     Vr.A. Short Flag. This flag will be set high when OT_Alert is high.       1     0     R     Fault Flag. The flag will be set high when OT_Alert is high.       1     0     R     Fault Flag. The flag will be set high when OT_Alert is high.       1     0     R     Fault Flag. The flag will be set high when OT_Alert is high.       0     0     RW     Reserved.     Context flag. The flag. This flag will be set high when OT_Alert is high.       0x02h     IEA<br>Sample     7:1     00     RW     Reserved.       0x03h     LD_ENV<br>VEA_EN     7:3     00     RW     Reserved.       0x04h     MPDR<br>Reserved.     1     RW     Reserved.     Reserved.       0x04h     MEDR<br>Reserved.     1     Reserved.     Reserved.     Reserved.       0x04h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |            | 1:0        | 0              | RW   | Reserved.                                                                                                                                                        |

| 0x01h     Status     5     0     R     LD Short Flag. This flag will be set high when LD is shorted to GND.       0x01h     4     0     R     LD Open Flag. This flag will be set high when Ve, is shorted to GND.       2     0     R     Ve, Short Flag. This flag will be set high when Ve, is shorted to GND.       2     0     R     OT. Alert (Over-Temperature Alert). The flag will be set high when die temperature is higher th +140°C. Fault flag will be set so set high when OT_Alert is high.       0     x     R     EN_LD Pin Status.       0x02h     Sample Ratio     0     0     RW     Reserved.       0x03h     VEA_EN     7:1     00     RW     Reserved.       0x03h     VEA_EN     7:1     00     RW     Reserved.       0x03h     VEA_EN     7:1     00     RW     Reserved.       0x04h     MPD     Rarge     0     1     RW     Reserved.       0x04h     MPD     Rarge     7:1     00     R     Reserved.       0x04h     MPD     Rarge     7:4     00     R     Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |            | 7          | 1              | R    | Reserved.                                                                                                                                                        |

| Ave:     Ave:     Ave:     Depen Flag. This flag will be set high when LD is open.       0x01h     Status     3     0     R     V <sub>DA</sub> Short Flag. This flag will be set high when V <sub>DA</sub> is shorted to GND.       2     0     R     OT_Alert (Over-Terguture Alert). The flag will be set high when OT_Alert is high.       1     0     R     Fault Flag. The flag will be sets thigh when OT_Alert is high.       1     0     R     Fault Flag. The flag will be sets thigh when OT_Alert is high.       0x02h     Sample<br>Ratio     7:1     00     RW     Reserved.       0x03h     VEA_ENN     7:1     00     RW     Reserved.       0x03h     VEA_ENN     7:3     00     RW     Reserved.       0x03h     VEA_ENN     7:1     00     R     Reserved.       0x04h     Range<br>Selection     7:1     00     R     Reserved.       0x04h     Range<br>Selection     7:1     00     R     Reserved.       0x04h     Range<br>Selection     7:4     00     R     Reserved.       0x00h     Ront Selection. The selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |            | 6          | 0              | R    | Reserved.                                                                                                                                                        |

| 0x01h     Status     3     0     R     V <sub>EA</sub> Short Flag. This flag will be set high when V <sub>EA</sub> is shorted to GND.       2     0     R     OT_Alert (Over-Temperature Alert). The flag will be set high when die temperature is higher th         +140°C. Fault flag will be also set high when OT_Alert is high.       1     0     R     PAIRt Flag. This flag will be also set high when OT_Alert is high.       0x02h     Sample Ratio     0     R     EN_LD Pin Status.       0x02h     Sample Ratio     0     R     R EN_LD Pin Status.       0x03h     LD_EN/<br>VEA_EN     0     RW     Reserved.       0x04h     MPD<br>Range<br>Selection     0     RW     Reserved.       0x04h     MPD<br>Range<br>Selection     7.1     00     RW     Reserved.       0x04h     MPD<br>Range<br>Selection     7.1     00     R     Reserved. <td></td> <td></td> <td>5</td> <td>0</td> <td>R</td> <td>LD Short Flag. This flag will be set high when LD is shorted to GND.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |            | 5          | 0              | R    | LD Short Flag. This flag will be set high when LD is shorted to GND.                                                                                             |

| No.     No. <td></td> <td></td> <td>4</td> <td>0</td> <td>R</td> <td>LD Open Flag. This flag will be set high when LD is open.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |            | 4          | 0              | R    | LD Open Flag. This flag will be set high when LD is open.                                                                                                        |

| Image: Problem in the state of the | 0x01h  | Status     | 3          | 0              | R    | $V_{EA}$ Short Flag. This flag will be set high when $V_{EA}$ is shorted to GND.                                                                                 |

| Image: Note of the system of the sy |        |            | 2          | 0              | R    | OT_Alert (Over-Temperature Alert). The flag will be set high when die temperature is higher than +140°C. Fault flag will be also set high when OT_Alert is high. |

| Ux02h     IEA<br>Sample<br>Ratio     7:1     00     RW     Reserved.       0x03h     VEA_EN     7:3     00     RW     Reserved.       0x03h     VEA_EN     7:3     00     RW     Reserved.       0x03h     VEA_EN     1     RW     Reserved.       0x03h     VEA_EN     1     RW     Reserved.       0x04h     Rage<br>Selection     0     1     RW     Enable 0: Disable.       0x04h     MPD<br>Range<br>Selection     7:1     00     R     Reserved.       0x04h     MPD<br>Range<br>Selection     7:1     00     R     Reserved.       0x04h     MPD<br>Range<br>Selection     7:1     00     R     Reserved.       0x04h     MPD<br>Range<br>Selection     7:4     00     R     Reserved.       0x04h     LD Gain<br>and Offset<br>Ctrl     7:4     00     R     Reserved.       0x05h     LD Gain<br>and Offset<br>Ctrl     7:4     00     R     Reserved.       0x06h     Multiplex<br>Ctrl     7:4     00     R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |            | 1          | 0              | R    | Fault Flag. The flag will be set high when certain abnormal events happen.                                                                                       |

| 0x02h<br>Ratio     Sample<br>Ratio     0     0     RW     1 for 40:1 (lex/luon).<br>0 for 20:1 (lex/luon).<br>0 for 20:1 (lex/luon).       0x03h     Image: Comparison of the second of the sec                                                                                                 |        |            | 0          | х              | R    | EN_LD Pin Status.                                                                                                                                                |

| Ratio00RWI (He,Husto),<br>0 for 20:1 (EgAlaco),<br>0 for 20:1 (EgAlaco),<br>0 for 20:1 (EgAlaco),0x03h $LD_{EN}$ 7:300RWReserved.21RWReserved.21RWEnable Ve, Voltage Source.<br>1: Enable, 0: Disable.0x04h11RWEnable Ve, Voltage Source.<br>1: Enable, 0: Disable.0x04hMPD<br>Range<br>Selection7:100RReserved.0x04hMPD<br>Range<br>Selection7:100RReserved.0x04hMPD<br>Range<br>Selection7:100RReserved.0x04hMPD<br>Range<br>Selection7:400RReserved.0x04hMPD<br>Cfri7:400RReserved.1. C finding range for MPD is 50µA ~ 250µA (mirror ratio = 1:1),<br>1: The monitoring range for MPD is 50µA ~ 250µA (mirror ratio = 1:8).1. C finding range for MPD is 50µA ~ 250µA (mirror ratio = 1:4),<br>1: The monitoring range for MPD is 50µA ~ 250µA (mirror ratio = 1:8).1. D Fin Offset Current Gain Selection.<br>0: The ILp offset current is 30µA ~ 239.5mA). 1: gain = 1/2 (0mA ~ 119.75mA).0x05hLD Gain<br>and Offset<br>Ctrl2:002:00RWUD Pin Offset Selection.<br>0: The ILp offset current is 32mA.<br>10: The ILp offset current is 32mA.<br>10: The ILp offset current is 48mA.<br>10: The ILp offset current is 80mA.<br>11: The ILp offset current is 96mA.<br>11: The ILp of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |            | 7:1        | 00             | RW   | Reserved.                                                                                                                                                        |

| No.33h     LD_EN/<br>VEA_EN     2     1     RW     Reserved.       0x03h     LD_EN/<br>VEA_EN     1     1     RW     Reserved.       0     1     RW     Enable V <sub>E</sub> , Voltage Source.<br>1: Enable, 0: Disable.     1       0x04h     MPD<br>Range<br>Selection     7:1     00     R     Reserved.       0x04h     MPD<br>Range<br>Selection     0     0     Reserved.     MPD monitoring current.<br>0: The monitoring range for MPD is 250µA ~ 2mA (mirror ratio = 1:1).<br>1: The monitoring range for MPD is 250µA ~ 2mA (mirror ratio = 1:2).       1     1     0     R     Reserved.       3     0     RW     LD Current Gain Selection. 0: gain = 1 (0mA ~ 239.5mA). 1: gain = 1/2 (0mA ~ 119.75mA).       0x05h     LD Gain<br>and Offset<br>Ctrl     3     0     RW     LD Current Gain Selection.<br>000: The ILD offset current is 0mA.<br>010: The ILD offset current is 0mA.<br>010: The ILD offset current is 32mA.<br>100: The ILD offset current is 64mA.<br>100: The ILD offset current is 64mA.<br>100: The ILD offset current is 80mA.<br>110: The ILD offset current is 96mA.<br>110: The ILD offset current is 96mA.<br>111: The ILD offset current is 96mA.<br>110: The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x02h  |            | 0          | 0              | RW   |                                                                                                                                                                  |

| Dx03h     LD_EN/<br>VEA_EN     1     1     RW     Enable V <sub>EA</sub> Voltage Source.<br>1: Enable, 0: Disable.       0     1     RW     Enable UC current Source.<br>1: Enable, 0: Disable.     Reserved.       0x04h     MPD<br>Range<br>Selection     7:1     00     R     Reserved.       0x04h     MPD<br>Range<br>Selection     0     0     R     Reserved.       0x04h     MPD<br>Range<br>Selection     0     0     R     Reserved.       0x04h     MPD<br>Range<br>Selection     0     0     R     Reserved.       0x05h     LD Gain<br>and Offset<br>Ctrl     7:4     00     R     Reserved.       2:0     0     RW     LD Current Gain Selection.<br>000: The I <sub>Lo</sub> offset current is 0mA.<br>010: The I <sub>Lo</sub> offset current is 0mA.<br>010: The I <sub>Lo</sub> offset current is 48mA.<br>100: The I <sub>Lo</sub> offset current is 48mA.<br>100: The I <sub>Lo</sub> offset current is 48mA.<br>100: The I <sub>Lo</sub> offset current is 80mA.<br>110: The I <sub>Lo</sub> offset current is 80mA.<br>110: The I <sub>Lo</sub> offset current is 90mA.<br>110: The I <sub>Lo</sub> offset current is 90mA.<br>110: The I <sub>Lo</sub> offset current is 90mA.<br>111: The I <sub>Lo</sub> offset current is 90mA.<br>110: The I <sub>Lo</sub> offset current is 90mA.<br>110: The I <sub>Lo</sub> offset current is 90mA.<br>111: The I <sub>Lo</sub> offset current is 90mA.<br>112: The I <sub>Lo</sub> offset current is 90mA.<br>113: The I <sub>Lo</sub> offset current is 90mA.<br>114: The I <sub>Lo</sub> offset current is 90mA.<br>115: The I <sub>Lo</sub> offset current is 90mA.<br>116: The I <sub>Lo</sub> offset current is 90mA.<br>11                                                                                                                                                                                                                                                                                                                                                                                                         |        |            | 7:3        | 00             | RW   | Reserved.                                                                                                                                                        |

| 0x03n   VEĀ_EN   1   1   RW   Enable VeAveAveAveAveAveAveAveAveAveAveAveAveAve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | ID FN/     | 2          | 1              | RW   |                                                                                                                                                                  |

| MPD<br>Range<br>Selection     7:1     00     R     Reserved.       0x04h     MPD<br>Range<br>Selection     0     0     R     Reserved.       0x04h     MPD<br>Range<br>Selection     0     0     RW     MPD Range Selection. The selection of monitoring range for MPD. This bit is to select the ran<br>0 <sup>-</sup> The monitoring current.<br>0 <sup>-</sup> The monitoring current.<br>0 <sup>-</sup> The monitoring range for MPD is 250µA ~ 2mA (mirror ratio = 1:1).<br>1 <sup>-</sup> The monitoring range for MPD is 50µA ~ 250µA (mirror ratio = 1:2).       1     7:4     00     R     Reserved.       3     0     RW     LD Current Gain Selection. 0 <sup>-</sup> gain = 1 (0mA ~ 239.5mA). 1 <sup>-</sup> gain = 1/2 (0mA ~ 119.75mA).       1     D Pin Offset Selection.<br>000 <sup>-</sup> The I <sub>LD</sub> offset current is 0mA.<br>01 <sup>-</sup> The I <sub>LD</sub> offset current is 16mA.<br>01 <sup>-</sup> The I <sub>LD</sub> offset current is 32mA.<br>10 <sup>-</sup> The I <sub>LD</sub> offset current is 48mA.<br>10 <sup>-</sup> The I <sub>LD</sub> offset current is 80mA.<br>11 <sup>-</sup> The I <sub>LD</sub> offset current is 80mA.<br>11 <sup>-</sup> The I <sub>LD</sub> offset current is 96mA.<br>11 <sup>-</sup> The I <sub>LD</sub> offset current is 96mA.<br>11 <sup>-</sup> The I <sub>LD</sub> offset current is 112mA.       0x06h     Multiplex<br>Monitoring<br>Output<br>Selection     7 <sup>-</sup> 2     00     RW     Reserved.       0x06h     Multiplex<br>Monitoring<br>Output<br>Selection     7 <sup>-</sup> 2     00     RW     Reserved.       0x02h     ILD     7 <sup>-</sup> 0     0     RW     Reserved.     7 <sup>-</sup> 0<                                                                                                                                                                                                                                                                                                                                                                                            | 0x03h  |            | 1          | 1              | RW   | 1: Enable, 0: Disable.                                                                                                                                           |

| MPD<br>Range<br>Selection     MPD<br>noto     MPD Range Selection. The selection of monitoring range for MPD. This bit is to select the ran<br>of MPD monitoring current.<br>0: The monitoring range for MPD is 250µA ~ 2mA (mirror ratio = 1:1).<br>1: The monitoring range for MPD is 250µA ~ 250µA (mirror ratio = 1:1).       V     7:4     00     R     Reserved.       3     0     RW     LD Current Gain Selection. 0: gain = 1 (0mA ~ 239.5mA). 1: gain = 1/2 (0mA ~ 119.75mA).       LD Gain<br>and Offset<br>Ctrl     2:0     0     RW     LD Current Gain Selection.<br>000: The I <sub>LD</sub> offset current is 10mA.<br>010: The I <sub>LD</sub> offset current is 32mA.<br>010: The I <sub>LD</sub> offset current is 48mA.<br>100: The I <sub>LD</sub> offset current is 64mA.<br>101: The I <sub>LD</sub> offset current is 80mA.<br>110: The I <sub>LD</sub> offset current is 96mA.<br>111: The I <sub>LD</sub> offset current is 112mA.       0x06h     Multiplex<br>Monitoring<br>Output<br>Selection     7:2     00     RW     Reserved.       0x06h     Multiplex<br>Monitoring<br>Output<br>Selection     7:2     00     RW     Reserved.       0x06h     Multiplex<br>Monitoring<br>Output     7:2     00     RW     Reserved.       0x06h     Multiplex<br>Monitoring<br>Output     7:0     3     RW     Multiplex Monitoring Output Channel Selection <sup>(1)</sup> . This register is used to select channels to MC<br>pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |            | 0          | 1              | RW   |                                                                                                                                                                  |