# SGM260321 High-Integration PMIC with 3 Bucks, 2 LDOs and Load Switch

# GENERAL DESCRIPTION

The SGM260321 is a highly integrated multi-channel power management device. It supports a variety of microcontrollers, solid-state drive (SSD) applications. It consists of three Buck converters and two LDOs that deliver several output voltages. Buck1 can be set as a load switch. All outputs are highly configurable through the I<sup>2</sup>C interface. The device has several default configurations which are programmed in the factory. System level sequencing, output voltage, switching frequency, start-up time, soft-start time, sleep and DPSLP modes, operating modes, and other settings can all be configured.

SGM260321 supplies 4 configurable GPIOs for system hardware control requirements. These GPIOs can be set for a variety of functions. Four input functions are EXT\_PG, DVS control, SYS\_EN, LSW (load switch mode) LDO control, and four output functions are EXT\_EN, nRESET, nIRQ, SYSMON.

A number of protection features are provided in the device including under-voltage/over-voltage protection, short-circuit, over-current and over-temperature shutdown.

The SGM260321 is available in a Green WLCSP-2.42×2.82-36B package.

# **APPLICATIONS**

Solid-State Drives

FPGA

Microcontroller Applications

Personal Navigation Devices

## **FEATURES**

- Input Voltage Range: 2.7V to 5.5V

- Advanced PMIC:

- + Buck1:

4A Maximum Output Current Capability, Configurable Bypass Function 0.6V <sup>(1)</sup> to 2.991V Programmable, 9.375mV/Step 0.8V <sup>(1)</sup> to 3.9875V Programmable, 12.5mV/Step

+ Buck2:

3A Maximum Output Current Capability 0.6V to 2.991V Programmable, 9.375mV/Step 0.8V to 3.9875V Programmable, 12.5mV/Step

+ Buck3:

3A Maximum Output Current Capability 0.8V to 3.9875V Programmable, 12.5mV/Step

+ LDO1/LDO2:

300mA Maximum Output Current Capability 0.6V to 2.991V Programmable, 9.375mV/Step 0.8V to 3.9875V Programmable, 12.5mV/Step

- Flexible Configurable

- Output Voltage

- Soft-Start Time

- Start-Up Sequence

- Switching Frequency

- Current Limit

- Status Reporting and Controllability via I<sup>2</sup>C Interface

- 4 Programmable GPIOs

- Seamless Sequencing of External Supplies

- Multiple Sleep Modes

- I<sup>2</sup>C Interface: 1MHz (MAX)

- Input OV/UV Protection

- Output OV/UV Protection

- Thermal Shutdown Protection

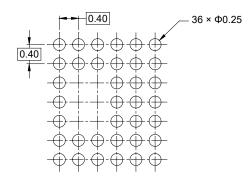

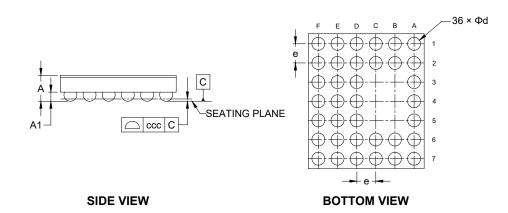

- Available in a Green WLCSP-2.42×2.82-36B Package

NOTE: 1. The Buck1 is optimized for large duty cycle applications, so a minimum output voltage of 1.7V is recommended for Buck1.

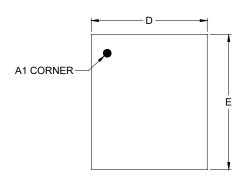

# PACKAGE/ORDERING INFORMATION

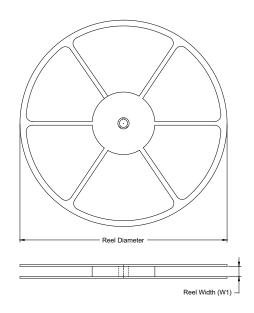

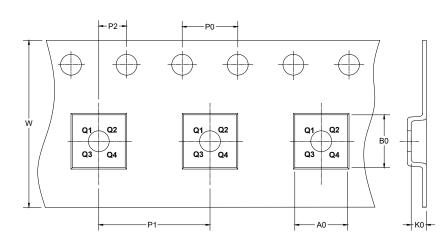

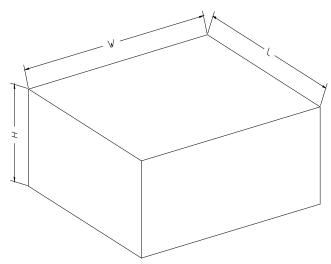

| MODEL         | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING                | PACKING<br>OPTION   |

|---------------|------------------------|-----------------------------------|--------------------|-----------------------------------|---------------------|

| SGM260321-003 | WLCSP-2.42×2.82-36B    | -40°C to +125°C                   | SGM260321-003XG/TR | SGM<br>260321-3<br>XXXXX<br>XX#XX | Tape and Reel, 5000 |

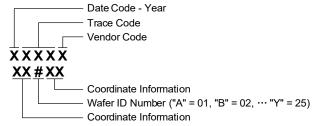

## MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code. XX#XX = Coordinate Information and Wafer ID Number.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| ADOOLO I E INAMINION NATIN              | 00             |

|-----------------------------------------|----------------|

| All I/O and Power Pins Except AGND, PGI | NDx0.3V to 6V  |

| Any PGND referenced to AGND             | 0.3V to 0.3V   |

| SW_Bx to PGNDx                          | 1V to 6V       |

| FB_Bx to PGNDx                          | 0.3V to 6V     |

| LDOx to AGND                            | 0.3V to 6V     |

| Package Thermal Resistance              |                |

| WLCSP-2.42×2.82-36B, θ <sub>JA</sub>    | 43.8°C/W       |

| WLCSP-2.42×2.82-36B, θ <sub>JB</sub>    | 12.5°C/W       |

| WLCSP-2.42×2.82-36B, θ <sub>JC</sub>    | 10.2°C/W       |

| Junction Temperature                    | +150°C         |

| Storage Temperature Range               | 65°C to +150°C |

| Lead Temperature (Soldering, 10s)       | +260°C         |

| ESD Susceptibility (1) (2)              |                |

| HBM                                     | ±2000V         |

| CDM                                     | ±1000V         |

|                                         |                |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

# RECOMMENDED OPERATING CONDITIONS

| Input Supply Voltage Range, V <sub>IN</sub> | 2.7V to 5.5V  |

|---------------------------------------------|---------------|

| Operating Junction Temperature Range40      | 0°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

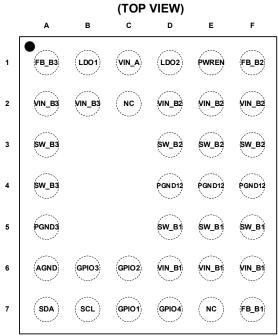

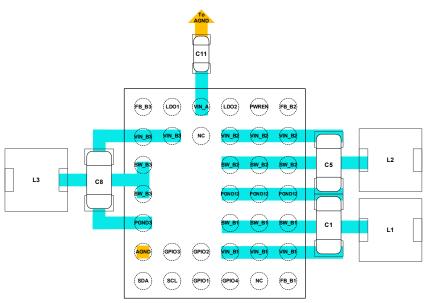

# **PIN CONFIGURATION**

WLCSP-2.42×2.82-36B

# **PIN DESCRIPTION**

| PIN        | NAME   | FUNCTION                                                             |                                                                                                                                               |  |  |  |

|------------|--------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| E1         | PWREN  | Detailed operation modes are de logic level specifications in the El | rol the device in power-on/DPSLP mode. escribed in the DPSLP state section. Ensure input voltage compliance with ectrical Characteristics.    |  |  |  |

| A6         | AGND   |                                                                      | and reference for the IC's analog circuitry and LDOx. It must be connected no high-current paths flow through this connection.                |  |  |  |

| D4, E4, F4 | PGND12 | Power Ground of Buck1/Buck2.                                         | The PGNDx pins serve as the power ground connections for the Buck                                                                             |  |  |  |

| A5         | PGND3  | Power Ground of Buck3.                                               | converters and are directly linked to the low-side FETs. Buck1 and Buck2 share pins D4, E4, and F4 (PGND12), while Buck3 uses pin A5 (PGND3). |  |  |  |

| C1         | VIN_A  | Analog VIN Supply and Power In AGND on the top PCB layer.            | put of LDO1/LDO2. Require a 2.2µF ceramic capacitor directly connected to                                                                     |  |  |  |

| D6, E6, F6 | VIN_B1 | VIN Power Input of Buck1.                                            |                                                                                                                                               |  |  |  |

| D2, E2, F2 | VIN_B2 | VIN Power Input of Buck2.                                            | Each VIN_Bx requires direct connection to its corresponding PGNDx pin through a 10µF bypass capacitor on the top PCB layer.                   |  |  |  |

| A2, B2     | VIN_B3 | VIN Power Input of Buck3.                                            | Tillough a Topic bypass capacitor on the top PCB layer.                                                                                       |  |  |  |

| D5, E5, F5 | SW_B1  | Switch Pin of Buck1.                                                 | Buck converter switch nodes requiring direct top-layer connection to                                                                          |  |  |  |

| D3, E3, F3 | SW_B2  | Switch Pin of Buck2.                                                 | inductors.                                                                                                                                    |  |  |  |

| A3, A4     | SW_B3  | Switch Pin of Buck3.                                                 | - mudctors.                                                                                                                                   |  |  |  |

| F7         | FB_B1  | Feedback of Buck1.                                                   | Buck regulator feedback pins requiring Kelvin connections to output                                                                           |  |  |  |

| F1         | FB_B2  | Feedback of Buck2.                                                   | capacitors.                                                                                                                                   |  |  |  |

| A1         | FB_B3  | Feedback of Buck3.                                                   | edpastere.                                                                                                                                    |  |  |  |

| B1         | LDO1   | Output of LDO1.                                                      | LDOx outputs requiring 1µF bypass capacitors to AGND.                                                                                         |  |  |  |

| D1         | LDO2   | Output of LDO2.                                                      | LDOX outputs requiring the bypass capacitors to AOND.                                                                                         |  |  |  |

| C7         | GPIO1  |                                                                      |                                                                                                                                               |  |  |  |

| C6         | GPIO2  | Configurable General Purpose                                         | Four programmable pins assigned specific functions through CMI configurations. Four input functions are EXT PG, DVS control, SYS EN,          |  |  |  |

| В6         | GPIO3  | I/O (Open-Drain or Push-Pull).                                       | and LSW LDO control, and four output functions are EXT_EN, nRESET, nIRQ, SYSMON.                                                              |  |  |  |

| D7         | GPIO4  |                                                                      | TIIITQ, STOWON.                                                                                                                               |  |  |  |

| A7         | SDA    | I <sup>2</sup> C Data Input and Output.                              | Standard I <sup>2</sup> C interface pins for digital communication.                                                                           |  |  |  |

| В7         | SCL    | I <sup>2</sup> C Clock Input.                                        | Standard i C interface pins for digital confindincation.                                                                                      |  |  |  |

| C2, E7     | NC     | No Connection.                                                       |                                                                                                                                               |  |  |  |

# **ELECTRICAL CHARACTERISTICS**

| PARAMETER                                        | SYMBOL                | C                                                                                                                                         | CONDITIONS            | MIN                      | TYP  | MAX  | UNITS |

|--------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|------|------|-------|

| Digital I/O                                      |                       | •                                                                                                                                         |                       |                          |      |      | •     |

| PWREN Input High Voltage                         | V <sub>IH_PWREN</sub> |                                                                                                                                           |                       | 1.2                      |      |      | V     |

| PWREN Input Low Voltage                          | V <sub>IL_PWREN</sub> |                                                                                                                                           |                       |                          |      | 0.4  | V     |

| GPIO Input High Voltage                          | V <sub>IH_GPIO</sub>  |                                                                                                                                           |                       | 1.2                      |      |      | V     |

| GPIO Input Low Voltage                           | V <sub>IL_GPIO</sub>  |                                                                                                                                           |                       |                          |      | 0.4  | V     |

| GPIO Leakage Current                             | I <sub>LKG_GPIO</sub> | Output = 5V, T                                                                                                                            | J = -40°C to +125°C   |                          |      | 1    | μΑ    |

| GPIO Output High Voltage                         | V <sub>OH_GPIO</sub>  | I <sub>OH</sub> = 10mA, T <sub>.</sub>                                                                                                    | 」= -40°C to +125°C    | V <sub>IN_A</sub> - 0.35 |      |      | V     |

| GPIO Output Low Voltage                          | V <sub>OL_GPIO</sub>  | I <sub>OL</sub> = 10mA, T <sub>J</sub>                                                                                                    | = -40°C to +125°C     | 0.00                     |      | 0.35 | V     |

| System Control                                   | <u> </u>              |                                                                                                                                           |                       |                          |      | I    |       |

| Input Supply Voltage Range                       | V <sub>IN_A</sub>     | VIN_A referen                                                                                                                             | ced to AGND           | 2.7                      |      | 5.5  | V     |

| VIN_A Under-Voltage Threshold                    | V <sub>UV</sub>       | Falling                                                                                                                                   |                       | 2.5                      | 2.6  | 2.7  | V     |

| VIN_A Under-Voltage Hysteresis                   | V <sub>UV_HYS</sub>   |                                                                                                                                           |                       | 100                      |      |      | mV    |

| System Monitor Programmable Range                | V <sub>SYSMON</sub>   | VIN_A                                                                                                                                     |                       | 2.7                      |      | 4.2  | V     |

| VIN A Over Valteur Throughold                    | V                     | Dising                                                                                                                                    | VIN_OV_SEL = 1        |                          | 3.8  |      | .,    |

| VIN_A Over-Voltage Threshold                     | $V_{OV}$              | Rising                                                                                                                                    | VIN_OV_SEL = 0        |                          | 5.7  |      | - V   |

| VINI A Over Veltere Hiveteresia                  | V <sub>OV_HYS</sub>   | VIN_OV_SEL = 1, T <sub>J</sub> = -40°C to +125°C                                                                                          |                       | 100                      | 200  | 300  | mV    |

| VIN_A Over-Voltage Hysteresis                    |                       | $VIN_OV_SEL = 0$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$                                                                                |                       | 200                      | 300  | 400  |       |

| All regulators disable                           |                       | disabled                                                                                                                                  |                       | 18                       |      | μΑ   |       |

| Operating Supply Current                         | lα                    | All regulators enabled but no load                                                                                                        |                       |                          | 250  |      | μA    |

| Thermal Shutdown (1)                             | T <sub>SD</sub>       | Temperature r                                                                                                                             | ising                 |                          | 155  |      | °C    |

| Thermal Shutdown Hysteresis (1)                  | T <sub>HYS</sub>      |                                                                                                                                           |                       |                          | 30   |      | °C    |

| Start-Up Delay after Initial $V_{\text{IN\_A}}$  | t <sub>D_START</sub>  |                                                                                                                                           |                       |                          | 1000 |      | μs    |

| VIN_A Deglitch Time UV (1)                       | 4                     | Falling, enter UV                                                                                                                         |                       |                          | 5    |      | μs    |

| VIIV_A Degition Time OV                          | t <sub>DEG_UV</sub>   | Rising, exit U\                                                                                                                           |                       |                          | 100  |      | μο    |

| Transition Time from DPSLP State to Active State | t <sub>D_A</sub>      | Time from PWREN pin low to high transition to time when the first regulator turns on with minimum turn-on delay configuration             |                       |                          | 0.7  | 1    | ms    |

| Transition Time from Sleep to Active State       | t <sub>S_A</sub>      | Time from I <sup>2</sup> C command to clear sleep mode to time when the first regulator turns on with minimum turn-on delay configuration |                       |                          | 250  |      | μs    |

| Time to First Power Rail Turn-Off <sup>(1)</sup> | t <sub>OFF</sub>      | Time from turn-off event to when the first power rail turns off with minimum turn-off delay configuration                                 |                       |                          | 120  |      | μs    |

|                                                  |                       | x_ON_DLY[1:0                                                                                                                              |                       |                          | 0    |      |       |

| Start-Up Delay Time (1)                          | to an                 | x_ON_DLY[1:0                                                                                                                              | 0] = 01               |                          | 0.25 |      |       |

| Start-op Delay Time 17                           | t <sub>D_SU</sub>     | x_ON_DLY[1:0] = 10                                                                                                                        |                       |                          | 0.5  |      | ms    |

|                                                  |                       | x_ON_DLY[1:0                                                                                                                              | 0] = 11               |                          | 1.0  |      |       |

| Turn-Off Delay Programmable Range (1)            | t <sub>D_OFF</sub>    | Ŭ                                                                                                                                         | n 0.25ms steps        | 0                        |      | 7.75 | ms    |

| nRESET Programmable Range (1)                    | t <sub>nRESET</sub>   | Configurable to 100ms                                                                                                                     | o 20ms, 40ms, 60ms or | 20                       |      | 100  | ms    |

NOTE: 1. Guaranteed by design, not tested in production.

| PARAMETER                                                                                                  | SYMBOL                  | CONDITIONS                                                                                           | MIN  | TYP            | MAX    | UNITS             |

|------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|------|----------------|--------|-------------------|

| Buck1                                                                                                      |                         |                                                                                                      |      |                |        |                   |

| Input Operating Voltage Range                                                                              | $V_{\text{IN\_B1}}$     |                                                                                                      | 2.7  |                | 5.5    | V                 |

| Output Voltage Programming Range 1 (1)                                                                     | V <sub>OUT_B1_R1</sub>  | Configurable in 9.375mV steps                                                                        | 0.6  |                | 2.991  | V                 |

| Output Voltage Programming Range 2 (1)                                                                     | V <sub>OUT_B1_R2</sub>  | Configurable in 12.5mV steps                                                                         | 0.8  |                | 3.9875 | V                 |

| Standby Supply Current                                                                                     | I <sub>Q_B1</sub>       | No switch, $V_{OUT\_B1} = 103\%$ set point,<br>$T_J = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ |      | 30             | 60     | μΑ                |

| Output Voltage Accuracy                                                                                    | ΔV <sub>OUT_B1</sub>    | V <sub>OUT_B1</sub> = default CMI voltage,<br>continuous PWM mode                                    | -1   |                | 1      | %                 |

| , g                                                                                                        |                         | V <sub>OUT_B1</sub> = default CMI voltage, PSM mode <sup>(1)</sup>                                   | -2   |                | 2      | %                 |

| Power Good Threshold                                                                                       | $V_{PG\_B1}$            | V <sub>OUT_B1</sub> rising                                                                           | 89.5 | 92             | 94.5   | %V <sub>NOM</sub> |

| Power Good Hysteresis                                                                                      | V <sub>PG_HYS_B1</sub>  |                                                                                                      |      | 3              |        | %V <sub>NOM</sub> |

| Over-Voltage Fault Threshold                                                                               | V <sub>OV_B1</sub>      | V <sub>OUT_B1</sub> rising                                                                           | 107  | 110            | 113.5  | %V <sub>NOM</sub> |

| Over-Voltage Fault Hysteresis                                                                              | V <sub>OV_HYS_B1</sub>  |                                                                                                      |      | 3              |        | %V <sub>NOM</sub> |

| Switching Frequency                                                                                        | f <sub>OSC1</sub>       | T <sub>J</sub> = -40°C to +125°C                                                                     | -5%  | 1.125/<br>2.25 | 5%     | MHz               |

| Soft-Start Period                                                                                          | t <sub>SS_B1</sub>      | BUCK_SS = 0, 10% to 90% of V <sub>NOM</sub>                                                          |      | 500            | 750    | μs                |

| Current Limit, Cycle-by-Cycle (Accuracy is only valid for register default setting, B1_ILIM_SET[1:0] = 00) | I <sub>LIM_B1</sub>     | B1_ILIM_SET[1:0] = 00                                                                                | 4.8  | 5.6            | 6.3    | A                 |

|                                                                                                            |                         | B1_ILIM_SET[1:0] = 01                                                                                | 4.1  | 4.8            | 5.5    |                   |

|                                                                                                            |                         | B1_ILIM_SET[1:0] = 10                                                                                | 2.9  | 3.8            | 4.7    |                   |

|                                                                                                            |                         | B1_ILIM_SET[1:0] = 11                                                                                | 1.8  | 3.0            | 4.3    |                   |

| Current Limit, Warning                                                                                     |                         | Compared to current limit, cycle-<br>by-cycle                                                        | 67.5 | 75             | 82.5   | %                 |

| PMOS On-Resistance                                                                                         | R <sub>DSON_B1_P</sub>  | I <sub>SW</sub> = -1A                                                                                |      | 35             |        | mΩ                |

| NMOS On-Resistance                                                                                         | R <sub>DSON_B1_N</sub>  | I <sub>SW</sub> = 1A                                                                                 |      | 13             |        | mΩ                |

| Dynamic Voltage Scaling Rate (1)                                                                           |                         |                                                                                                      |      | 3              |        | mV/μs             |

| Output Pull-Down Resistance (1)                                                                            | $R_{PD\_B1}$            | Enabled when regulator disabled                                                                      |      | 4.4            | 8.75   | Ω                 |

| Buck1 - Bypass Mode (V <sub>IN_B1</sub> = 3.3V)                                                            |                         |                                                                                                      |      |                |        |                   |

| Input Voltage for Bypass Mode                                                                              | $V_{IN\_B1}$            |                                                                                                      | 2.7  | 3.3            | 5.5    | V                 |

| PMOS On-Resistance                                                                                         | R <sub>DSON_BY1_P</sub> | I <sub>SW_B1</sub> = -1A                                                                             |      | 35             |        | mΩ                |

| PMOS Current Limit, Warning                                                                                |                         | Compared to current limit, cycle-<br>by-cycle                                                        | 67.5 | 75             | 82.5   | %                 |

|                                                                                                            |                         | B1_ILIM_SET[1:0] = 00                                                                                | 4.8  | 5.6            | 6.3    |                   |

| PMOS Current Limit Shutdown<br>(Shut down after deglitch time and stay off<br>for off-time)                |                         | B1_ILIM_SET[1:0] = 01                                                                                | 4.1  | 4.8            | 5.5    | _                 |

|                                                                                                            | I <sub>LIM_BY1</sub>    | B1_ILIM_SET[1:0] = 10                                                                                | 2.9  | 3.8            | 4.7    | - A               |

|                                                                                                            |                         | B1_ILIM_SET[1:0] = 11                                                                                | 1.8  | 3.0            | 4.3    |                   |

| Internal PMOS Current Shutdown Deglitch Time <sup>(1)</sup>                                                | t <sub>DEG_BY1</sub>    |                                                                                                      |      | 5              |        | μs                |

| Internal PMOS Current Shutdown<br>Off-Time (Retry Time) (1)                                                | t <sub>OFF_BY1</sub>    |                                                                                                      |      | 10             |        | ms                |

| Internal PMOS Soft-Start (1)                                                                               | t <sub>SS_BY1</sub>     | С <sub>оит</sub> = 66µF                                                                              |      | 500            |        | μs                |

NOTE: 1. Guaranteed by design, not tested in production.

| PARAMETER SYMBOL CONDI                                                           |                        | CONDITIONS                                                              | MIN   | TYP            | MAX    | UNIT              |

|----------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------|-------|----------------|--------|-------------------|

| Buck2/3                                                                          |                        |                                                                         | •     |                |        |                   |

| Input Operating Voltage Range                                                    | $V_{IN\_Bx}$           |                                                                         | 2.7   |                | 5.5    | V                 |

| Buck2 Output Voltage Range 1 (1)                                                 | V <sub>OUT_B2_R1</sub> | Configurable in 9.375mV steps                                           | 0.6   |                | 2.991  | V                 |

| Buck2 Output Voltage Range 2 (1)                                                 | V <sub>OUT_B2_R2</sub> | Configurable in 12.5mV steps                                            | 0.8   |                | 3.9875 | V                 |

| Buck3 Output Voltage Range (1)                                                   | V <sub>OUT_B3</sub>    | Configurable in 12.5mV steps                                            | 0.8   |                | 3.9875 | V                 |

| Standby Supply Current                                                           | I <sub>Q_Bx</sub>      | No switch, $V_{OUT\_Bx} = 103\%$ set point,<br>$T_J = -40$ °C to +125°C |       | 30             | 60     | μA                |

| Output Voltage Accuracy                                                          | $\Delta V_{OUT\_Bx}$   | V <sub>OUT_Bx</sub> = default CMI voltage,<br>continuous PWM mode       | -1    |                | 1      | %                 |

|                                                                                  | _                      | V <sub>OUT_Bx</sub> = default CMI voltage, PSM <sup>(1)</sup>           | -2    |                | 2      | %                 |

| Power Good Threshold                                                             | $V_{PG\_Bx}$           | V <sub>OUT_Bx</sub> rising                                              | 90    | 93             | 96     | %V <sub>NOM</sub> |

| Power Good Hysteresis                                                            | $V_{PG\_HYS\_Bx}$      |                                                                         |       | 3              |        | $%V_{NOM}$        |

| Over-Voltage Fault Threshold                                                     | $V_{\text{OV\_Bx}}$    | V <sub>OUT_Bx</sub> rising                                              | 107.5 | 110.5          | 114    | %V <sub>NOM</sub> |

| Over-Voltage Fault Hysteresis                                                    | $V_{OV\_HYS\_Bx}$      |                                                                         |       | 3              |        | %V <sub>NOM</sub> |

| Switching Frequency                                                              | f <sub>oscx</sub>      | $T_J = -40^{\circ}C \text{ to } +125^{\circ}C$                          | -5%   | 1.125/<br>2.25 | 5%     | MHz               |

| Soft-Start Period                                                                | t <sub>SS_Bx</sub>     | BUCK_SS = 0, 10% to 90% of V <sub>NOM</sub>                             |       | 500            | 750    | μs                |

|                                                                                  |                        | B2_ILIM_SET[1:0] = 00                                                   | 3.4   | 4.2            | 5.0    |                   |

| Buck2 Current Limit, Cycle-by-Cycle (Accuracy is only valid for register default | I <sub>LIM_B2</sub>    | B2_ILIM_SET[1:0] = 01                                                   | 2.9   | 3.6            | 4.4    | A                 |

| setting, B2_ILIM_SET[1:0] = 00)                                                  |                        | B2_ILIM_SET[1:0] = 10                                                   | 2.3   | 3.0            | 3.8    |                   |

|                                                                                  |                        | B2_ILIM_SET[1:0] = 11                                                   | 1.7   | 2.5            | 3.3    |                   |

|                                                                                  |                        | B3_ILIM_SET[1:0] = 00                                                   | 3.1   | 4.0            | 4.8    |                   |

| Buck3 Current Limit, Cycle-by-Cycle                                              |                        | B3_ILIM_SET[1:0] = 01                                                   | 2.6   | 3.4            | 4.2    | _                 |

| (Accuracy is only valid for register default setting, B3_ILIM_SET[1:0] = 01)     | I <sub>LIM_B3</sub>    | B3_ILIM_SET[1:0] = 10                                                   | 2.1   | 2.8            | 3.6    | Α                 |

|                                                                                  |                        | B3_ILIM_SET[1:0] = 11                                                   | 1.6   | 2.3            | 2.9    |                   |

| Current Limit, Warning                                                           |                        | Compared to current limit, cycle-<br>by-cycle                           | 67.5  | 75             | 82.5   | %                 |

| PMOS On-Resistance                                                               | R <sub>DSON_Bx_P</sub> | $I_{SW\_Bx} = -1A$                                                      |       | 80             |        | mΩ                |

| NMOS On-Resistance                                                               | R <sub>DSON_Bx_N</sub> | I <sub>SW_Bx</sub> = 1A                                                 |       | 55             |        | mΩ                |

| Dynamic Voltage Scaling Rate (1)                                                 |                        |                                                                         |       | 3              |        | mV/µs             |

| Output Pull-Down Resistance (1)                                                  | R <sub>PD_Bx</sub>     | Enabled when regulator disabled                                         |       | 6.6            | 13     | Ω                 |

NOTE: 1. Guaranteed by design, not tested in production.

| PARAMETER                                                              | SYMBOL                        | CONDITIC                                          | ONS                      | MIN | TYP  | MAX    | UNITS             |

|------------------------------------------------------------------------|-------------------------------|---------------------------------------------------|--------------------------|-----|------|--------|-------------------|

| LDO1/2                                                                 |                               |                                                   |                          |     |      |        |                   |

| Operating Voltage Range                                                | V <sub>IN_A</sub>             |                                                   |                          | 2.7 |      | 5.5    | V                 |

| Output Voltage Range 1 (1)                                             | V <sub>OUT_LDOx_R1</sub>      | Configurable in 9.375m                            | V steps                  | 0.6 |      | 2.991  | V                 |

| Output Voltage Range 2 (1)                                             | V <sub>OUT_LDOx_R2</sub>      | Configurable in 12.5mV                            | steps                    | 0.8 |      | 3.9875 | V                 |

| Output Current                                                         | I <sub>OUT_LDOx</sub>         |                                                   |                          |     | 300  |        | mA                |

| Output Voltage Accuracy                                                | $\Delta V_{\text{OUT\_LDOx}}$ | $I_{OUT\_LDOx} = 5mA, T_J = -40$                  | 0°C to +125°C            | -1  |      | 1      | %                 |

|                                                                        |                               |                                                   | f = 1kHz                 |     | 52   |        | dB                |

| Power Supply Rejection Ratio (1)                                       | PSRR                          | $I_{OUT\_LDOx} = 20mA,$<br>$V_{OUT\_LDOx} = 1.8V$ | f = 10kHz                |     | 32   |        | dB                |

|                                                                        |                               |                                                   | f = 2.25MHz              |     | 51   |        | dB                |

| Supply Current                                                         | $I_{Q\_LDOx}$                 | Regulator enabled, no le                          | oad                      |     | 34   | 50     | μΑ                |

| Soft-Start Time                                                        | t <sub>SS_LDOx</sub>          | 10% to 90% of V <sub>NOM</sub>                    |                          |     | 300  | 430    | μs                |

| Power Good Threshold                                                   | $V_{PG\_LDOx}$                | V <sub>OUT_LDOx</sub> rising                      |                          | 87  | 90.5 | 95     | %V <sub>NOM</sub> |

| Power Good Hysteresis                                                  | $V_{PG\_HYS\_LDOx}$           |                                                   |                          |     | 4    |        | %V <sub>NOM</sub> |

| Over-Voltage Fault Threshold                                           | $V_{OV\_LDOx}$                | V <sub>OUT_LDOx</sub> rising                      |                          | 105 | 110  | 115    | %V <sub>NOM</sub> |

| Over-Voltage Fault Hysteresis                                          | V <sub>OV_HYS_LDOx</sub>      |                                                   |                          |     | 3    |        | %V <sub>NOM</sub> |

| Discharge Resistance (1)                                               | R <sub>DIS_LDOx</sub>         |                                                   |                          |     | 50   | 125    | Ω                 |

| Dropout Voltage                                                        | V <sub>DROP_LDOx</sub>        | I <sub>OUT_LDOx</sub> = 220mA, V <sub>OUT_</sub>  | _ <sub>LDOx</sub> = 2.7V |     |      | 150    | mV                |

|                                                                        |                               | LDOx_ILIM_SET[1:0] =                              | 00                       | 80  | 155  | 230    |                   |

| Output Current Limit                                                   |                               | LDOx_ILIM_SET[1:0] = 01                           |                          | 180 | 245  | 310    | mA                |

| Output Current Limit                                                   | I <sub>LIM_LDOx</sub>         | LDOx_ILIM_SET[1:0] =                              | 10                       | 300 | 365  | 430    | IIIA              |

|                                                                        |                               | LDOx_ILIM_SET[1:0] = 11                           |                          | 400 | 460  | 520    | 1                 |

| LDO1/2 Load Switch Mode - Bypass Mod                                   | de                            |                                                   |                          |     |      |        |                   |

| Operating Voltage Range LDO1/2                                         | V <sub>IN_A</sub>             |                                                   |                          | 2.7 |      | 5.5    | V                 |

| PMOS On-Resistance                                                     | R <sub>DSON_LDOx_P</sub>      |                                                   |                          |     | 320  |        | mΩ                |

| Supply Current                                                         | $I_{Q\_LDOx}$                 | Load switch enabled, no                           | o load                   |     | 42   | 60     | μΑ                |

|                                                                        |                               | LDOx_ILIM_SET[1:0] =                              | 00                       | 80  | 155  | 230    |                   |

| Output Current Limit                                                   |                               | LDOx_ILIM_SET[1:0] =                              | 01                       | 180 | 245  | 310    | 1                 |

| Output Current Limit                                                   | I <sub>LIM_LDOx</sub>         | LDOx_ILIM_SET[1:0] = 10                           |                          | 300 | 365  | 430    | - mA              |

|                                                                        |                               | LDOx_ILIM_SET[1:0] =                              | 11                       | 400 | 460  | 520    |                   |

| Internal PMOS Current Shutdown Deglitch Time (1)                       | t <sub>DEG_SD_LDOx</sub>      |                                                   |                          |     | 5    |        | μs                |

| Internal PMOS Current Shutdown Off<br>Time (Retry Time) <sup>(1)</sup> | t <sub>OFF_LDOx</sub>         |                                                   |                          |     | 10   |        | ms                |

| Internal PMOS Soft-Start (1)                                           |                               | Only used with 3.3V inp                           | out, Coυτ = 1μF          |     | 10   |        | mV/μs             |

NOTE: 1. Guaranteed by design, not tested in production.

$(V_{IN} = 3.3V, T_J = +25^{\circ}C, \text{ unless otherwise noted.})$

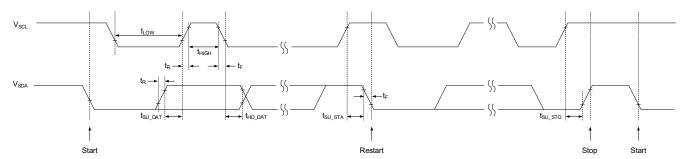

| PARAMETER                     | SYMBOL                         | CONDITIONS            | MIN  | TYP | MAX  | UNITS |

|-------------------------------|--------------------------------|-----------------------|------|-----|------|-------|

| I <sup>2</sup> C Interface    | •                              |                       |      | •   | •    | •     |

| SCL Clock Frequency           | f <sub>SCL</sub>               |                       | 0    |     | 1000 | kHz   |

| SCL, SDA Input Low Voltage    | V <sub>IL</sub>                |                       |      |     | 0.4  | V     |

| SCL, SDA Input High Voltage   | V <sub>IH</sub>                |                       | 1.25 |     |      | V     |

| SDA Leakage Current           | ΙL                             | V <sub>SDA</sub> = 5V |      |     | 1    | μΑ    |

| SDA Output Low Voltage        | V <sub>OL</sub>                | I <sub>OL</sub> = 5mA |      |     | 0.35 | V     |

| SCL Low Period                | t <sub>LOW</sub>               |                       | 0.5  |     |      | μs    |

| SCL High Period               | t <sub>HIGH</sub>              |                       | 0.26 |     |      | μs    |

| SDA Data Setup Time           | t <sub>SU_DAT</sub>            |                       | 50   |     |      | ns    |

| SDA Data Hold Time            | t <sub>HD_DAT</sub>            |                       | 0    |     |      | ns    |

| Start Setup Time              | t <sub>SU_STA</sub>            | For start condition   | 260  |     |      | ns    |

| Stop Setup Time               | t <sub>su_sto</sub>            | For stop condition    | 260  |     |      | ns    |

| Capacitance on SCL or SDA Pin | С                              |                       |      |     | 10   | pF    |

| SCL/SDA Rise/Fall Time        | t <sub>R</sub> /t <sub>F</sub> | Device requirement    |      |     | 120  | ns    |

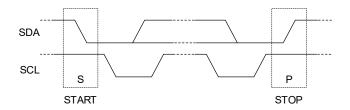

# I<sup>2</sup>C TIMING DIAGRAM

Figure 1. I<sup>2</sup>C Timing Diagram

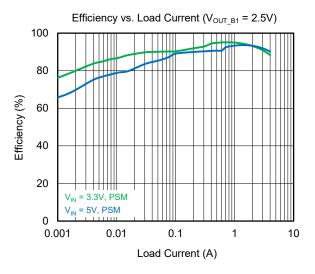

# TYPICAL PERFORMANCE CHARACTERISTICS

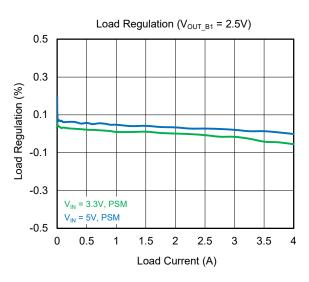

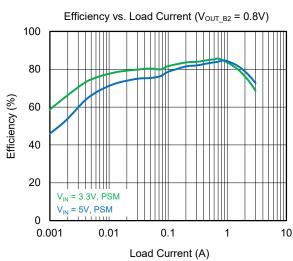

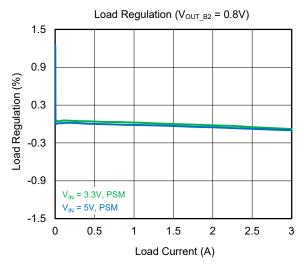

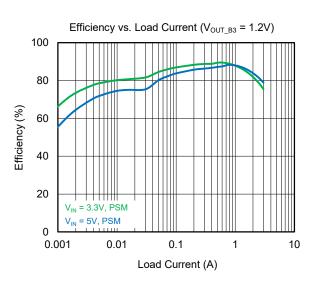

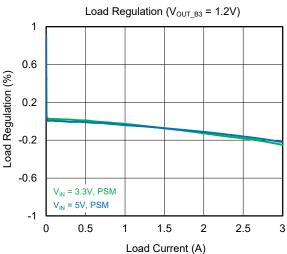

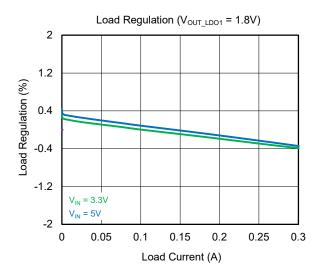

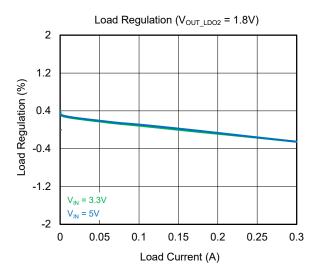

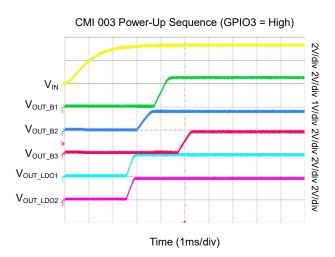

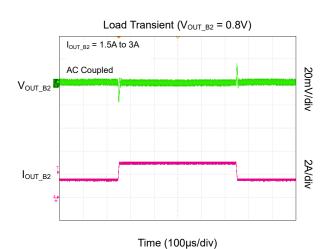

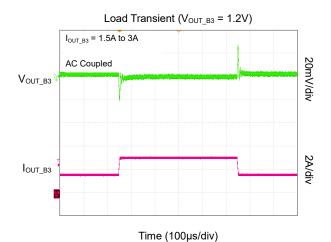

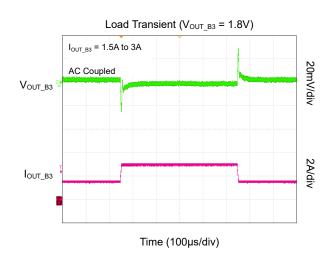

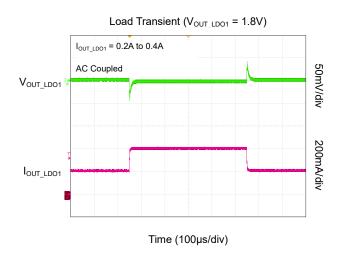

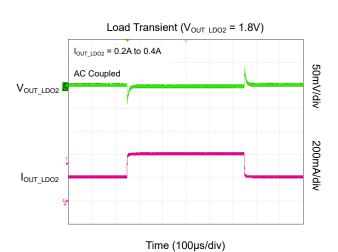

$T_J$  = +25°C,  $V_{IN}$  = 3.3V, f = 2.25MHz, L = 0.47 $\mu$ H (DCR = 7.3m $\Omega$ ), unless otherwise noted.

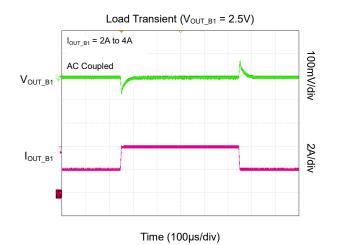

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_J$  = +25°C,  $V_{IN}$  = 3.3V, f = 2.25MHz, L = 0.47 $\mu$ H (DCR = 7.3m $\Omega$ ), unless otherwise noted.

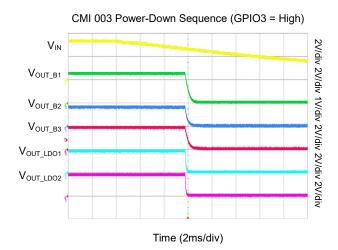

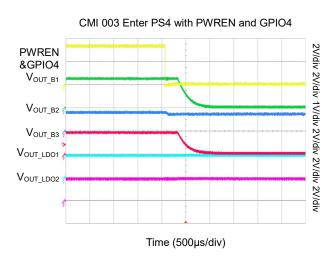

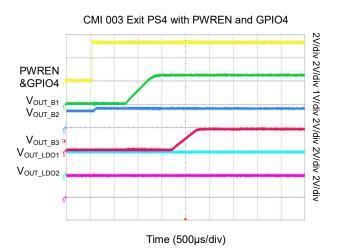

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_J$  = +25°C,  $V_{IN}$  = 3.3V, f = 2.25MHz, L = 0.47 $\mu$ H (DCR = 7.3m $\Omega$ ), unless otherwise noted.

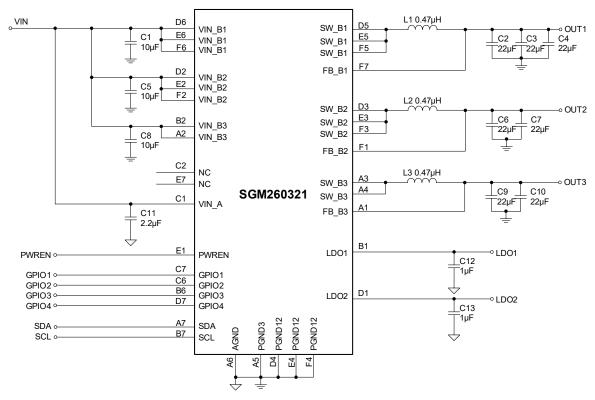

# TYPICAL APPLICATION CIRCUIT

Figure 2. Typical Application Circuit

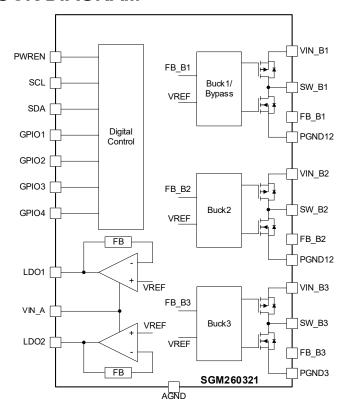

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 3. Block Diagram

# **DETAILED DESCRIPTION: SYSTEM CONTROL**

#### General

The SGM260321 represents an integrated power management IC engineered for next-generation solid state drive controllers. This system-on-chip solution delivers three high efficient Buck converters and two LDOs, specifically optimized for mission-critical storage controllers and industrial automation processors. It integrates three Buck converters, two LDOs, achieving space-saving and cost-effective power delivery through advanced integration. SGM260321 contains a master controller governing critical operations: start-up sequence, turn-on delay, turn-off delay, voltage of each channel, soft-start time, sleep or DPSLP state, and fault conditions.

System parameters can be dynamically adjusted through  $I^2C$  interface, without physical hardware modifications. A built-in bypass switch for Buck1 enhances sequencing flexibility in 3.3V power architectures.

The master controller continuously tracks all output channels, transmitting status information through  $I^2C$  protocol communication and hardware-level status signals. User can configure fault thresholds and response mechanisms via  $I^2C$  interface, including selective fault masking capabilities.

Factory-defined parameters for SGM260321 are established through Code Matrix Index (CMI). The device supports extensive customization for different GPIO configuration and each channel's voltage and current limit, etc. It is specifically defined for each SGM260321 CMI part number.

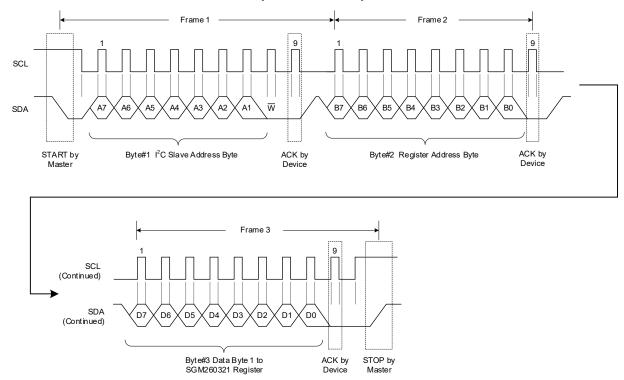

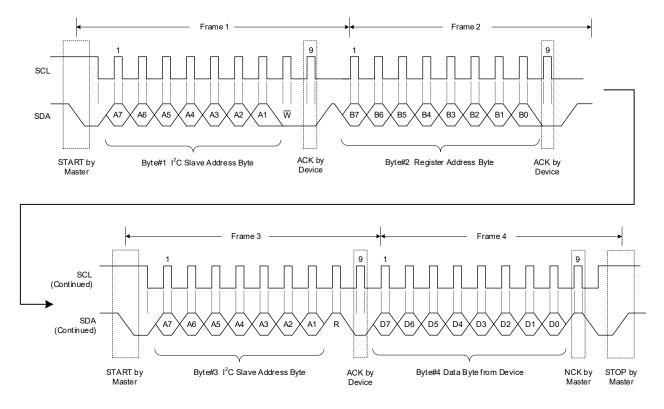

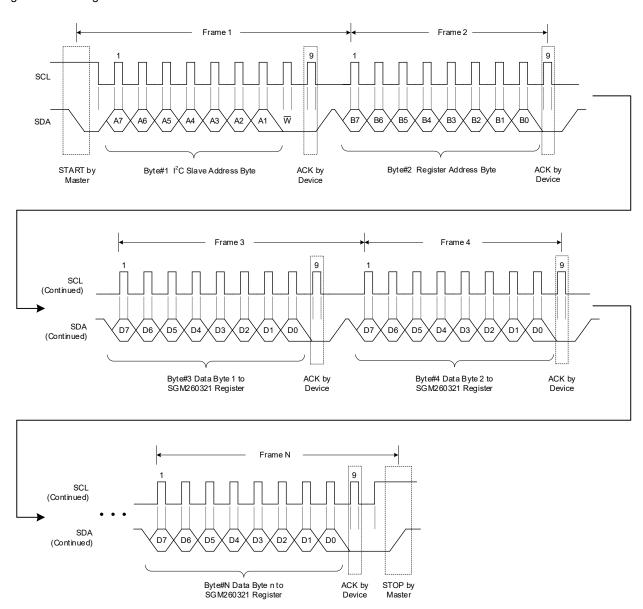

## I<sup>2</sup>C Serial Interface

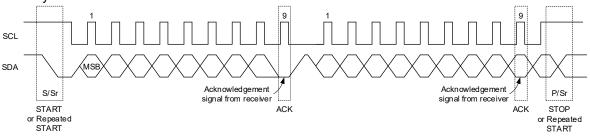

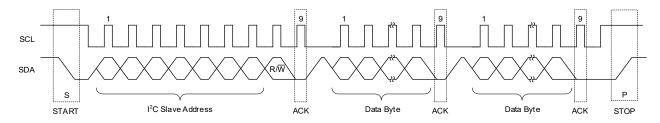

Standard I<sup>2</sup>C interface is used to program SGM260321 parameters and get status reports. It operates as a slave device, and can be configured by factory to one of four 7-bit slave addresses. The base address incorporates an extension bit which defining the operation is read or write.

Refer to each specific CMI for the IC's slave address.

| 7-Bit Slave Address |          | 8-Bit Write<br>Address | 8-Bit Read<br>Address |

|---------------------|----------|------------------------|-----------------------|

| 0x25                | 010 0101 | 0x4A                   | 0x4B                  |

| 0x27                | 010 0111 | 0x4E                   | 0x4F                  |

| 0x67                | 110 0111 | 0xCE                   | 0xCF                  |

| 0x6B                | 110 1011 | 0xD6                   | 0xD7                  |

The I<sup>2</sup>C controller does not have a timeout feature. However, whenever it detects a new start signal, it will immediately stop and reset the current data processing, even if a valid data packet is being transmitted.

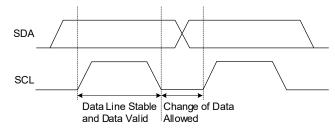

I<sup>2</sup>C is 2-wire serial communication interface that can connect one (or more) master device(s) to some slave devices for two-way communication. The bus lines are named serial data (SDA) and serial clock (SCL). The SDA pin operates in open-drain configuration and requires an external pull-up resistor. Signal transitions on this pin must comply with the timing parameters specified in the Electrical Characteristics on page 8.

# I<sup>2</sup>C Registers

The SGM260321 integrates internal configuration registers that store critical operational parameters, including output voltage setting, start-up sequencing, fault detection thresholds, and fault mask configurations. These registers provide the core programmability of the device. Two register categories are implemented.

#### **Basic Volatile**

These registers are R/W (read/write) and R (read only). After power-up, user can modify R/W registers to adjust IC functions, such as masking faults. R registers display IC status, including faults. All changes are lost on power cycle. Default values are fixed and cannot be altered by the factory or user.

#### **Basic Non-Volatile**

These registers are R/W and R types. Once the IC is powered up, user can change the R/W registers to adjust functions like output voltage, start-up delay, and current limit thresholds. These modifications are lost when power is cycled. The default values can be set at the factory to optimize the IC for specific applications. Please contact sales for custom options and minimum order quantities. When updating only certain bits within a register, be careful not to alter the other bits, as doing so may cause unexpected device behavior.

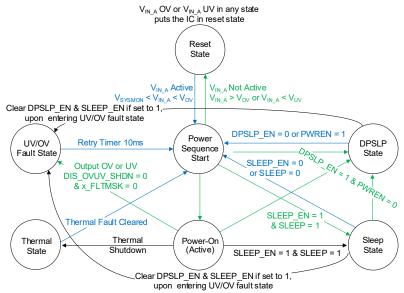

#### **State Machine**

Figure 4 shows the SGM260321 internal state machine.

Figure 4. State Machine

#### **Reset State**

During the reset state, the SGM260321 monitors VIN\_A until it stabilizes within the acceptable range specified by  $V_{\text{SYSMON}}$  and  $V_{\text{OV}}$ . In this state, all regulators remain off and the outputs are maintained at a low level. When the input voltage drops below the  $V_{\text{UV}}$  threshold or exceed the  $V_{\text{OV}}$  limit, the IC will revert to the reset state regardless of its current operating state.

### **Power Sequence Start State**

During the power sequence start state, the system is in a transitional phase as the regulators begin their activation. During this period, outputs are activated and start their ramp-up. As soon as the regulators stabilize and enter regulation, the IC promptly shifts to the power-on, sleep or DPSLP state.

#### Power-On (Active) State

The active state represents normal operation, where the input voltage remains within the acceptable range, all outputs are enabled, and no faults are detected.

## **Sleep State**

In sleep state, each output can be configured to remain on/off. When transitioning into/out of sleep mode, the outputs follow their programmed sequencing delay time for turning on/off.

The IC can enter the sleep state through the SLEEP and SLEEP EN registers. Table 1 shows the conditions

required for this transition. In sleep mode, the SGM260321's  $I^2C$  interface remains active. The IC exits sleep mode once the entry conditions are no longer met.

If an output over-voltage (OV) or under-voltage (UV), occurs in sleep mode, the IC resets SLEEP\_EN and DPSLP\_EN bits and returns to the power-on state.

Table 1. Sleep Mode Truth Table

| SLEEP_EN Bit<br>(0x04h) | SLEEP Bit<br>(0x04h) | Enter Sleep Mode |

|-------------------------|----------------------|------------------|

| 0                       | 0                    | No               |

| 0                       | 1                    | No               |

| 1                       | 0                    | No               |

| 1                       | 1                    | Yes              |

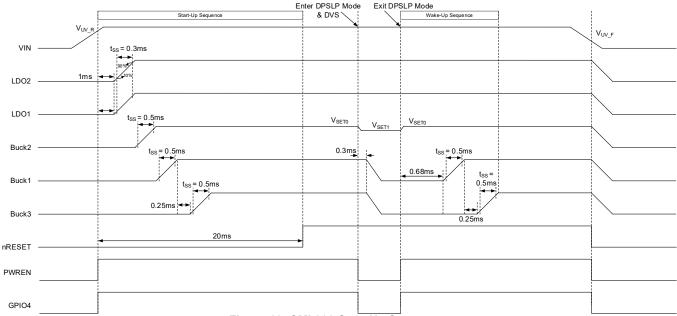

#### **DPSLP State**

The DPSLP state is designed for even lower power consumption than the sleep mode. While similar to the sleep state, DPSLP state has different entry and exit configurations. Each output can be individually set to be on/off in DPSLP mode, with setting that may differ from those in the sleep state. When transitioning into/out of DPSLP mode, the outputs follow their programmed sequencing delay time for turning on/off.

The device can enter the DPSLP mode through pulling the PWREN pin low and setting DPSLP = 1. Table 2 shows the conditions required for this transition. In DPSLP mode, the  $I^2C$  interface remains active. The device exits DPSLP mode once the entry conditions are no longer met.

If an output over-voltage (OV) or under-voltage (UV) occurs in DPSLP state, the IC resets SLEEP\_EN and DPSLP EN bits and returns to the power-on state.

**Table 2. DPSLP Mode Truth Table**

| PWREN Pin | DPSLP_EN Bit<br>(0x04h) | Enter DPSLP Mode |

|-----------|-------------------------|------------------|

| 0         | 1                       | Yes              |

| 1         | 1                       | No               |

| 0         | 0                       | No               |

| 1         | 0                       | No               |

#### **Thermal State**

When the chip temperature exceeds the thermal shutdown temperature, all regulators automatically turn off to protect the IC and the nRESET signal is pulled low. The TMSK control bit stops the nIRQ from triggering when temperature exceeds the warning level  $(T_J > T_{WARN})$ , but the TWARN status bit still shows the overheating condition even when TMSK bit is set to 1.

#### **UV/OV Fault State**

When any regulator's output goes above the over-voltage (OV) threshold or below the under-voltage (UV) threshold after soft-start, the IC enters UV/OV state. All regulators turn off, and the nRESET is pulled low. The system tries to restart after a 10ms delay. If the OV/UV condition remains, the IC returns to UV/OV state, repeating this cycle until the fault is removed or input power is disconnected. While over-current conditions do not directly trigger UV/OV state, sustained over-current causing UV conditions will lead to PMIC enter UV/OV state.

Each regulator provides OV/UV fault control through mask bits (x\_OV\_FLTMSK/x\_UV\_FLTMSK). UV/OV fault state is enabled only when both conditions are met: the fault mask bits are cleared to 0 and the DIS\_OVUV\_SHDN = 0. When fault mask is active, the nIRQ signal remains high during faults and PMIC does not enter UV/OV state. But OV/UV still provides the over-/under-voltage fault status even if x\_OV\_FLTMSK/ x\_UV\_FLTMSK = 1.

#### Start-Up/Shutdown

The IC automatically moving from the reset state to the power sequence start state upon input power is applied.

Then PMIC transitions to either power-on, sleep, or DPSLP states is determined by input conditions defined in Table 1 and Table 2. A standard start-up sequence progresses from reset to power-on state when input power is applied. For  $V_{\text{IN}}$ , POWER\_OFF bit or SYS\_EN shutdown, there is no shutdown sequence, all channels are shutdown at the same time.

#### Sequencing

The SGM260321 delivers advanced sequencing control for multi-rail power systems. Each of its five outputs has four programmable parameters: input trigger, turn-on delay, turn-off delay, and output voltage. Buck regulators additionally support soft-start time adjustment. All parameters are programmed through dedicated configuration registers, enabling application specific optimization without hardware changes. Detailed sequencing profiles for this device and related parameters are provided at the end of datasheet. Contact sales for custom sequencing configurations.

#### **Input Trigger**

The input trigger determines when a regulator turns on. Each output channel can use independent trigger sources, including internal channel's power ok (POK), internal  $V_{\text{IN}\_A}$  power ok ( $V_{\text{SYSMON}}$ ), and external signal through GPIO pin.

This flexibility enables system designers to implement a wide range of sequencing possibilities with external power supply or host controllers. For instance, configuring Buck1 as LDO1's input trigger, LDO1 will not turn on until Buck1 achieves stable regulation. Input triggers are predefined at the factory and can only be modified through a custom CMI configuration.

Additionally, GPIOx outputs can be linked to an internal power supply's POK signal to trigger external power supply sequencing. Also, GPIOx inputs can connect to an external power supply's power good output, serving as an input trigger for an SGM260321 supply.

#### **Turn-On Delay**

The turn-on delay is the time from when an input trigger activates to the output begins turning on. This timing parameter for each output is set using the  $x_ON_DLY[1:0]$  bits in the  $I^2C$  registers. Do not change this  $x_ON_DLY[1:0]$  bits when PMIC is powered on. Change this turn-on delay when CMI configuration is initially determined.

### **Turn-Off Delay**

The turn-off delay is the time from sleep/DPSLP mode activation to the output begins shutting down. Each output's delay time is set using the x\_OFF\_DLY[4:0] bits in the I<sup>2</sup>C registers. The setting can be adjusted during operation but is temporary, it will reset to default value when power is recycled.

#### **Soft-Start Time**

The soft-start time for all Buck converters is managed through the BUCK\_SS control bit. Setting this bit to 0 selects a 500µs start-up period, while setting it to 1 set the period to 250µs. Though adjustable after power-up, the setting is temporary and resets to factory defaults when power is recycled.

#### **Output Voltage**

The output voltage defines the target voltage for each regulator. For Buck converters, this value is set through I<sup>2</sup>C using Bx\_VSET0[7:0] bits (active mode) and Bx\_VSET1[7:0] bits (DVS mode). LDOs utilize a single LDOx\_VSET[7:0] register for voltage configuration. All output voltages can be adjusted during operation, though new setting is temporary and resets to factory defaults when power is recycled.

Output voltages can be adjusted while the IC is operating. For significant voltage changes, use multiple small steps instead of a single large adjustment. This avoids accidental triggering of over-voltage (OV) or under-voltage (UV) protection because the fault detection thresholds update immediately, but the output voltage changes more slowly.

#### **Dynamic Voltage Scaling (DVS)**

The three Buck converters support dynamic voltage scaling through either the  $I^2C$  interface or GPIO pins. This feature enables power optimization by dynamically adjusting processor voltage based on workload demands. DVS operates within the active state, modifying output voltages without changing the IC's operational mode.

Each Buck converter maintains its Bx\_VSET0 setting during normal operation and switches to Bx\_VSET1 when the DVS trigger activates. Voltage transitions occur seamlessly while the IC remains fully operational.

The IC can enter DVS mode through  $I^2C$ , a GPIO pin, or by transitioning into sleep mode. DVS can be applied to all Buck converters simultaneously via  $I^2C$ . When using  $I^2C$ , the user can choose between two different configurations for enabling DVS. However, note that DVS via  $I^2C$  is disabled if EN DVS  $I^2C = 0$ .

## Enable DVS via I2C\_DVS\_ON Bit

Set EN\_DVS\_I2C = 1 and SEL\_DVS\_IN = 0 through  $I^2C$ . Writing 1 to I2C\_DVS\_ON enables DVS mode, while writing 0 disables it.

#### **Enable DVS when Enter Sleep State**

With EN\_DVS\_I2C = 1 and SEL\_DVS\_IN = 1, entering sleep state automatically activates DVS mode (I2C DVS ON value becomes irrelevant).

Note that the IC cannot be configured to enter DVS in DPSLP state. Table 3 summarizes I<sup>2</sup>C DVS functionality.

Table 3. I<sup>2</sup>C DVS Control

| EN_DVS_I2C | SEL_DVS_IN | I2C_DVS_ON | DVS Mode             |

|------------|------------|------------|----------------------|

| 0          | X          | X          | Off                  |

| 1          | 0          | 0          | Off                  |

| 1          | 0          | 1          | On                   |

| 1          | 1          | Х          | On in Sleep<br>State |

# Input Voltage Monitoring (V<sub>SYSMON</sub>)

The SGM260321 continuously tracks input voltages on VIN\_A pin to maintain system operational limits. Initial activation occurs when  $V_{\text{IN}\_A}$  exceeds the under-voltage rising threshold, but outputs remain disabled until  $V_{\text{IN}\_A}$  rises above the programmable  $V_{\text{SYSMON}}$  (2.7V to 4.2V).

The nIRQ pin pulls low if  $V_{IN\_A}$  drops below  $V_{SYSMON}$ , while outputs continue normal operation. Full system shutdown triggers when  $V_{IN\_A}$  falls below  $V_{UV}$ .

VSYSSTAT bit flags input status (1 =  $V_{IN\_A}$  <  $V_{SYSMON}$ , 0 =  $V_{IN\_A}$  >  $V_{SYSMON}$ ),  $V_{IN\_A}$  <  $V_{SYSMON}$  will pull nIRQ low, it is latched and required I<sup>2</sup>C VSYSSTAT bit in register 0x00h reads to clear, and this fault is masked via VSYSMSK bit by default. SGM260321 also has a real-time VSYSDAT status bit.

#### **Fault Protection**

The SGM260321 has multiple levels of fault protections, including:

- Input Under-Voltage/Over-Voltage

- Output Over-Voltage

- Output Under-Voltage

- Output Current Limit and Short-Circuit

- Thermal Warning

- Thermal Shutdown

The IC implements two types of registers for each fault condition: fault bits and mask bits. Fault bits are always valid, even when masking is active. Mask bits determine whether a fault triggers the nIRQ signal. User can selectively mask faults through I<sup>2</sup>C configuration. Unmasked faults immediately pull low the nIRQ pin, which remains low until both the fault clears and the status register is read via I<sup>2</sup>C. Masked faults can still be read in the fault bit.

#### Input Voltage (UV)

The SGM260321 continuously checks the input voltage at the VIN\_A pin to detect UV condition. If the voltage drops below the  $V_{\text{UV}}$  threshold, the IC enters the reset state, disabling all outputs and pulling the nRESET signal low. When the input voltage rises above  $V_{\text{SYSMON}}$  and  $V_{\text{UV}}$  rising threshold, the PMIC transitions to the active state, and begins normal start-up procedures.

#### Input Voltage (OV)

The SGM260321 monitors the input voltage at the VIN\_A pin for an over-voltage (OV) condition. The VIN\_OV\_SEL threshold is factory programmable between 3.8V and 5.7V. If the input voltage exceeds this threshold, the IC enters the reset state, turning off all outputs and asserting nRESET low. Once the input voltage drops below the  $V_{\rm OV}$  falling threshold, the IC transitions back to the power sequence start state and resumes normal start-up.

# Output (UV/OV)

The SGM260321 continuously checks all outputs for under-voltage (UV) and over-voltage (OV) conditions. When detecting a UV/OV fault, the IC enters the UV/OV fault state, disabling all outputs and pulling nRESET low. After a 10ms delay, the system restarts using the programmed start-up sequence.

During current limit conditions, output voltages may drop below UV thresholds, triggering system shutdown. To prevent this, user can mask the UV fault bits. Each output continues to report OV fault conditions through its fault bit, regardless of masking setting. Masking OV/UV faults prevents both nIRQ signal pulling low and entering UV/OV fault state, while maintaining real-time fault monitoring capability.

## **Output Current Limit**

The SGM260321 employs a two-level over-current protection strategy for the Buck converters and a single-level over-current protection for the LDOs.

For the Buck converters, Buck1 monitors peak switch current, while Buck2/Buck3 monitors valley switch current. The first protection level triggers when switch current exceeds 75% of the current limit for 16 consecutive cycles. It logs Bx\_ILIM\_WARN fault status and pulls the nIRQ pin low if unmasked. The second level of protection occurs when the current reaches the cycle-by-cycle limit. In response, the Buck converter limits the peak switch current for Buck1 and the valley switch current for Buck2 and Buck3 during each switching cycle. This reduces duty cycle and potentially causes output voltage drop. If this triggers an unmasked under-voltage condition, all outputs are disabled for 10ms before restarting.

For the LDOs, the over-current thresholds are determined by each LDO's output current limit setting. When the output current reaches this threshold, the LDO restricts the output current, causing the output voltage to drop. If this results in a UV condition, all supplies are turned off for 10ms before restarting.

The over-current fault limits for each output can be adjusted via  $I^2C$ .

All current limit thresholds are configurable through I<sup>2</sup>C registers.

#### Thermal Warning and Thermal Shutdown

The SGM260321 continuously tracks its internal die temperature. When the die temperature exceeds the +125°C warning threshold, the nIRQ is pulled low. If temperatures rises further to the +155°C shutdown limit, all outputs are immediately disabled. The thermal warning is mask via I<sup>2</sup>C by default, though the status bit still reflects temperature conditions even when masked. Masking only prevents the fault from being reported by nIRQ.

#### **PWREN**

The PWREN pin controls the IC's operational mode selection between power-on state and DPSLP state. PWREN has a bidirectional filter to prevent false triggering. When pulled low, user can program the Bucks and LDOs to either maintain operation or power down, enabling system-wide power saving states through a single control signal.

## **GPIO CONFIGURATION**

**Table 4. Configurable GPIO Features**

| _             |                     | EXT_PG           |

|---------------|---------------------|------------------|

|               | Input<br>Functions  | DVS Control      |

|               |                     | SYS_EN           |

| GPIO          |                     | LSW LDO Control  |

| Configuration | Output<br>Functions | EXT_EN           |

|               |                     | nRESET           |

|               |                     | nIRQ (Interrupt) |

|               |                     | SYSMON           |

# **Input Functions**

## EXT\_PG

The IC provides an external input trigger (EXT\_PG) to coordinate start-up timing with additional power supplies. EXT\_PG can initiate one or multiple power rails, enabling seamless integration of external regulators into the system's start-up sequence. CMI setting designate the GPIO pin used for EXT\_PG functionality.

#### **DVS Control**

GPIOx can be configured as input pins for different Buck channel DVS control. Whenever GPIOx is pulled low, the channel enters DVS state and the input voltage switches from x VSET0[7:0] to x VSET1[7:0].

#### SYS EN

GPIOx can be configured as the system's enable pin. When GPIOx is pulled low, the system shuts down. If GPIOx is pulled high, the system starts using the programmed start-up sequence.

### **LSW LDO Control**

GPIOx can be configured as input pins for different LDO channel mode control. When GPIOx is pulled high, LDOx is set for LDO mode. If GPIOx is pulled low, LDOx is set for LSW mode. Do not change LDO's working mode after PMIC is powered on.

# **Output Functions**

#### **EXT EN**

The SGM260321 includes an enable function (EXT\_EN) for controlling external regulators or providing system control signals. This feature supports programmable input triggers and delay time to align with specific power sequencing requirements. The assigned GPIO pin for EXT\_EN operation is defined through CMI configuration.

#### **nRESET**

The SGM260321 includes a reset function to initiate system-level CPU/controller resets. The nRESET

signal pulls low during thermal shutdown events. This signal also pulls low instantly if input voltage exceeds OV threshold, drops below UV threshold, or when any outputs that are connected to nRESET functionality experience OV or UV situations. The CMI configuration determines which power rails are monitored for nRESET triggering.

Following system start-up, nRESET pulls high after a programmable delay period when input voltage and all connected channel's output voltage are above their respective thresholds. This delay interval (20ms ~ 100ms) is programmed through the TRST\_DLY[1:0] bits. CMI setting additionally assigns the dedicated GPIO pin for nRESET signal output and program which regulator outputs are monitored for nRESET functionality.

#### nIRQ (Interrupt)

The nIRQ interrupt output serves as a system processor alert signal, generated by various monitored conditions within the SGM260321. Individual fault conditions can be masked through the I<sup>2</sup>C interface. For more information about the available fault conditions, refer to the appropriate sections of this datasheet. nIRQ can be triggered from:

- Input Voltage Lower than V<sub>SYSMON</sub>.

- Die Temperature Above Warning Threshold.

- Buck Converter Exceeding Current Limit for 16 Consecutive Cycles after Soft-Start or the UV/OV Condition.

- LDO Regulator Exceeding Current Limit after Soft-Start or the UV/OV Condition.

If any of these faults occur, the nIRQ output is pulled low. After being pulled low, reading the interrupt status registers via I<sup>2</sup>C clears both the interrupt signal and status bit only when the fault is removed. If the fault persists, nIRQ remains low and the status bit stays unchanged. The relevant status registers are located at 0x00, 0x30, 0x40, 0x50, 0x60, and 0x65. The CMI configuration defines which GPIO serves as the nIRQ pin.

#### **SYSMON**

GPIOx pins can be configured to output active-low SYSMON signals for host system monitoring. It gets low when  $V_{\text{IN}\_A} < V_{\text{SYSMON}}$  falling threshold, and it gets high when  $V_{\text{IN}\_A} > V_{\text{SYSMON}}$ , It is a real-time signal.

# **DETAILED DESCRIPTION: BUCK CONVERTERS**

## **General Description**

The SGM260321 integrates three Buck converters: Buck1 provides a 4A output, while Buck2 and Buck3 each deliver 3A. Buck1 operates as a fixed-frequency, constant-off-time (COFT) controlled synchronous converter, whereas Buck2 and Buck3 use constant-on-time (COT) control. These Buck converters switch at either 1.125MHz or 2.25MHz and feature internal compensation, requiring only three small external components ( $C_{\text{IN}}$ ,  $C_{\text{OUT}}$ , and L) for operation.

To minimize noise in sensitive applications, the regulators incorporate a switching phase delay and offset. Additionally, all regulators support a range of standard and custom output voltages and can be controlled via the  $I^2C$  interface, enabling advanced power management capabilities.

Each Buck converter has its own dedicated input pin and power ground pin. To ensure optimal performance, each converter requires a dedicated input capacitor placed strategically to minimize power routing loops. Although the Buck converters have separate input pins, all inputs must be tied to the same voltage potential.

Buck1 can be configured as a bypass switch for systems operating with a 3.3V bus voltage. This bypass mode enables full sequencing functionality, allowing the 3.3V bus to serve as the input for other power supplies while maintaining proper sequencing to the downstream load.

The SGM260321 Buck regulators offer extensive configurability and can be easily adjusted via I<sup>2</sup>C, eliminating the need for PCB modifications when hardware requirements change. The following I<sup>2</sup>C controlled functions are available:

- Real-Time Monitoring of Power Good, Over-Voltage (OV), Under-Voltage and Current Limit

- Selective Fault Masking

- Dynamic Output Voltage Adjustment

- On/Off Control

- Soft-Start Ramp Configuration

- Switching Delay and Phase Control

- Power Save Mode

- Over-Current Thresholds Adjustment

## 100% Duty Cycle Operation

Buck1 supports 100% duty cycle operation, where the high-side FET remains continuously on. This creates a direct connection from the input to the output through the inductor, minimizing dropout voltage, an essential feature for battery-powered applications.

## **Operating Mode**

By default, all Buck converters operate in fixed-frequency PWM mode under medium to heavy loads. At light loads, it automatically transitions to a proprietary power-saving mode that reduces conduction losses by preventing negative inductor current.