# SGM62112

# 1.8A Switch Current Single Inductor **Buck-Boost Converter**

## GENERAL DESCRIPTION

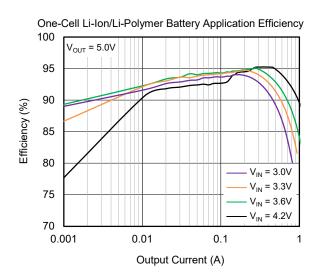

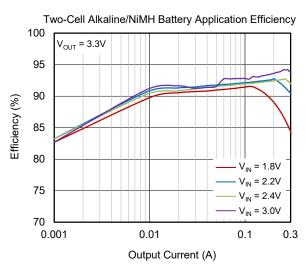

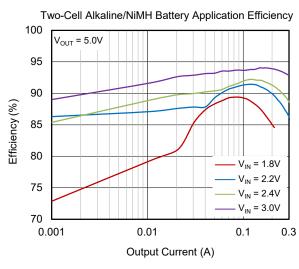

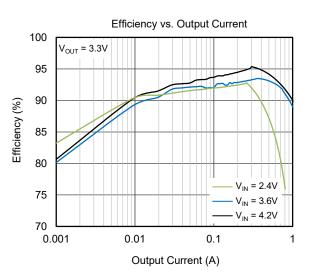

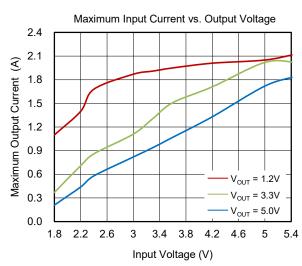

The SGM62112 is a fully-integrated synchronous Buck-Boost converter which is capable of operating from 1.8V to 5.5V input and suitable for battery powered applications such as 1-cell Li-lon battery, 2-cell or 3-cell Alkaline/NiMH batteries. The device supports up to 1200mA output current at higher than 3.8V input voltage, and 800mA output current at higher than 2.5V input voltage.

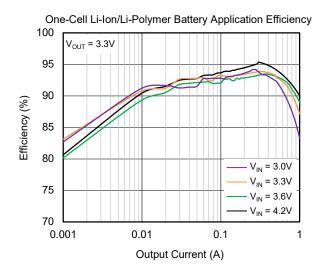

The SGM62112 adopts the current mode control with a fixed 1.4MHz (TYP) switching frequency to regulate the output voltage. In addition, the SGM62112 offers configurable light load PWM (pulse width modulation) operation or auto PFM (pulse frequency modulation) mode via MODE/SYNC pin configuration. PFM mode enables higher light load efficiency, while forced PWM operation ensures constant switching throughout entire load range.

The SGM62112 offers various protection features to improve device robustness such as soft-start to reduce inrush current during startup, cycle-by-cycle over-current protection and thermal shutdown protection. In addition, the device features true load disconnect when the EN pin is pulled low.

The SGM62112 is available in a Green TDFN-3×3-10L package.

#### **FEATURES**

- 1.8V to 5.5V Input Voltage Range

- 1.2V to 5.5V Output Voltage Range (Fixed and Adjustable)

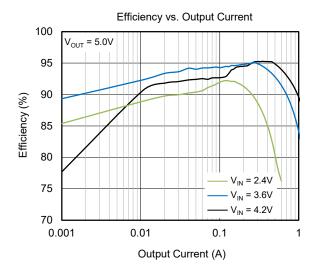

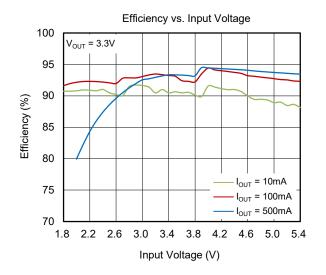

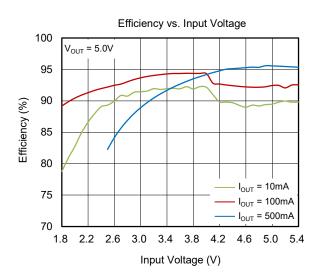

- Up to 96% Efficiency

- Less than 55µA Quiescent Current

- Output Current at 3.3V:

- Up to 1200mA in Buck Mode

- Up to 800mA in Boost Mode (V<sub>IN</sub> > 2.5V)

- Real Buck, Boost and Buck-Boost Modes

- Automatic Mode Transition

- Auto PFM and Forced PWM Selectable

- External Clock Synchronization

- True Shutdown Function with Load Disconnect

- OTP Protection

- Available in a Green TDFN-3×3-10L Package

## **APPLICATIONS**

Medical Equipment System Bias **TEC**

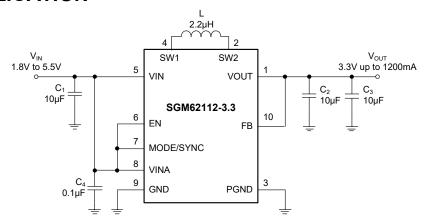

## TYPICAL APPLICATION

Figure 1. Typical Application Circuit of SGM62112-3.3

# PACKAGE/ORDERING INFORMATION

| MODEL        | PACKAGE SPECIFIED TEMPERATURE RANGE |                | ORDERING<br>NUMBER    | PACKAGE<br>MARKING   | PACKING<br>OPTION   |

|--------------|-------------------------------------|----------------|-----------------------|----------------------|---------------------|

| SGM62112-3.3 | TDFN-3×3-10L                        | -40°C to +85°C | SGM62112-3.3YTD10G/TR | SGM<br>G5MD<br>XXXXX | Tape and Reel, 4000 |

| SGM62112-ADJ | TDFN-3×3-10L                        | -40°C to +85°C | SGM62112-ADJYTD10G/TR | SGM<br>SXTD<br>XXXXX | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage on VIN, VINA, SW1, SW2, VOU | T, MODE/SYNC, EN, |

|-------------------------------------|-------------------|

| FB                                  | 0.3V to 6V        |

| Package Thermal Resistance          |                   |

| TDFN-3×3-10L, θ <sub>JA</sub>       | 62°C/W            |

| TDFN-3×3-10L, θ <sub>JB</sub>       | 26°C/W            |

| TDFN-3×3-10L, θ <sub>JC</sub>       | 53°C/W            |

| Junction Temperature                | +150°C            |

| Storage Temperature Range           | 65°C to +150°C    |

| Lead Temperature (Soldering, 10s)   | +260°C            |

| ESD Susceptibility                  |                   |

| HBM                                 | 4000V             |

| CDM                                 | 1000V             |

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage at VIN, VINA          | 1.8V to 5.5V    |

|--------------------------------------|-----------------|

| Operating Junction Temperature Range | -40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

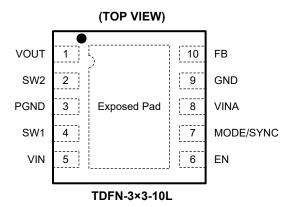

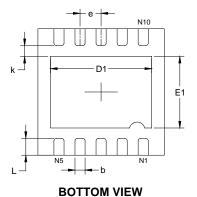

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN            | NAME      | TYPE | FUNCTION                                                                                                                                                                   |

|----------------|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | VOUT      | 0    | Buck-Boost Converter Output Pin.                                                                                                                                           |

| 2              | SW2       | I    | Boost Switch Node Pin.                                                                                                                                                     |

| 3              | PGND      | G    | Power Ground Pin.                                                                                                                                                          |

| 4              | SW1       | I    | Buck Switch Node Pin.                                                                                                                                                      |

| 5              | VIN       | I    | Power Stage Supply Voltage Pin.                                                                                                                                            |

| 6              | EN        | I    | Enable Input Pin. Pulling this pin logic high enables the device, logic low disables the device. Do not leave it floating.                                                 |

| 7              | MODE/SYNC | I    | Mode Selection Pin or External Clock Synchronization Input. Pull this pin logic high for forced PWM operation, logic low for auto PFM operation. Do not leave it floating. |

| 8              | VINA      | I    | Control Stage Supply Voltage Pin.                                                                                                                                          |

| 9              | GND       | G    | Ground Pin.                                                                                                                                                                |

| 10             | FB        | I    | ADJ Version: Voltage Feedback Pin. Fixed Output Voltage Version: connect it to VOUT pin directly.                                                                          |

| Exposed<br>Pad | _         | G    | Exposed Pad. Connect it to GND.                                                                                                                                            |

NOTE: O = output; I = input; G = ground.

# **ELECTRICAL CHARACTERISTICS**

$(T_J = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ typical values are at } T_J = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                                 | SYMBOL                           | CONDITIONS                                                                          | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------|------|------|------|-------|

| DC/DC Stage                               |                                  |                                                                                     |      |      |      |       |

| Input Voltage Range                       | V <sub>IN</sub>                  |                                                                                     | 1.8  |      | 5.5  | V     |

| Input Voltage Range for Startup           | V <sub>IN</sub>                  |                                                                                     | 1.9  |      | 5.5  | V     |

| Output Voltage Range                      | V <sub>OUT</sub>                 | SGM62112-ADJ                                                                        | 1.2  |      | 5.5  | V     |

| Feedback Voltage                          | $V_{FB}$                         | SGM62112-ADJ, MODE/SYNC = V <sub>IN</sub>                                           | 490  | 500  | 510  | mV    |

| Oscillator Frequency                      | f                                |                                                                                     | 1100 | 1400 | 1700 | kHz   |

| Frequency Range for Synchronization       |                                  |                                                                                     | 1250 |      | 1800 | kHz   |

| Switch Current Limit                      | I <sub>SW</sub>                  | V <sub>IN</sub> = V <sub>INA</sub> = 5V, T <sub>J</sub> = +25°C                     |      | 2400 |      | mA    |

| High side Cuiteb On Desistance            | R <sub>Q1</sub>                  | V - V - 5V                                                                          |      | 85   |      | mΩ    |

| High-side Switch On-Resistance            | R <sub>Q4</sub>                  | $-V_{IN} = V_{INA} = 5V$                                                            |      | 95   |      |       |

| Law aida Coitab On Basistanas             | R <sub>Q2</sub>                  | V - V - 5V                                                                          |      | 60   |      |       |

| Low-side Switch On-Resistance             | $R_{Q3}$ $V_{IN} = V_{INA} = 5V$ |                                                                                     |      | 55   |      | mΩ    |

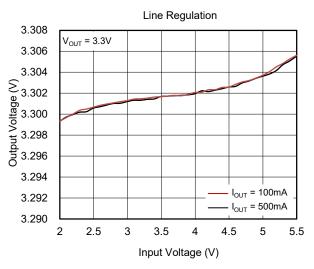

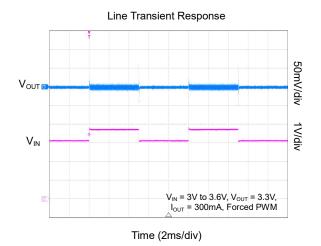

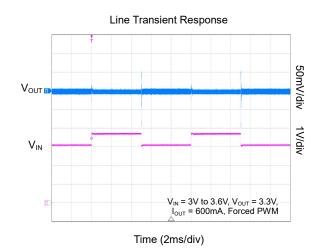

| Line Regulation                           |                                  | Forced PWM Mode                                                                     |      |      | 0.5  | %     |

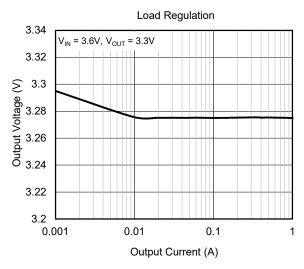

| Load Regulation                           |                                  |                                                                                     |      |      | 1    | %     |

| Quiescent Current                         | 1                                | I <sub>OUT</sub> = 0mA, V <sub>EN</sub> = V <sub>IN</sub> = V <sub>INA</sub> = 3.6V |      | 35   | 55   | μА    |

| Quiescent Current                         | lα                               | V <sub>OUT</sub> = 3.6V                                                             |      | 4    | 7    |       |

| FB Input Impedance (Fixed Output Voltage) |                                  |                                                                                     |      | 1    |      | МΩ    |

| Shutdown Current                          | Is                               | $V_{EN} = 0V, V_{IN} = V_{INA} = 3.6V$                                              |      | 0.1  | 1    | μA    |

| Control Stage                             |                                  |                                                                                     |      |      |      | _     |

| Under-Voltage Lockout Threshold           | V <sub>UVLO</sub>                | V <sub>IN</sub> voltage decreasing                                                  | 1.6  | 1.7  | 1.8  | V     |

| EN, MODE/SYNC Input Low Voltage           | V <sub>IL</sub>                  |                                                                                     |      |      | 0.4  | V     |

| EN, MODE/SYNC Input High Voltage          | V <sub>IH</sub>                  |                                                                                     | 1.2  |      |      | V     |

| EN, MODE/SYNC Input Current               |                                  | Clamped on GND or VINA                                                              |      | 0.1  | 0.5  | μA    |

| Over-Temperature Protection               |                                  |                                                                                     |      | 140  |      | °C    |

| Over-Temperature Hysteresis               |                                  |                                                                                     |      | 20   |      | °C    |

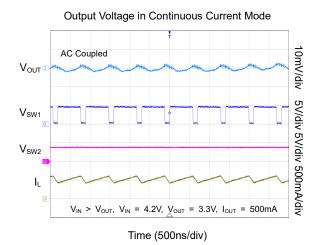

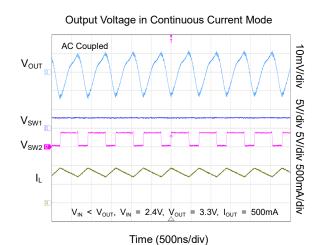

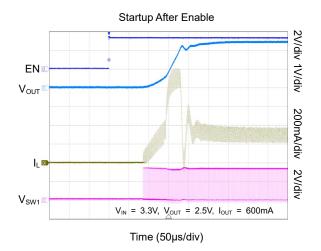

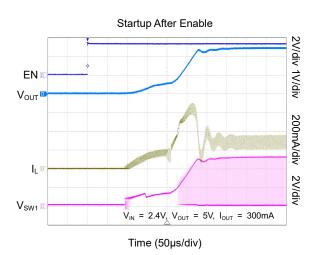

# TYPICAL PERFORMANCE CHARACTERISTICS

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_J$  = +25°C, unless otherwise noted.

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_J$  = +25°C, unless otherwise noted.

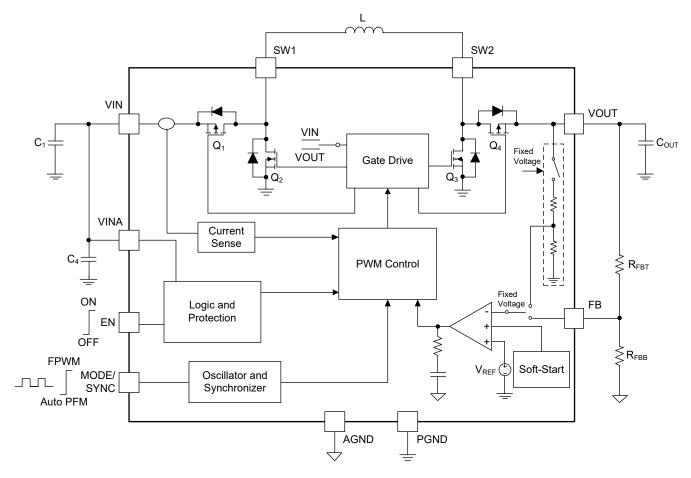

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

# **DETAILED DESCRIPTION**

The SGM62112 contains 4 MOSFETs for synchronous operation to improve system efficiency. In EN logic low case, the Buck-leg high-side MOSFET enables a load disconnect function.

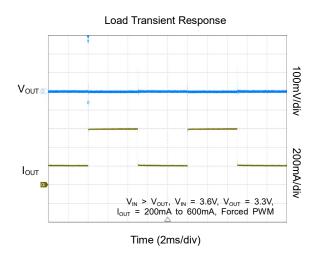

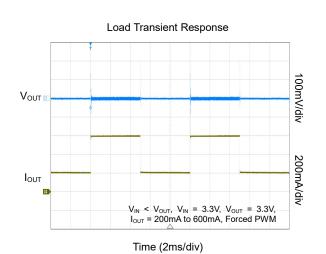

The SGM62112 senses the inductor current through the Buck-leg high-side MOSFET which is controlled by a current loop. The voltage loop formed by the feedback network then controls the current loop to regulate the output voltage. The SGM62112 implements input and output voltage feedforward and monitors the input and output voltage, any changes are immediately responded to achieve fast load transient response. The output voltage of SGM62112 is programmed via a resistive voltage divider connected at FB pin. Loop compensation network is integrated to reduce external component count.

The SGM62112 senses the peak inductor current for PWM duty cycle generation. In addition, the peak input current is also sensed to limit the maximal input power consumed by the load. This additional feature works in conjunction with the maximal peak inductor current to provide safe and stable operation of SGM62112. Some protection features are also implemented such as the thermal shutdown.

#### **Device Enable**

Pulling the EN pin logic high starts up the SGM62112, while a logic low turns off the device. During startup, the SGM62112 limits the peak current to control the inrush current being pulled from the input supply.

#### **Under-Voltage Lockout (UVLO)**

The SGM62112 separates the power stage input and the internal power supply input of the device via VIN and VINA pins. An under-voltage lockout function is implemented to prevent insufficient voltage applied on VINA pin. Voltage below the UVLO threshold will turn off the SGM62112.

#### **Soft-Start and Short Circuit Protection**

The SGM62112 starts switching once the device is enabled and voltage at VINA pin exceeds the UVLO threshold. The current limit is set to 400mA to raise the output voltage from 0V. Current limit is released to the nominal value once the voltage is higher than 1.2V. If the output voltage fails to reach 1.2V or lower, it indicates that a short circuit condition is present. Current limit is reduced in the short circuit condition to prevent the device from damage. The reduced current limit prevents output voltage overshoot and large inrush current at startup.

# **Over-Temperature Protection**

The SGM62112 implements the over-temperature protection which prevents the device from over-heating. If the sensed temperature in the IC exceeds the thermal shutdown threshold (see Electrical Characteristics), the device terminates the operation. The device resumes operating once the junction temperature falls 20 °C below the thermal shutdown threshold.

## **Buck-Boost Operation**

The SGM62112 is a fully-integrated synchronous Buck-Boost converter which can automatically switch to boost, buck or buck-boost operation to ensure regulated output throughout entire input range. In all operation modes, the SGM62112 switches with one main switch FET, one rectifying switch, while one of the either high-side MOSFET remains fully turn-on, and the last switch remains fully off.

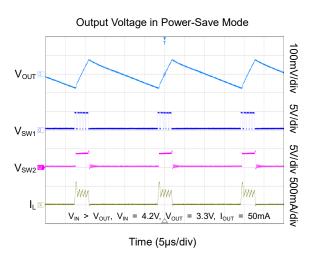

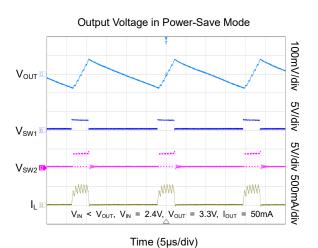

#### **Power-Save Mode and Synchronization**

The SGM62112 allows programmable PFM operation or forced PWM operation at light loads via MODE/SYNC pin. Power-save mode is used to improve efficiency at light loads. The SGM62112 also supports external frequency synchronization function. An external clock signal applied at MODE/SYNC pin forces the device to synchronize to the applied clock frequency. The internal phase-locked loop (PLL) ensures smooth operation when a lack of synchronous clock pulse does not cause malfunction.

# **APPLICATION INFORMATION**

The SGM62112 DC/DC converter supports various popular battery chemistries in the 1.8V to 5.5V range. The fully-integrated power-stage MOSFETs reduce solution size as well as achieving high efficiency.

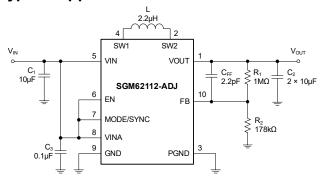

#### **Typical Application**

Figure 3. Typical Application Circuit of SGM62112-ADJ

#### **Design Requirements**

The loop compensation of the SGM62112-ADJ Buck-Boost converter is integrated to reduce external component counts. The external LC filter combination should be carefully designed to ensure control loop stability. Please follow Table 1 for the recommended component selections.

**Table 1. List of Components**

|                                 | -                                                           |               |

|---------------------------------|-------------------------------------------------------------|---------------|

| Reference                       | Description                                                 | Vendor        |

| L <sub>1</sub>                  | 2.2µH,1.8A, 74438334022                                     | Wurth         |

| C <sub>1</sub>                  | 10μF, 6.3V, 0603, X7R ceramic                               |               |

| C <sub>2</sub>                  | 2 × 10µF, 6.3V, 0603, X7R ceramic                           |               |

| C <sub>3</sub>                  | 0.1μF, X7R ceramic                                          |               |

| R <sub>1</sub> , R <sub>2</sub> | Depending on the output voltage of not used on SGM62112-3.3 | SGM62112-ADJ, |

#### **Programming the Output Voltage**

To program the output voltage, an external resistor divider is used to adjust the output voltage. The current through the resistive divider should be about 100 times greater than the current into the FB pin to avoid the effect on the output voltage accuracy since there is 0.01 $\mu$ A (TYP) leakage current into the FB pin. In order ensure the 100 times condition, the recommended value for R<sub>2</sub> should be lower than 500k $\Omega$  to set the

divider current at  $1\mu A$  or higher. Depending on the needed output voltage ( $V_{OUT}$ ), the resistor,  $R_1$ , connected between VOUT and FB pin can be calculated using equation 1.

$$R_1 = R_2 \times \left(\frac{V_{\text{OUT}}}{V_{\text{FB}}} - 1\right) \tag{1}$$

A  $1M\Omega$  resistor is chosen for  $R_1$  to program 3.3V output. To further improve the loop response of the device, a feed-forward capacitor in parallel to  $R_1$  is recommended. Please follow equation 2 for feed-forward capacitor calculation.

$$C_{FF} = \frac{2.2\mu s}{R_1} \tag{2}$$

#### **Inductor Selection**

The inductor used on DC/DC performs important roles to ensure proper operation of the device. Table 2 listed readily available inductor series from various vendors.

Table 2. List of Recommended Inductors

| Vendor     | Inductor Series |  |  |

|------------|-----------------|--|--|

| Wurth      | 74438334022     |  |  |

| vvurin     | 74438324022     |  |  |

| Murata     | LQH3NP          |  |  |

| Tajo Yuden | NR3015          |  |  |

| TDK        | VLF3215         |  |  |

| TDK        | VLF4012         |  |  |

A low DC resistance inductor is recommended to minimize conduction losses. And the core loss of the inductor also affects the efficiency. Large inductance results in large ripple current which reduces core loss, but provides better load transient response versus small inductance. Saturation current of the inductor should be taken into account as well. Equation 4 shows the calculation of inductor peak current. The saturation current of the selected inductor should be higher than the value calculated in equation 4. Boost mode or lowest operation input has the highest value of current; therefore only Boost mode equation is displayed.

# **APPLICATION INFORMATION (continued)**

Duty Cycle Boost

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}}$$

(3)

$$I_{PEAK} = \frac{I_{OUT}}{\eta \times (1 - D)} + \frac{V_{IN} \times D}{2 \times f \times L}$$

(4)

where:

D: Boost mode duty cycle.

L: Inductance.

F: Converter switching frequency, 1.4MHz (TYP).

η: DC/DC conversion efficiency (90% efficiency estimation is a good starting point).

The saturation current of the selected inductor should be at least 20% higher than the value calculated using equation 4 to ensure enough margin. Table 2 lists some recommended inductors for SGM62112.

# **Capacitor Selection**

**Input Capacitor**

A 4.7 $\mu F$  or higher value ceramic capacitor should be placed as close as possible to the IC's VIN and PGND pins.

#### **Output Capacitor**

A minimal of  $15\mu F$  effective capacitance ceramic capacitor placed as close as possible to the VOUT and PGND pins of the IC is recommended.

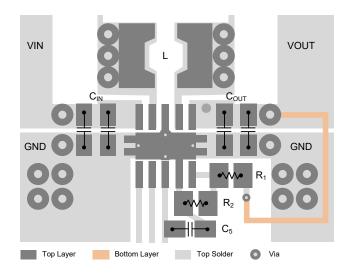

#### **Layout Guidelines**

Layout plays a significant role for all switch mode DC/DC power supplies. Improper layout could result in poor EMI performance, device instability, and potential device damage. The input and output capacitors should be placed on the same PCB layer as the IC. In addition, the loop formed by the capacitor input/output return to IC ground pin should be as small as possible. The SGM62112 implements a power ground and control ground pins to minimize the ground noise effect on sensitive analog circuits. Use a separate ground trace to connect the feedback, and connect this ground trace to the main power ground at a single point.

Figure 4. Layout Recommendation

#### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| SEPTEMBER 2023 – REV.A.1 to REV.A.2                 | Page |

|-----------------------------------------------------|------|

| Changed Features section                            | 1    |

| Changed Absolute Maximum Ratings section            | 2    |

|                                                     |      |

| AUGUST 2022 – REV.A to REV.A.1                      | Page |

| Updated Typical Performance Characteristics section | 8    |

| Changes from Original (MARCH 2022) to REV.A         | Page |

| Changed from product preview to production data     | All  |

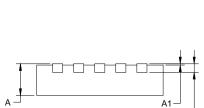

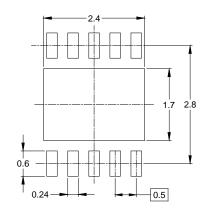

# **PACKAGE OUTLINE DIMENSIONS TDFN-3×3-10L**

**TOP VIEW**

**SIDE VIEW**

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol |         | nsions<br>meters | Dimensions<br>In Inches |       |  |

|--------|---------|------------------|-------------------------|-------|--|

|        | MIN MAX |                  | MIN                     | MAX   |  |

| А      | 0.700   | 0.800            | 0.028                   | 0.031 |  |

| A1     | 0.000   | 0.050            | 0.000                   | 0.002 |  |

| A2     | 0.203   | REF              | 0.008 REF               |       |  |

| D      | 2.900   | 3.100            | 0.114                   | 0.122 |  |

| D1     | 2.300   | 2.600            | 0.091                   | 0.103 |  |

| Е      | 2.900   | 3.100            | 0.114                   | 0.122 |  |

| E1     | 1.500   | 1.800            | 0.059                   | 0.071 |  |

| k      | 0.200   | MIN              | 0.008                   | MIN   |  |

| b      | 0.180   | 0.300            | 0.007                   | 0.012 |  |

| е      | 0.500   | 0.500 TYP        |                         | TYP   |  |

| L      | 0.300   | 0.500            | 0.012                   | 0.020 |  |

NOTE: This drawing is subject to change without notice.

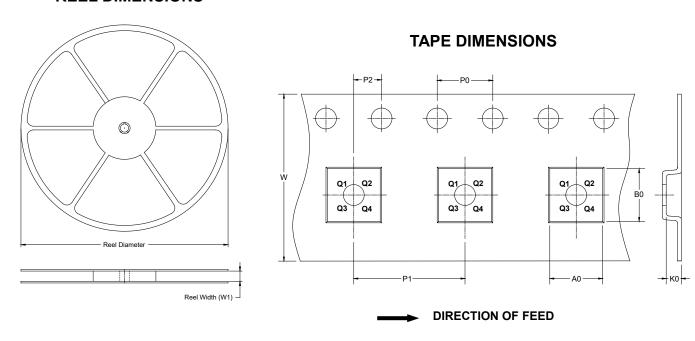

# TAPE AND REEL INFORMATION

## **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TDFN-3×3-10L | 13"              | 12.4                     | 3.35       | 3.35       | 1.13       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

# **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

# **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-----------|----------------|---------------|----------------|--------------|

| 13"       | 386            | 280           | 370            | 5            |