# 2.4V to 5.5V Input, 4A/6A Synchronous Buck Converter with I<sup>2</sup>C Interface

#### GENERAL DESCRIPTION

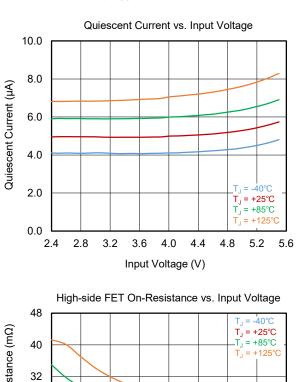

The SGM6038 is a family of high power density synchronous Buck converters which are capable of delivering 4A/6A continuous output current from 2.4V to 5.5V input voltage range. The device only consumes 5µA (TYP) quiescent current.

The SGM6038 implements an I<sup>2</sup>C interface to further enhance the device's flexibility and ease of use to adapt for various application needs. The device implements auto PFM mode operation to maximize the efficiency at light load condition. At moderate to heavy load, the device automatically switches to CCM operation with a 2.3MHz (TYP) switching frequency. forced PWM operation is also available via I<sup>2</sup>C programming for low output voltage ripple requirement.

The SGM6038 implements the constant on-time (COT) architecture that incorporates the benefits of fast load and line transient responses and low output voltage ripple, which is beneficial for RF and noise sensitive applications.

The SGM6038 family of devices offers VID option for dynamic voltage scaling (DVS) via the I<sup>2</sup>C interface, which can adjust the output voltage rapidly to adapt for any changes on the load side. Another variant of the device offers an active-low power good (VSET/nPG) function.

The SGM6038 is available in a Green TQFN-1.5×2.5 -9L package.

#### **APPLICATIONS**

Core Supply for FPGAs, CPUs, ASICs or GPUs DDR Memory Optical Modules Solid-State Drives

#### **FEATURES**

- 2.4V to 5.5V Input Voltage Range

- 5µA (TYP) Quiescent Current

- 2.3MHz (TYP) Switching Frequency

- 2% Output Voltage Accuracy

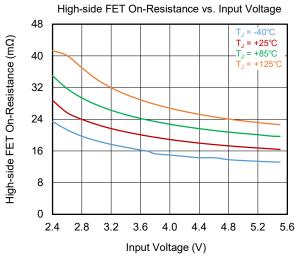

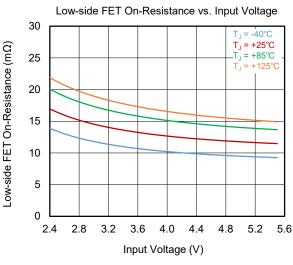

- 16.4mΩ and 10.5mΩ Internal Power MOSFETs

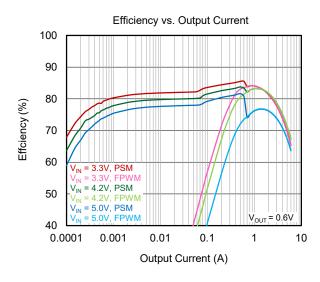

- 90% Efficiency at 0.9V Output

- COT-Control Architecture for Fast Transient Response

- Output Current:

- SGM6038A: 4A (VSET/VID Pin)

- SGM6038B: 4A (VSET/nPG Pin)

- SGM6038C: 6A (VSET/VID Pin)

- SGM6038D: 6A (VSET/nPG Pin)

- Selection by External Resistor

- I<sup>2</sup>C Slave Address

- Start-up Output Voltage

- Selection by I<sup>2</sup>C Interface

- Output Discharge

- Output Voltage Ramp Speed

- Power-Save Mode or Forced PWM Mode

- Hiccup or Latching Short-Circuit Protection

- VID Option for Dynamic Voltage Scaling (DVS)

- Thermal Warning and Shutdown

- Power Good Indicator Pin Option

- Up to 3.4Mbps I<sup>2</sup>C Compatible Interface

- Available in a Green TQFN-1.5×2.5-9L Package

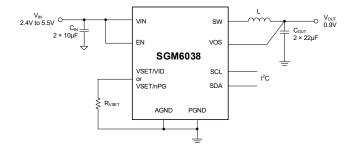

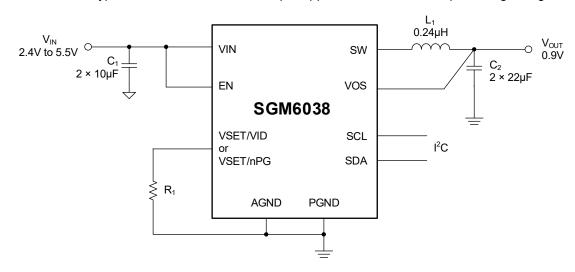

#### TYPICAL APPLICATION

**Figure 1. Typical Application Circuit**

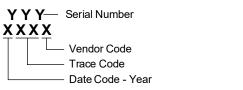

## PACKAGE/ORDERING INFORMATION

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM6038A | TQFN-1.5×2.5-9L        | -40°C to +125°C                   | SGM6038AXTVY9G/TR  | 1VQ<br>XXXX        | Tape and Reel, 3000 |

| SGM6038B | TQFN-1.5×2.5-9L        | -40°C to +125°C                   | SGM6038BXTVY9G/TR  | 1VR<br>XXXX        | Tape and Reel, 3000 |

| SGM6038C | TQFN-1.5×2.5-9L        | -40°C to +125°C                   | SGM6038CXTVY9G/TR  | 1GC<br>XXXX        | Tape and Reel, 3000 |

| SGM6038D | TQFN-1.5×2.5-9L        | -40°C to +125°C                   | SGM6038DXTVY9G/TR  | 1GD<br>XXXX        | Tape and Reel, 3000 |

#### MARKING INFORMATION

NOTE: XXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

## **DEVICE DESCRIPTION**

| Part Number | Start-up Output Voltage     | Output Current | VSET/VID or VSET/nPG Pin |

|-------------|-----------------------------|----------------|--------------------------|

| SGM6038A    |                             | 4.0            | VSET/VID                 |

| SGM6038B    |                             | 4A             | VSET/nPG                 |

| SGM6038C    | - 0.4V to 1.15V, Selectable | 6.4            | VSET/VID                 |

| SGM6038D    |                             | 6A             | VSET/nPG                 |

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>IN</sub> 0.3V to 6V                   |

|--------------------------------------------------------------|

| EN, SDA, SCL, VOS Voltages0.3V to 6V                         |

| VSET/VID, VSET/nPG Voltages0.3V to 6V                        |

| SW, DC Voltages0.3V to V <sub>IN</sub> + 0.3V                |

| SW, AC (10ns Transient), while Switching2.5V to 10V          |

| Source Current at VSET/nPG, I <sub>SOURCE_VSET/nPG</sub> 1mA |

| Sink Current at SDA, SCL, I <sub>SINK_SDA/SCL</sub> 2mA      |

| Package Thermal Resistance                                   |

| TQFN-1.5×2.5-9L, θ <sub>JA</sub> 75.5°C/W                    |

| TQFN-1.5×2.5-9L, θ <sub>JB</sub>                             |

| TQFN-1.5×2.5-9L, θ <sub>JC</sub> 57.2°C/W                    |

| Operating Junction Temperature40°C to +150°C                 |

| Storage Temperature Range65°C to +150°C                      |

| Lead Temperature (Soldering, 10s)+260°C                      |

| ESD Susceptibility (1)(2)                                    |

| HBM±2000V                                                    |

| CDM±1000V                                                    |

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage, V <sub>IN</sub>                            | 2.4V to 5.5V  |

|------------------------------------------------------------|---------------|

| Falling Transition Time at VIN Pin, t <sub>VIN_F</sub> (3) | 10mV/µs       |

| SGM6038A/B: Output Current, I <sub>OUT</sub> (4)           | 0A to 4A      |

| SGM6038C/D: Output Current, I <sub>OUT</sub> (5)           | 0A to 6A      |

| Operating Junction Temperature Range40                     | 0°C to +125°C |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

- 3. The falling slew rate of  $V_{\text{IN}}$  should be limited if  $V_{\text{IN}}$  goes below  $V_{\text{UVLO}}.$

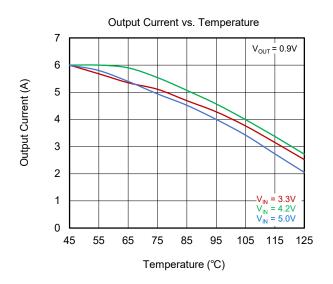

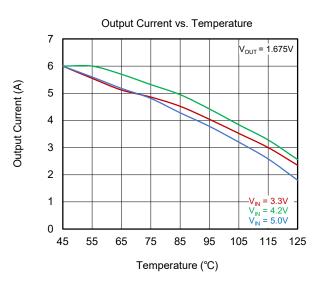

- 4. Lifetime is reduced when operating continuously at 4A output current and the junction temperature is higher than  $\pm 105 ^{\circ}\text{C}$ .

- 5. Lifetime is reduced when operating continuously at 6A output current and the junction temperature is higher than  $+85^{\circ}\text{C}$ .

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

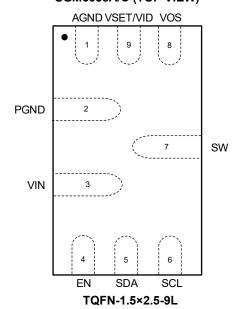

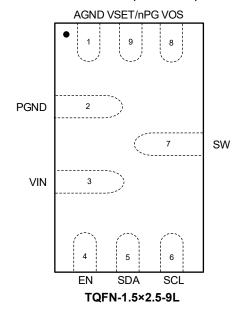

## **PIN CONFIGURATIONS**

#### SGM6038A/C (TOP VIEW)

#### SGM6038B/D (TOP VIEW)

## **PIN DESCRIPTION**

| PIN | NAME     | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                   |

|-----|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | AGND     | G    | Analog Ground Pin.                                                                                                                                                                                                                                                                                         |

| 2   | PGND     | G    | Power Ground Pin.                                                                                                                                                                                                                                                                                          |

| 3   | VIN      | Р    | Power Supply Input. Connect a ceramic capacitor (C <sub>IN</sub> ) close to this pin and PGND.                                                                                                                                                                                                             |

| 4   | EN       | I    | Device Enable Pin. Logic high on this pin enables the device, and logic low on this pin disables the device. Do not leave it floating.                                                                                                                                                                     |

| 5   | SDA      | I/O  | I <sup>2</sup> C Bus Data Signal. Do not leave it floating. Connect it to AGND if not used.                                                                                                                                                                                                                |

| 6   | SCL      | ı    | I <sup>2</sup> C Bus Clock Signal. Do not leave it floating. Connect it to AGND if not used.                                                                                                                                                                                                               |

| 7   | SW       | Р    | Switching Node Pin. This pin is connected to the internal MOSFET switches. Connect the inductor to this terminal.                                                                                                                                                                                          |

| 8   | VOS      | Р    | Output Voltage Sense Input. This pin is internally connected to the feedback loop and a MOSFET to discharge the output $(V_{OUT})$ when the device is disabled. Connect it with a short trace to the output capacitor.                                                                                     |

| 9   | VSET/VID | I/O  | I <sup>2</sup> C Address Selection and Start-up Voltage Selection Pin. An external resistor connected to this pin programs the start-up voltage. Logic low selects the VOUT register 1 ( <b>REG0x01</b> ), and logic high selects the VOUT register 2 ( <b>REG0x02</b> ).                                  |

| 9   | VSET/nPG | I/O  | I <sup>2</sup> C Address Selection and Start-up Voltage Selection Pin. An external resistor connected to this pin programs the start-up voltage. After start-up, this pin is an active-low power good pin. When output voltage is within regulation, this pin is pulled low through the external resistor. |

NOTE: I = input, O = output, I/O = input/output, P = power, G = ground.

## **ELECTRICAL CHARACTERISTICS**

$(T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, V_{IN} = 2.4\text{V to } 5.5\text{V}, \text{ all typical values are measured at } T_J = +25^{\circ}\text{C} \text{ and } V_{IN} = 3.7\text{V}, \text{ unless otherwise noted.})$

| PARAMETER SYMBOL CONDITIONS                                  |                            |                                                                                   |      | TYP  | MAX  | UNITS    |  |  |  |

|--------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------|------|------|------|----------|--|--|--|

| Supply                                                       |                            |                                                                                   |      |      |      |          |  |  |  |

| Quiescent Current                                            | ΙQ                         | EN = High, no load, device not switching                                          |      | 5    | 17.0 | μA       |  |  |  |

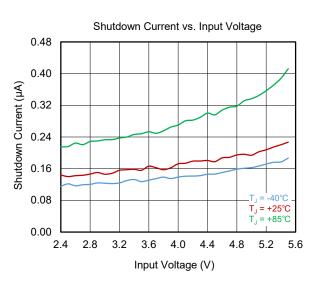

| Shutdown Current                                             | I <sub>SD</sub>            | $T_J = -40$ °C to +85°C, EN = low                                                 |      | 0.1  | 1.7  | μA       |  |  |  |

| Hadan Valtaria Laglicus Thuashald                            | M                          | V <sub>IN</sub> rising                                                            | 2.0  | 2.2  | 2.4  | l V      |  |  |  |

| Under-Voltage Lockout Threshold                              | $V_{\text{UVLO}}$          | V <sub>IN</sub> falling                                                           | 1.9  | 2.1  | 2.3  | v        |  |  |  |

| Thermal Warning Threshold                                    | т                          | $T_J$ rising                                                                      |      | 130  |      | °C       |  |  |  |

| Thermal Warning Hysteresis                                   | $T_JW$                     | T <sub>J</sub> falling                                                            |      | 20   |      | °C       |  |  |  |

| Thermal Shutdown Threshold                                   | -                          | T <sub>J</sub> rising                                                             |      | 150  |      | °C       |  |  |  |

| Thermal Shutdown Hysteresis                                  | $T_{SD}$                   | T <sub>J</sub> falling                                                            |      | 20   |      | °C       |  |  |  |

| Logic Interface EN, SCL, SDA, VSET                           | /VID                       |                                                                                   |      |      |      |          |  |  |  |

| High-Level Input Threshold Voltage at EN, SCL, SDA, VSET/VID | V <sub>IH</sub>            |                                                                                   | 0.9  |      |      | V        |  |  |  |

| Low-Level Input Threshold Voltage at EN, SCL, SDA, VSET/VID  | $V_{IL}$                   |                                                                                   |      |      | 0.3  | ٧        |  |  |  |

| Input Leakage Current into SCL Pin                           | I <sub>SCL_LKG</sub>       |                                                                                   |      | 0.01 | 0.30 | μA       |  |  |  |

| Input Leakage Current into SDA Pin                           | I <sub>SDA_LKG</sub>       |                                                                                   |      | 0.01 | 0.30 | μA       |  |  |  |

| Input Leakage Current into EN Pin                            | I <sub>EN_LKG</sub>        |                                                                                   |      | 0.03 | 0.30 | μΑ       |  |  |  |

| Parasitic Capacitance at SCL                                 | $C_{SCL}$                  |                                                                                   |      | 1    |      | pF       |  |  |  |

| Parasitic Capacitance at SDA                                 | $C_{SDA}$                  |                                                                                   |      | 2    |      | pF       |  |  |  |

| Start-up, Power Good                                         |                            |                                                                                   |      |      |      |          |  |  |  |

| Enable Delay Time                                            | t <sub>DELAY</sub>         | Time from EN high to device starts switching, $R_1$ = 249k $\Omega$               | 340  | 640  | 950  | μs       |  |  |  |

| Output Voltage Ramp Time                                     | t <sub>RAMP</sub>          | Time from device starts switching to power good                                   | 0.65 | 1.3  | 1.8  | ms       |  |  |  |

| Power Good Lower Threshold                                   | $V_{VSET/nPG}$             | V <sub>VOS</sub> referenced to V <sub>OUT</sub> nominal                           | 85   | 91   | 97   | %        |  |  |  |

| Power Good Upper Threshold                                   | ▼ VSET/nPG                 | V <sub>VOS</sub> referenced to V <sub>OUT</sub> nominal                           | 105  | 111  | 118  | %        |  |  |  |

| Power Good Deglitch Delay                                    | $t_{\text{VSET/nPG\_DLY}}$ | Rising and falling edges                                                          |      | 48   |      | μs       |  |  |  |

| Output                                                       |                            |                                                                                   |      |      |      |          |  |  |  |

|                                                              |                            | $T_J$ = -40°C to +125°C,<br>$V_{OUT} \ge 1.15V$ , FPWM, no Load                   | -2.0 |      | 2.0  |          |  |  |  |

| Output Voltage Accuracy                                      | $V_out$                    | $T_J$ = -40°C to +125°C,<br>0.9V $\leq$ V <sub>OUT</sub> $<$ 1.15V, FPWM, no Load | -2.3 |      | 2.3  | %        |  |  |  |

| Output Voltage Accuracy                                      | <b>V</b> 001               | $T_J$ = -40°C to +125°C,<br>0.59V ≤ V <sub>OUT</sub> < 0.9V, FPWM, no Load        | -3.4 |      | 3.4  | - %<br>- |  |  |  |

|                                                              |                            | $T_J$ = -40°C to +125°C,<br>$V_{OUT}$ < 0.59V, FPWM, no Load                      | -4.9 |      | 4.9  |          |  |  |  |

|                                                              |                            | EN = high, V <sub>VOS</sub> = 1.8V                                                |      | 1    |      |          |  |  |  |

| Input Leakage Current into VOS Pin                           | I <sub>VOS_LKG</sub>       | EN = low, output discharge disabled,<br>$V_{VOS} = 1.8V$                          |      | 0.1  | 0.5  | μA       |  |  |  |

| Output Discharge Resistor at VOS Pin                         | R <sub>DIS</sub>           |                                                                                   |      | 17   | 25   | Ω        |  |  |  |

| Load Regulation                                              |                            | V <sub>OUT</sub> = 0.9V, FPWM                                                     |      | 0.18 |      | %/A      |  |  |  |

**ELECTRICAL CHARACTERISTICS (continued)** ( $T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ,  $V_{IN} = 2.4\text{V}$  to 5.5V, all typical values are measured at  $T_J = +25^{\circ}\text{C}$  and  $V_{IN} = 3.7\text{V}$ , unless otherwise noted.)

| PARAMETER                           | SYMBOL            | CONDITIONS                                | MIN | TYP  | MAX  | UNITS |  |

|-------------------------------------|-------------------|-------------------------------------------|-----|------|------|-------|--|

| Power Switch                        |                   |                                           |     |      |      |       |  |

| High-side FET On-Resistance         | В                 |                                           |     | 16.4 |      | mΩ    |  |

| Low-side FET On-Resistance          | R <sub>DSON</sub> |                                           |     | 10.5 |      | mΩ    |  |

| High-side FET Forward Current Limit |                   | SGM6038A and SGM6038B                     | 5.4 | 6.8  | 8.0  | A     |  |

| (Initialization)                    |                   | SGM6038C and SGM6038D                     | 6.7 | 8.5  | 10.0 |       |  |

| Low-side FET Forward Current Limit  | I <sub>LIM</sub>  | SGM6038A and SGM6038B                     |     | 5.6  |      |       |  |

| Low-side FET Forward Current Limit  |                   | SGM6038C and SGM6038D                     | 7.0 |      |      | Α     |  |

| Low-side FET Negative Current Limit |                   | SGM6038A, SGM6038B, SGM6038C and SGM6038D |     | -2.4 |      | Α     |  |

| PWM Switching Frequency             | f <sub>SW</sub>   | $I_{OUT} = 1A, V_{OUT} = 0.9V$            |     | 2.3  |      | MHz   |  |

## I<sup>2</sup>C INTERFACE TIMING CHARACTERISTICS

| PARAMETER                                                                          | SYMBOL                             | CONDITIONS                                                      | MIN                                                                                 | TYP | MAX  | UNITS |

|------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|------|-------|

|                                                                                    |                                    | Standard mode                                                   |                                                                                     |     | 100  | kHz   |

|                                                                                    |                                    | Fast mode                                                       |                                                                                     |     | 400  | kHz   |

|                                                                                    |                                    | Fast mode plus                                                  |                                                                                     |     | 1    | MHz   |

| SCL Clock Frequency                                                                | $f_{SCL}$                          | High-speed mode (write operation), C <sub>B</sub> - 100pF (MAX) |                                                                                     |     | 3.4  | MHz   |

|                                                                                    |                                    | High-speed mode (read operation), C <sub>B</sub> - 10pF (MAX)   |                                                                                     |     | 3.4  | MHz   |

|                                                                                    |                                    | High-speed mode (write operation), C <sub>B</sub> - 400pF (MAX) |                                                                                     |     | 1.7  | MHz   |

|                                                                                    |                                    | High-speed mode (read operation), C <sub>B</sub> - 400pF (MAX)  |                                                                                     |     | 1.7  | MHz   |

|                                                                                    |                                    | Standard mode                                                   | 4.7                                                                                 |     |      | μs    |

| Bus Free Time between a Stop and Start Condition                                   | t <sub>BUF</sub>                   | Fast mode                                                       | 1.3                                                                                 |     |      | μs    |

| and Start Condition                                                                |                                    | Fast mode plus                                                  | 0.5                                                                                 |     |      | μs    |

|                                                                                    |                                    | Standard mode                                                   | 4                                                                                   |     |      | μs    |

| Hold Time (Repeated) Start                                                         |                                    | Fast mode                                                       | 600                                                                                 |     |      | ns    |

| Condition                                                                          | t <sub>HD</sub> , t <sub>STA</sub> | Fast mode plus                                                  | 260                                                                                 |     |      | ns    |

|                                                                                    |                                    | High-speed mode                                                 | 160                                                                                 |     |      | ns    |

|                                                                                    |                                    | Standard mode                                                   | 4.7                                                                                 |     |      | μs    |

|                                                                                    | t <sub>LOW</sub>                   | Fast mode                                                       | 1.3                                                                                 |     |      | μs    |

| Low Period of the SCL Clock                                                        |                                    | Fast mode plus                                                  | 0.5                                                                                 |     |      | μs    |

| Low Period of the SCL Clock                                                        |                                    | High-speed mode, C <sub>B</sub> - 100pF (MAX)                   | 160                                                                                 |     |      | ns    |

|                                                                                    |                                    | High-speed mode, C <sub>B</sub> - 400pF (MAX)                   | 320                                                                                 |     |      | ns    |

|                                                                                    |                                    | Standard mode                                                   | 4                                                                                   |     |      | μs    |

|                                                                                    |                                    | Fast mode                                                       | 600                                                                                 |     |      | ns    |

| Low Period of the SCL Clock High Period of the SCL Clock Setup Time for a Repeated | t <sub>HIGH</sub>                  | Fast mode plus                                                  | 260                                                                                 |     |      | ns    |

|                                                                                    |                                    | High-speed mode, C <sub>B</sub> - 100pF (MAX)                   | 60                                                                                  |     |      | ns    |

|                                                                                    |                                    | High-speed mode, C <sub>B</sub> - 400pF (MAX)                   | 120                                                                                 |     |      | ns    |

|                                                                                    |                                    | Standard mode                                                   | 4.7                                                                                 |     |      | μs    |

| Setup Time for a Repeated                                                          |                                    | Fast mode                                                       | 600                                                                                 |     |      | ns    |

| Start Condition                                                                    | t <sub>su</sub> , t <sub>sta</sub> | Fast mode plus                                                  | 260                                                                                 |     |      | ns    |

|                                                                                    |                                    | High-speed mode                                                 | 160                                                                                 |     |      | ns    |

|                                                                                    |                                    | Standard mode                                                   | 250                                                                                 |     |      | ns    |

|                                                                                    |                                    | Fast mode                                                       | 100                                                                                 |     |      | ns    |

| Data Setup Time                                                                    | $t_{SU}, t_{DAT}$                  | Fast mode plus                                                  | 50                                                                                  |     |      | ns    |

|                                                                                    |                                    | High-speed mode                                                 | 320<br>4<br>600<br>260<br>60<br>120<br>4.7<br>600<br>260<br>160<br>250<br>100<br>50 | ns  |      |       |

|                                                                                    |                                    | Standard mode                                                   | 0                                                                                   |     | 3.45 | μs    |

|                                                                                    |                                    | Fast mode                                                       | 0                                                                                   |     | 0.9  | μs    |

| Data Hold Time                                                                     | t <sub>HD</sub> , t <sub>DAT</sub> | Fast mode plus                                                  | 0                                                                                   |     |      | μs    |

|                                                                                    |                                    | High-speed mode, C <sub>B</sub> - 100pF (MAX)                   | 0                                                                                   |     | 70   | ns    |

|                                                                                    |                                    | High-speed mode, C <sub>B</sub> - 400pF (MAX)                   | 0                                                                                   |     | 150  | ns    |

## **SGM6038**

## I<sup>2</sup>C INTERFACE TIMING CHARACTERISTICS (continued)

| PARAMETER                                        | SYMBOL                             | CONDITIONS                                    | MIN                     | TYP | MAX                                                                                                                        | UNITS |

|--------------------------------------------------|------------------------------------|-----------------------------------------------|-------------------------|-----|----------------------------------------------------------------------------------------------------------------------------|-------|

|                                                  |                                    | Standard mode                                 |                         |     | 1000                                                                                                                       | ns    |

|                                                  |                                    | Fast mode                                     | 20 + 0.1 C <sub>B</sub> |     | 300                                                                                                                        | ns    |

| Rise Time of SCL Signal                          | t <sub>RCL</sub>                   | Fast mode plus                                |                         |     | 120                                                                                                                        | ns    |

|                                                  |                                    | High-speed mode, C <sub>B</sub> - 100pF (MAX) | 10                      |     | 40                                                                                                                         | ns    |

|                                                  |                                    | High-speed mode, C <sub>B</sub> - 400pF (MAX) | 20                      |     | 80                                                                                                                         | ns    |

|                                                  |                                    | Standard mode                                 | 20 + 0.1 C <sub>B</sub> |     | 1000                                                                                                                       | ns    |

| Rise Time of SCL Signal                          |                                    | Fast mode                                     | 20 + 0.1 C <sub>B</sub> |     | 300                                                                                                                        | ns    |

| after a Repeated Start<br>Condition and after an | t <sub>RCL1</sub>                  | Fast mode plus                                |                         |     | 120                                                                                                                        | ns    |

| Acknowledge BIT                                  |                                    | High-speed mode, C <sub>B</sub> - 100pF (MAX) | 10                      |     | 80                                                                                                                         | ns    |

|                                                  |                                    | High-speed mode, C <sub>B</sub> - 400pF (MAX) | 20                      |     | 160                                                                                                                        | ns    |

|                                                  |                                    | Standard mode                                 | 20 + 0.1 C <sub>B</sub> |     | 300                                                                                                                        | ns    |

|                                                  |                                    | Fast mode                                     |                         |     | 300                                                                                                                        | ns    |

| Fall Time of SCL Signal                          | t <sub>FCL</sub>                   | Fast mode plus                                |                         |     | 120                                                                                                                        | ns    |

|                                                  |                                    | High-speed mode, C <sub>B</sub> - 100pF (MAX) | 10                      |     | 40                                                                                                                         | ns    |

|                                                  |                                    | High-speed mode, C <sub>B</sub> - 400pF (MAX) | 20                      |     | 80                                                                                                                         | ns    |

|                                                  |                                    | Standard mode                                 |                         |     | 1000                                                                                                                       | ns    |

|                                                  |                                    | Fast mode                                     | 20 + 0.1 C <sub>B</sub> |     | 300                                                                                                                        | ns    |

| Rise Time of SDA Signal                          | t <sub>RDA</sub>                   | Fast mode plus                                |                         |     | 120                                                                                                                        | ns    |

|                                                  |                                    | High-speed mode, C <sub>B</sub> - 100pF (MAX) | 10                      |     | 80                                                                                                                         | ns    |

|                                                  |                                    | High-speed mode, C <sub>B</sub> - 400pF (MAX) | 20                      |     | 160                                                                                                                        | ns    |

|                                                  |                                    | Standard mode                                 |                         |     | 300                                                                                                                        | ns    |

|                                                  |                                    | Fast mode                                     | 20 + 0.1 C <sub>B</sub> |     | 300                                                                                                                        | ns    |

| Fall Time of SDA Signal                          | t <sub>FDA</sub>                   | Fast mode plus                                |                         |     | 120                                                                                                                        | ns    |

|                                                  |                                    | High-speed mode, C <sub>B</sub> - 100pF (MAX) | 10                      |     | 80                                                                                                                         | ns    |

|                                                  |                                    | High-speed mode, C <sub>B</sub> - 400pF (MAX) | 20                      |     | 1000 300 120 40 80 1000 300 120 80 160 300 120 40 80 1000 300 120 40 80 1000 300 120 80 160 300 300 120 80 160 300 300 120 | ns    |

|                                                  |                                    | Standard mode                                 | 4                       |     |                                                                                                                            | μs    |

| Setup Time of STOP                               |                                    | Fast mode                                     | 600                     |     |                                                                                                                            | ns    |

| Condition                                        | t <sub>su</sub> , t <sub>sto</sub> | Fast mode plus                                | 260                     |     |                                                                                                                            | ns    |

|                                                  |                                    | High-Speed mode                               | 160                     |     |                                                                                                                            | ns    |

|                                                  |                                    | Standard mode                                 |                         |     | 400                                                                                                                        | pF    |

| Capacitive Load for SDA                          |                                    | Fast mode                                     |                         |     | 400                                                                                                                        | pF    |

| and SCL                                          | Св                                 | Fast mode plus                                |                         |     | 550                                                                                                                        | pF    |

|                                                  |                                    | High-Speed mode                               |                         |     | 400                                                                                                                        | pF    |

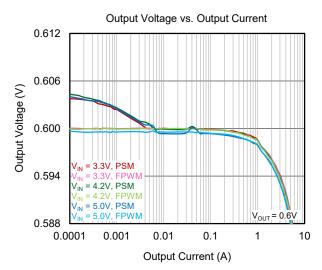

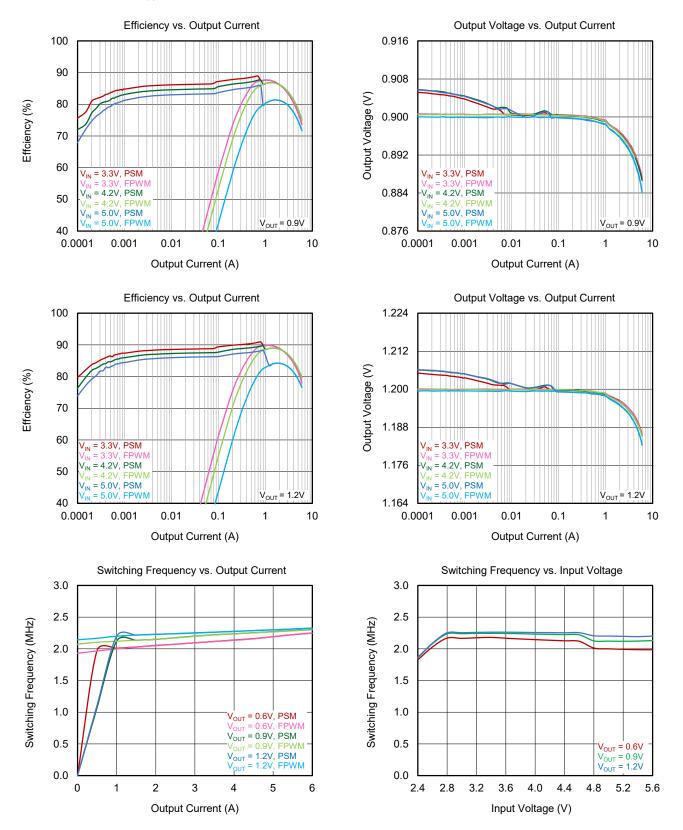

#### TYPICAL PERFORMANCE CHARACTERISTICS

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

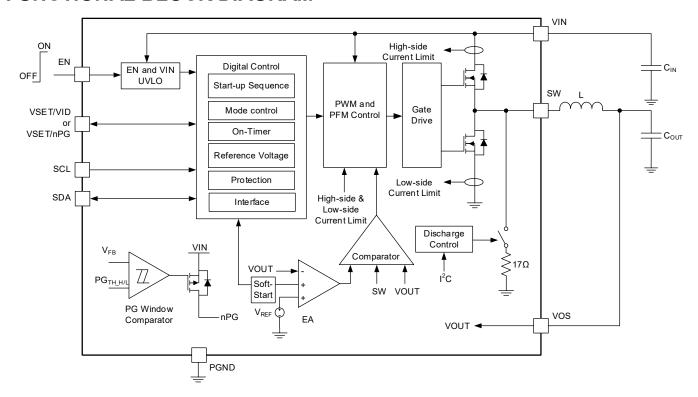

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

#### **DETAILED DESCRIPTION**

#### Overview

The SGM6038 family of synchronous Buck converter consumes  $5\mu A$  (TYP) quiescent current and offers 4A/6A of DC load current in a small TQFN package. The device adopts the constant on-time (COT) architecture to provide superior load transient performance. In addition, the advanced control architecture offers excellent load and line regulation performance.

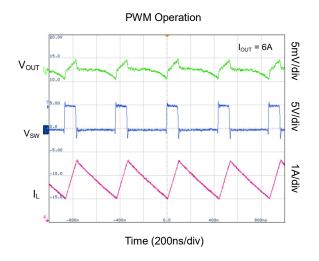

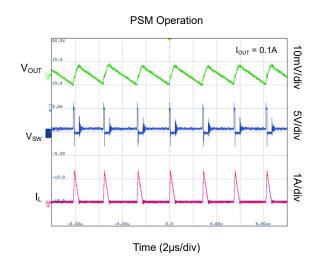

The device operates in PWM mode with 2.3MHz of fixed switching frequency at medium to heavy load. At light load, the device automatically operates in power-save mode to provide excellent light load efficiency. The device only requires two 22µF ceramic output capacitors to achieve minimal output voltage ripple at light load and heavy load.

### **Feature Description**

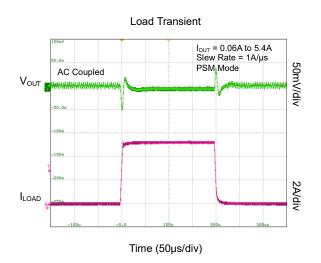

#### **Power-Save Mode**

As the load current decreases, the inductor current reaches around 0A in a switching cycle, and the operation mode becomes discontinuous. The SGM6038 automatically enters power-save mode (PSM) in discontinuous mode. Equation 1 below calculates the device on-time in PSM.

$$t_{ON} = \frac{V_{OUT}}{V_{IN}} \times 416 ns \tag{1}$$

In order to maintain regulation, the output voltage is slightly increased above the programmed voltage. Adding more output capacitors will minimize the output voltage rise in PSM.

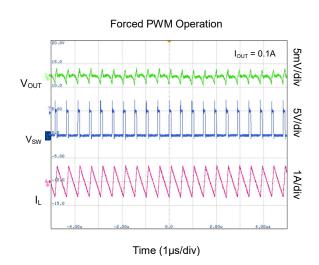

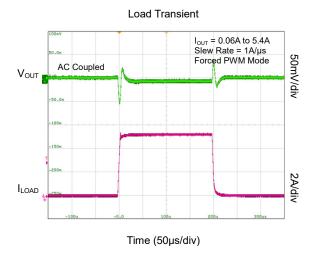

#### Forced PWM Mode (FPWM)

The SGM6038 is able to operate in FPWM mode to achieve fixed switching frequency and output ripple across the entire operating load range. FPWM is configurable in CONTROL register (**REG0x03**) via I<sup>2</sup>C.

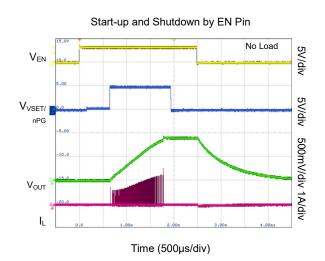

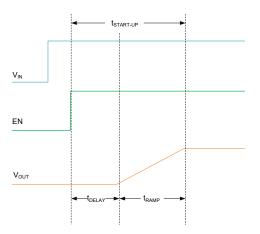

#### Start-up

When the input voltage is above the UVLO rising threshold of 2.2V (TYP), toggling the enable pin to logic high to start up the device. Before the output voltage starts ramping up, the device has an enable delay of 640µs (TYP). During the enable delay, the device establishes the internal reference, and reads the resistor connected to the VSET/VID or VSET/nPG pin to determine the start-up output voltage. The internal registers can be programmed via I<sup>2</sup>C after the enable delay.

Figure 3. Start-up Sequence

The device initiates an internal soft-start when the enable delay finishes. The internal soft-start time is fixed to 1.3ms (TYP) to ramp up the output voltage from 0V to the programmed output voltage. The soft-start mechanism effectively reduces the inrush current drawn from the input source, as well as providing a controlled output voltage rising ramp. For pre-biased output voltage start-up, the device starts up from the pre-biased voltage to the programmed output voltage.

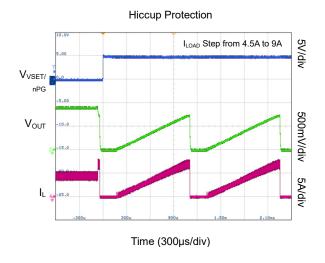

## **Switch Current Limit and Hiccup Short-Circuit Protection**

The device implements over-current protection when the load exceeds the maximum allowed 6A to prevent excessive current drawn from battery type inputs. During an output short scenario or a saturated inductor, the inductor current will reach the current limit threshold. When current limit threshold is reached, the device turns off the high-side switch to terminate the inductor current from further increase, and the low-side switch turns on to ramp down the inductor current to the low-side switch current limit.

During the short-circuit event, as the output voltage drops below 0.3V, the current limit threshold is foldback to 4A for 6A version to prevent the device from excessive temperature rise. When the high-side switch current limit and low-side current limit are triggered for 64 consecutive times, the switching is terminated immediately to enter hiccup short protection mode of 128µs hiccup off-time. The device resumes operation after hiccup off-time with the soft-start sequence. If the over-current or short condition remains, the device remains in the hiccup cycle until the fault condition is removed.

## **DETAILED DESCRIPTION (continued)**

#### **Under-Voltage Lockout (UVLO)**

The SGM6038 offers input under-voltage lockout to prevent false triggering with unstable input source. The device's UVLO rising voltage is 2.2V (TYP) and falling threshold is 2.1V (TYP). The device stops operation as soon as the input voltage drops below the falling threshold. The output voltage discharge is active when UVLO falling threshold is reached, and the output voltage discharge function is programmable via the CONTROL register. The internal register settings are not cleared when UVLO is triggered.

When the input voltage drops below the falling threshold, the UVLO bit in the STATUS register is set, and all register settings will reset until the input voltage drops below 1.8V (TYP).

#### **Thermal Warning and Shutdown**

The SGM6038 is a high power density device, thus when the junction temperature rises above the  $T_{JW}$ , a thermal pre-warning indicator in the STATUS register will toggle high to alert the host, however the device will continue operating.

As the junction temperature continues to rise and exceeds above the  $T_{SD}$ , the device stops switching, enabling active discharge to discharge the output voltage and enters thermal shutdown. The device has a 20°C (TYP) thermal shutdown hysteresis to allow the device to resume operation automatically with internal soft-start. The register settings are not changed during thermal shutdown.

#### **Device Functional Modes**

#### **Enable and Disable (EN)**

I<sup>2</sup>C interface is live when the EN pin is toggled logic high after the enable delay time. When the EN pin is toggled to logic low, power FETs are off as well as the internal control circuits. Register settings are reset except the EN\_OUTPUT\_DISCHG bit. EN pin cannot be left floating.

Device enters shutdown mode when EN pin is logic low. I<sup>2</sup>C communication is terminated in this mode.

The EN pin supports 1.2V I/O logic with 0.66V rising threshold and 0.58V falling threshold.

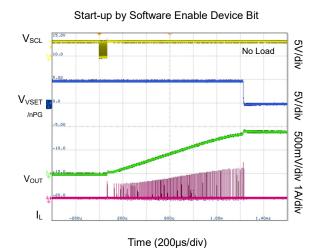

The device also supports a software enable and disable via EN\_DEVICE bit in CONTROL register while EN pin is toggled to logic high. When the device is enabled by this bit, the device starts up with  $t_{\text{RAMP}}$ , and no  $t_{\text{DELAY}}$  is required. When the device is disabled by

this bit, the device stops switching, but I<sup>2</sup>C communication remains active.

#### **Output Discharge**

The device implements I<sup>2</sup>C programmable output voltage discharge function for application requiring sequencing control. The internal discharge path discharges the output voltage through the SW pin to ground. There are four scenarios to discharge the output voltage: EN pin is toggled to logic low, EN\_DEVICE bit is set to 0, input voltage UVLO or device thermal shutdown.

Output voltage discharge function is disabled when the EN\_OUTPUT\_DISCHG bit is set to 0. The output discharge function remains active as long as the input voltage is higher than 1V (TYP) and the EN\_OUTPUT\_DISCHG bit is retained. When a rising edge of the EN pin is applied, the EN\_OUTPUT\_DISCHG bit is reset.

## Start-up Output Voltage and I<sup>2</sup>C Slave Address Selection (VSET)

In start-up phase, during the enable delay period, the resistor is connected to VSET/VID or VSET/nPG pin to program the output voltage as well as device slave address through an internal R2D (resistor-to-digital) converter. Table 1 lists the programmable options.

Table 1. Start-up Output Voltage and I<sup>2</sup>C Slave Address Options

| START-UP<br>OUTPUT<br>VOLTAGE<br>(TYP) | RESISTOR<br>(E96 SERIES, ±1% ACCURACY)<br>AT VSET/VID OR VSET/nPG PIN | I <sup>2</sup> C SLAVE<br>ADDRESS |

|----------------------------------------|-----------------------------------------------------------------------|-----------------------------------|

| 1.15V                                  | 249kΩ                                                                 | 1000 110                          |

| 1.10V                                  | 205kΩ                                                                 | 1000 101                          |

| 1.05V                                  | 162kΩ                                                                 | 1000 100                          |

| 1.00V                                  | 133kΩ                                                                 | 1000 011                          |

| 0.95V                                  | 105kΩ                                                                 | 1000 010                          |

| 0.90V                                  | 86.6kΩ                                                                | 1000 001                          |

| 0.85V                                  | 68.1kΩ                                                                | 1001 000                          |

| 0.80V                                  | 56.2kΩ                                                                | 1001 001                          |

| 0.75V                                  | 44.2kΩ                                                                | 1001 010                          |

| 0.70V                                  | 36.5kΩ                                                                | 1001 011                          |

| 0.65V                                  | 28.7kΩ                                                                | 1001 100                          |

| 0.60V                                  | 23.7kΩ                                                                | 1001 101                          |

| 0.55V                                  | 18.7kΩ                                                                | 1001 110                          |

| 0.50V                                  | 15.4kΩ                                                                | 1001 111                          |

| 0.45V                                  | 12.1kΩ                                                                | 1000 000                          |

| 0.40V                                  | 10kΩ                                                                  | 1000 111                          |

## **DETAILED DESCRIPTION (continued)**

During the enable delay time, a current source is applied on the VSET resistor. The internal ADC converts the voltage on the VSET pin to a digital signal to program the output voltage and I<sup>2</sup>C slave address. Once this R2D conversion completes, the current source is turned off to avoid unnecessary current consumption. Any capacitance higher than 30pF is not recommended to connect between the VSET pin and ground.

If  $I^2C$  command is issued to change the output voltage, the device will ramp up to the VSET resistor programmed output voltage first before ramping up or down to the  $I^2C$  programmed output voltage.

#### **VID**

The device offers 2 selectable output voltage registers via the VID pin, and dynamic voltage scaling (DVS) is supported via these 2 registers. VID pin is pulled to logic low, the output voltage follows **REG0x01**, and VID pin is pulled to logic high, the output voltage follows **REG0x02**.

Output voltage adjustment can be made via either I<sup>2</sup>C programming or toggling the VID pin, and the output voltage ramp up or down speed is also configurable via the RAMP SPEED bits.

#### **Active-Low Power Good**

The SGM6038 offers variants for an active-low power good option if VID function is not used. The device starts to compare the actual output voltage with the VSET resistor programmed output voltage after the enable delay time. When the voltage reaches 91% (TYP) of programmed output voltage, after 200µs delay, the VSET/nPG is pulled low. The VSET/nPG pin remains low as long as the output voltage is within 91% to 111% of the programmed output voltage.

For the VSET/nPG version, a resistor must be connected from this pin to ground to properly configure the start-up voltage and I<sup>2</sup>C slave address. VOUT Register 2 is disabled and this pin's source current is up to 1mA. Due to the active-low logic configuration, in device shutdown, leakage current is increased through the resistor connected to this pin, since the VSET/nPG pin is pulled high.

Table 2. VSET/nPG Pin Logic

|                      | DEVICE CONDITIONS                                                            | VSET/nPG LOGIC STATUS |

|----------------------|------------------------------------------------------------------------------|-----------------------|

| Enable               | $0.91 \times V_{OUT\_NOM} \le V_{VOS} \le 1.11 \times V_{OUT\_NOM}$          | Low                   |

|                      | $V_{VOS} < 0.91 \times V_{OUT\_NOM}$ or $V_{VOS} > 1.11 \times V_{OUT\_NOM}$ | High                  |

| Thermal Shutdown     | $T_{J} > T_{SD}$                                                             | High                  |

| Power Supply Removal | V <sub>IN</sub> < 1.8V                                                       | Undefined             |

### **REGISTER MAPS**

All registers are 8-bit and individual bits are named from D[0] (LSB) to D[7] (MSB).

I<sup>2</sup>C Address Map of SGM6038

| ADDRESS | REGISTER NAME    | D[7]  | D[6]               | D[5]          | D[4]        | D[3]                 | D[2]          | D[1]       | D[0] |

|---------|------------------|-------|--------------------|---------------|-------------|----------------------|---------------|------------|------|

| 0x01    | VOUT Register 1  |       |                    |               | VO1_9       | SET[7:0]             |               |            |      |

| 0x02    | VOUT Register 2  |       | VO2_SET[7:0]       |               |             |                      |               |            |      |

| 0x03    | CONTROL Register | RESET | EN_FPWM_<br>CHANGE | EN_<br>DEVICE | EN_<br>FPWM | EN_OUTPU<br>T_DISCHG | EN_<br>HICCUP | RAMP_SPEED |      |

| 0x05    | STATUS Register  |       | Reserved           |               | T_WARN      | HICCUP               | Reserved      | Reserved   | UVLO |

Bit Types:

R: Read only R/W: Read/Write

REG0x01: VOUT Register 1 [Reset = 0x64]

| BITS   | BIT NAME     | DEFAULT   | TYPE | DESCRIPTION                                                                                                        |

|--------|--------------|-----------|------|--------------------------------------------------------------------------------------------------------------------|

| D[7:0] | VO1_SET[7:0] | 0110 0100 | R/W  | Output Voltage<br>0x00 = 400mV<br>0x01 = 405mV<br><br>0x64 = 900mV (default)<br><br>0xFE = 1670mV<br>0xFF = 1675mV |

**REG0x02: VOUT Register 2 [Reset = 0x64]**

|        | (100x01: 100: 100; 100; 1 [1000t |           |      |                                                                                                                    |  |  |  |  |  |

|--------|----------------------------------|-----------|------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BITS   | BIT NAME                         | DEFAULT   | TYPE | DESCRIPTION                                                                                                        |  |  |  |  |  |

| D[7:0] | VO2_SET[7:0]                     | 0110 0100 | R/W  | Output Voltage<br>0x00 = 400mV<br>0x01 = 405mV<br><br>0x64 = 900mV (default)<br><br>0xFE = 1670mV<br>0xFF = 1675mV |  |  |  |  |  |

## **REGISTER MAPS (continued)**

**REG0x03: CONTROL Register [Reset = 0x6F]**

| BITS   | BIT NAME             | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                     |

|--------|----------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7]   | RESET                | 0       | R/W  | 1 = Reset all registers to default                                                                                                                                              |

| D[6]   | EN_FPWM_CHANGE       | 1       | R/W  | Enable FPWM mode during output voltage change 0 = Keep the current mode status during output voltage change 1 = Force the device in FPWM during output voltage change (default) |

| D[5]   | EN_DEVICE            | 1       | R/W  | Software Enable Device 0 = Disable the device. All registers values are still kept 1 = Re-enable the device with a new start-up without the t <sub>DELAY</sub> period (default) |

| D[4]   | EN_FPWM              | 0       | R/W  | Enable FPWM Mode  0 = Set the device in power-save mode at light loads (default)  1 = Set the device in forced PWM mode at light loads                                          |

| D[3]   | EN_OUTPUT_DISCH<br>G | 1       | R/W  | Enable Output Discharge 0 = Disable output discharge 1 = Enable output discharge (default)                                                                                      |

| D[2]   | EN_HICCUP            | 1       | R/W  | Enable Hiccup  0 = Disable Hiccup. Enable latching protection  1 = Enable Hiccup. Disable latching protection (default)                                                         |

| D[1:0] | RAMP_SPEED           | 11      | R/W  | Voltage Ramp Speed 00 = 20mV/µs (0.25µs/step) 01 = 10mV/µs (0.5µs/step) 10 = 5mV/µs (1µs/step) 11 = 1mV/µs (5µs/step, default)                                                  |

**REG0x05: STATUS Register [Reset = 0x00]**

| BITS   | BIT NAME | DEFAULT | TYPE | DESCRIPTION                                                      |

|--------|----------|---------|------|------------------------------------------------------------------|

| D[7:5] | Reserved |         |      | Reserved.                                                        |

| D[4]   | T_WARN   | 0       | R    | Thermal warning. 1 = Junction temperature is higher than +130°C. |

| D[3]   | HICCUP   | 0       | R    | 1 = Device has Hiccup status once.                               |

| D[2]   | Reserved |         |      | Reserved.                                                        |

| D[1]   | Reserved |         |      | Reserved.                                                        |

| D[0]   | UVLO     | 0       | R    | 1 = The input voltage is less than the UVLO falling threshold.   |

### **APPLICATION INFORMATION**

## **Typical Application**

Figure 4 below shows a typical schematic for a 0.9V output application with a wide input voltage range.

Figure 4. 6A Output Current Typical Application

#### **Design Requirements**

Table 3 below shows the operation conditions of this design example.

**Table 3. Design Parameters**

| DESIGN PARAMETER       | EXAMPLE VALUE |

|------------------------|---------------|

| Input Voltage          | 2.4V to 5.5V  |

| Output Voltage         | 0.9V          |

| Maximum Output Current | 6A            |

Table 4 lists the components used for the example.

**Table 4. List of Components**

| REFERENCE      | DESCRIPTION                                                       | MANUFACTURER |

|----------------|-------------------------------------------------------------------|--------------|

| C <sub>1</sub> | 10μF, ceramic capacitor, 6.3V, X7R, size 0603, CL10B106MQ8NRNC    | Samsung      |

| C <sub>2</sub> | 22μF, ceramic capacitor, 6.3V, X7R, size 0805, GRM21BZ70J226ME44L | Murata       |

| L <sub>1</sub> | 0.24µH, power inductor, size 0806, DFE201612E-R24M=P2             | Murata       |

| R <sub>1</sub> | Depending on the start-up output voltage, size 0603               | Std          |

#### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes   | from    | Original  | (FEBRUARY  | 2025) | to REV A |

|-----------|---------|-----------|------------|-------|----------|

| Citaliyes | 11 0111 | Oligiliai | (FEBRUAR I | 20231 | IU NEV.A |

Page

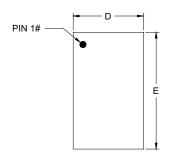

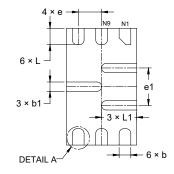

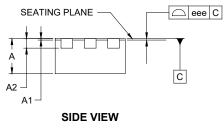

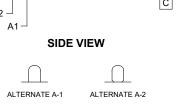

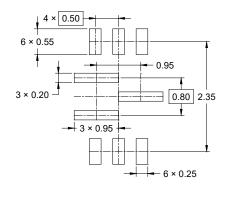

## **PACKAGE OUTLINE DIMENSIONS** TQFN-1.5×2.5-9L

#### **TOP VIEW**

**BOTTOM VIEW**

**DETAIL A** ALTERNATE TERMINAL CONSTRUCTION

RECOMMENDED LAND PATTERN (Unit: mm)

| Cymahal | Dimensions In Millimeters |           |       |  |  |  |  |

|---------|---------------------------|-----------|-------|--|--|--|--|

| Symbol  | MIN                       | NOM       | MAX   |  |  |  |  |

| Α       | 0.700                     | -         | 0.800 |  |  |  |  |

| A1      | 0.000                     | -         | 0.050 |  |  |  |  |

| A2      |                           | 0.203 REF |       |  |  |  |  |

| b       | 0.200                     | -         | 0.300 |  |  |  |  |

| b1      | 0.150                     | -         | 0.250 |  |  |  |  |

| D       | 1.400                     | -         | 1.600 |  |  |  |  |

| E       | 2.400                     | 2.400 -   |       |  |  |  |  |

| е       | 0.500 BSC                 |           |       |  |  |  |  |

| e1      | 0.800 BSC                 |           |       |  |  |  |  |

| L       | 0.250                     | -         | 0.450 |  |  |  |  |

| L1      | 0.650                     | -         | 0.850 |  |  |  |  |

| eee     | 0.080                     |           |       |  |  |  |  |

NOTE: This drawing is subject to change without notice.

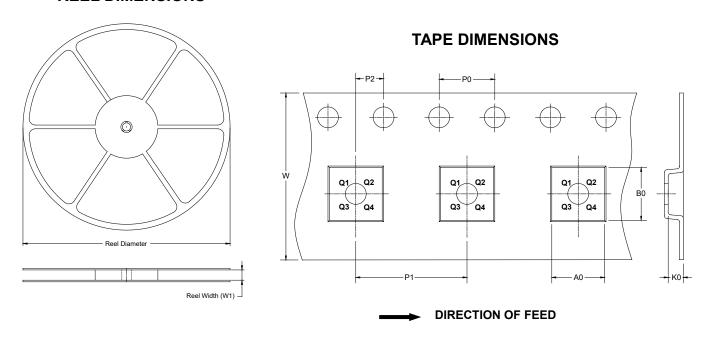

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type    | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-1.5×2.5-9L | 7"               | 9.5                      | 1.70       | 2.70       | 0.95       | 4.0        | 4.0        | 2.0        | 8.0       | Q1               |

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-------------|----------------|---------------|----------------|--------------|

| 7" (Option) | 368            | 227           | 224            | 8            |

| 7"          | 442            | 410           | 224            | 18           |