# 74LVTN16374 3.3V, 16-Bit D-Type Edge-Triggered Flip-Flops with 3-State Outputs

## **GENERAL DESCRIPTION**

The 74LVTN16374 is high performance product designed for  $V_{CC}$  operation at 3.3V. The device is 16-bit edge-triggered D-type flip-flops with non-inverting 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. It is particularly suitable for implementing buffer registers, I/O ports, bidirectional bus drivers and working registers.

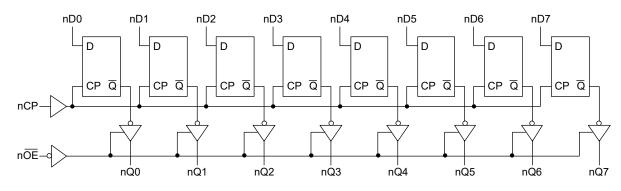

The device can be used as two 8-bit flip-flops or one 16-bit flip-flop. On the positive transition of the clock (nCP) input, the nQn outputs of the flip-flop take on the logic levels set up at the nDn inputs.

An output enable  $(n\overline{OE})$  input can be used to place the 8 outputs in either a normal logic state (high or low logic levels) or a high-impedance state.

$n\overline{OE}$  does not affect internal operations of the flip-flop. Old data can be retained or new data can be entered while the outputs are in the high-impedance state.

# FEATURES

- 16-Bit Edge-Triggered Flip-Flop

- 3-State Buffers

- Output Capability: +64mA/-32mA

- TTL Input and Output Switching Levels

- Input and Output Interface Capability to Systems at 5V Supply

- Live Insertion and Extraction Permitted

- Power-Up Reset

- Power-Up 3-State

- No Bus Current Loading When Output is Tied to 5V Bus

- -40°C to +125°C Operating Temperature Range

- Available in a Green TSSOP-48 Package

## PACKAGE/ORDERING INFORMATION

| MODEL       | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER   | PACKAGE<br>MARKING            | PACKING<br>OPTION   |

|-------------|------------------------|-----------------------------------|----------------------|-------------------------------|---------------------|

| 74LVTN16374 | TSSOP-48               | -40°C to +125°C                   | 74LVTN16374XTS48G/TR | 74LVTN16374<br>XTS48<br>XXXXX | Tape and Reel, 2500 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

<u>XXXXX</u>

- Vendor Code

- ——— Trace Code ——— Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Supply Voltage, V <sub>CC</sub>                                | 0.5V to 4.6V |

|----------------------------------------------------------------|--------------|

| Input Voltage, VI <sup>(2)</sup>                               | 0.5V to 7V   |

| Output Voltage, Vo <sup>(2)</sup>                              |              |

| Output in 3-State or High-State                                | 0.5V to 7V   |

| Input Clamping Current, I <sub>IK</sub> (V <sub>I</sub> < 0V)  | 50mA         |

| Output Clamping Current, I <sub>OK</sub> (V <sub>O</sub> < 0V) | 50mA         |

| Output Current, I <sub>O</sub>                                 |              |

| Output in High-State                                           | 64mA         |

| Output in Low-State                                            | 128mA        |

| Supply Current, I <sub>CC</sub>                                | 128mA        |

| Ground Current, I <sub>GND</sub>                               |              |

| Junction Temperature <sup>(3)</sup>                            |              |

| Storage Temperature Range65°                                   | C to +150°C  |

| Lead Temperature (Soldering, 10s)                              | +260°C       |

| ESD Susceptibility                                             |              |

| HBM                                                            | 7000V        |

| CDM                                                            | 1000V        |

### **RECOMMENDED OPERATING CONDITIONS**

| Supply Voltage, V <sub>CC</sub>                            | 2.7V to 3.6V |

|------------------------------------------------------------|--------------|

| Input Voltage, V <sub>I</sub>                              | 0V to 5.5V   |

| High-Level Output Current, IOH                             | 32mA         |

| Low-Level Output Current, IoL                              | 64mA         |

| Input Transition Rise and Fall Rate, $\Delta t / \Delta V$ |              |

|                                                            | 10ns/V (MAX) |

| Operating Temperature Range                                | 40℃ to +125℃ |

### **OVERSTRESS CAUTION**

1. Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

2. The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.

3. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability.

### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

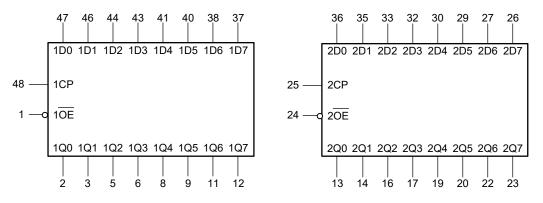

## LOGIC SYMBOL

## LOGIC DIAGRAM

# **FUNCTION TABLE**

| OPERATING MODE         | со  | NTROL INF | TUY | INTERNAL | OUTPUT |

|------------------------|-----|-----------|-----|----------|--------|

| OF ERATING MODE        | nOE | nCP       | nDn | REGISTER | nQn    |

| Lood and Dood Degister | L   | 1         | I   | L        | L      |

| Load and Read Register | L   | 1         | h   | н        | Н      |

| Hold                   | L   | NC        | X   | NC       | NC     |

| Dischla Qutnuta        | Н   | NC        | X   | NC       | Z      |

| Disable Outputs        | Н   | 1         | nDn | nDn      | Z      |

H = High Voltage Level

L = Low Voltage Level

$\uparrow$  = Low-to-High Clock Transition

h = High Voltage Level One Set-Up Time Prior to the Low-to-High Clock Transition

I = Low Voltage Level One Set-Up Time Prior to Low-to-High Clock Transition

Z = High-Impedance State

NC = No Change

X = Don't Care

## 3.3V, 16-Bit D-Type Edge-Triggered Flip-Flops with 3-State Outputs

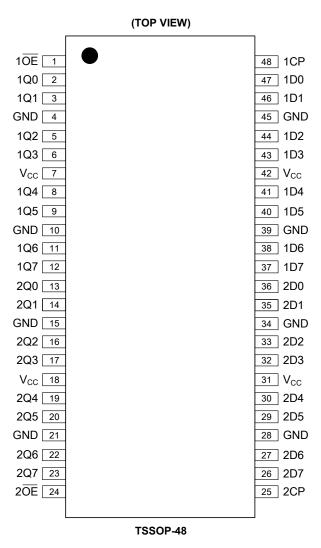

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN                            | NAME                                   | FUNCTION                           |

|--------------------------------|----------------------------------------|------------------------------------|

| 47, 46, 44, 43, 41, 40, 38, 37 | 1D0, 1D1, 1D2, 1D3, 1D4, 1D5, 1D6, 1D7 | Data Inputs.                       |

| 36, 35, 33, 32, 30, 29, 27, 26 | 2D0, 2D1, 2D2, 2D3, 2D4, 2D5, 2D6, 2D7 | Data Inputs.                       |

| 1, 24                          | 10E, 20E                               | Output Enable Inputs (Active Low). |

| 48, 25                         | 1CP, 2CP                               | Clock Inputs.                      |

| 2, 3, 5, 6, 8, 9, 11, 12       | 1Q0, 1Q1, 1Q2, 1Q3, 1Q4, 1Q5, 1Q6, 1Q7 | Data Outputs.                      |

| 13, 14, 16, 17, 19, 20, 22, 23 | 2Q0, 2Q1, 2Q2, 2Q3, 2Q4, 2Q5, 2Q6, 2Q7 | Data Outputs.                      |

| 4, 10, 15, 21, 28, 34, 39, 45  | GND                                    | Ground.                            |

| 7, 18, 31, 42                  | V <sub>cc</sub>                        | Supply Voltage.                    |

# **ELECTRICAL CHARACTERISTICS**

(Full = -40°C to +125°C, all typical values are measured at  $V_{CC}$  = 3.3V and  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                        | SYMBOL               | CONDI                                                                          | TEMP                                                                                                  | MIN   | TYP                    | MAX                     | UNITS |    |

|--------------------------------------------------|----------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|------------------------|-------------------------|-------|----|

| Input Clamping Voltage                           | VIK                  | V <sub>CC</sub> = 2.7V, I <sub>IK</sub> = -18mA                                |                                                                                                       | Full  | -1.2                   | -0.78                   |       | V  |

| High-Level Input Voltage                         | V <sub>IH</sub>      | V <sub>CC</sub> = 2.7V to 3.6V                                                 |                                                                                                       | Full  | 2                      |                         |       | V  |

| Low-Level Input Voltage                          | VIL                  | V <sub>CC</sub> = 2.7V to 3.6V                                                 |                                                                                                       | Full  |                        |                         | 0.8   | V  |

|                                                  |                      | I <sub>OH</sub> = -100µA, V <sub>CC</sub> = 2.7V                               | to 3.6V                                                                                               | Full  | V <sub>CC</sub> - 0.05 | V <sub>CC</sub> - 0.001 |       |    |

| High-Level Output Voltage                        | V <sub>он</sub>      | I <sub>он</sub> = -8mA, V <sub>cc</sub> = 2.7V                                 |                                                                                                       | Full  | 2.45                   | 2.6                     |       | V  |

|                                                  |                      | I <sub>OH</sub> = -32mA, V <sub>CC</sub> = 3.0V                                |                                                                                                       | Full  | 2.1                    | 2.65                    |       |    |

|                                                  |                      | $y_{1} = 0.7y_{1}$                                                             | I <sub>OL</sub> = 100μA                                                                               | Full  |                        | 0.001                   | 0.05  |    |

|                                                  |                      | $V_{CC} = 2.7V$                                                                | I <sub>OL</sub> = 24mA                                                                                | Full  |                        | 0.15                    | 0.28  |    |

| Low-Level Output Voltage                         | V <sub>OL</sub>      |                                                                                | I <sub>OL</sub> = 16mA                                                                                | Full  |                        | 0.1                     | 0.18  | V  |

|                                                  |                      | V <sub>CC</sub> = 3.0V                                                         | I <sub>OL</sub> = 32mA                                                                                | Full  |                        | 0.2                     | 0.36  |    |

|                                                  |                      |                                                                                | I <sub>OL</sub> = 64mA                                                                                | Full  |                        | 0.4                     | 0.55  | 1  |

| Power-Up Low-Level Output Voltage <sup>(1)</sup> | $V_{OL_{PU}}$        | $V_{CC} = 3.6V, I_{OL} = 1mA, V_{I}$                                           | Full                                                                                                  |       | 5                      | 50                      | mV    |    |

|                                                  |                      | Control pins, $V_{CC}$ = 3.6V, $V_1$ = $V_{CC}$ or GND                         |                                                                                                       | Full  |                        | ±0.01                   | ±1    |    |

|                                                  |                      | Control pins, V <sub>CC</sub> = 0V or                                          | Full                                                                                                  |       | 0.01                   | 5                       |       |    |

| Input Leakage Current                            | l,                   | Input data pins $^{(2)}$ , V <sub>CC</sub> = 0V or 3.6V, V <sub>I</sub> = 5.5V |                                                                                                       | Full  |                        | 0.01                    | 5     | μA |

|                                                  |                      | Input data pins <sup>(2)</sup> , $V_{CC}$ = 3.6V, $V_{I}$ = $V_{CC}$           |                                                                                                       | Full  |                        | 0.01                    | 1     |    |

|                                                  |                      | Input data pins $^{(2)}$ , V <sub>CC</sub> = 3                                 | 3.6V, V <sub>I</sub> = GND                                                                            | Full  | -2                     | -0.01                   |       |    |

| Off State Output Current                         |                      | V = 2.6V                                                                       | V <sub>o</sub> = 3.0V                                                                                 | Full  |                        | 0.01                    | 2     |    |

| Off-State Output Current                         | l <sub>oz</sub>      | V <sub>CC</sub> = 3.6V                                                         | V <sub>o</sub> = 0.5V                                                                                 | Full  | -2                     | -0.01                   |       | μA |

| Output Leakage Current                           | ILO                  | Output in high-state when $V_0 = 5.5V$ , $V_{CC} = 3.0V$                       |                                                                                                       | Full  |                        | 1                       | 30    | μA |

| Power-Up/Down Output<br>Current                  | I <sub>O_PU/PD</sub> | $V_{CC} \le 1.2V, V_0 = 0.5V$ to<br>nOE = don't care                           | $V_{CC}$ , $V_{I}$ = GND or $V_{CC}$ ,                                                                | +25°C |                        | 0.01                    | 10    | μA |

| Power-Off Leakage<br>Current                     | I <sub>OFF</sub>     | $V_{CC} = 0V$ , $V_I$ or $V_O = 0V$ to                                         | o 5.5V                                                                                                | Full  |                        | 0.01                    | 10    | μA |

|                                                  |                      | $V_{CC} = 3.6V$ ,                                                              | Outputs high                                                                                          | Full  |                        | 12                      | 80    |    |

| Supply Current                                   | I <sub>cc</sub>      | $V_1 = GND \text{ or } V_{CC},$                                                | Outputs low                                                                                           | Full  |                        | 12                      | 80    | μA |

|                                                  |                      | I <sub>0</sub> = 0A                                                            | Outputs disabled <sup>(3)</sup>                                                                       | Full  |                        | 12                      | 80    | 1  |

| Additional Supply Current <sup>(4)</sup>         | $\Delta I_{CC}$      |                                                                                | Per input pin, $V_{CC}$ = 3.0V to 3.6V, one input at $V_{CC}$ - 0.6V, other inputs at $V_{CC}$ or GND |       |                        | 0.2                     | 80    | μA |

| Input Capacitance                                | Cı                   | Input pins, $V_1 = 0V$ or 3.0                                                  | V                                                                                                     | +25℃  |                        | 6                       |       | pF |

| Output Capacitance                               | Co                   | Output pins nQn, outputs $V_0 = 0V$ or $V_{CC}$                                | disabled,                                                                                             | +25°C |                        | 9                       |       | pF |

NOTES:

1. For valid test results, data must not be loaded into the flips-flops (or latches) after applying power.

2. Unused pins at  $V_{CC}$  or GND.

3.  $I_{\text{CC}}$  is measured with outputs pulled to  $V_{\text{CC}}$  or GND.

4. This is the increase in supply current for each input at the specified voltage level other than V<sub>CC</sub> or GND.

## 3.3V, 16-Bit D-Type Edge-Triggered Flip-Flops with 3-State Outputs

# **DYNAMIC CHARACTERISTICS**

(For test circuit, see Figure 1. All typical values are measured at  $V_{CC}$  = 3.3V and  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                            | SYMBOL           | CONDITI                               | TEMP                                      | MIN   | TYP | MAX | UNITS |      |  |

|--------------------------------------|------------------|---------------------------------------|-------------------------------------------|-------|-----|-----|-------|------|--|

| Maximum Frequency                    | f <sub>MAX</sub> | nCP, $V_{CC}$ = 3.3V ± 0.3V, se       | nCP, $V_{CC}$ = 3.3V ± 0.3V, see Figure 2 |       |     |     |       | MHz  |  |

| Low to High Propagation Delay        | +                | nCP to nQn, see Figure 2              | $V_{CC} = 3.3V \pm 0.3V$                  | +25°C |     | 3.4 |       |      |  |

| Low to high Propagation Delay        | t <sub>PLH</sub> | nor to non, see rigule 2              | V <sub>CC</sub> = 2.7V                    | +25°C |     | 3.9 |       | ns   |  |

| High to Low Propagation Delay        | +                | nCP to nQn, see Figure 2              | $V_{CC} = 3.3V \pm 0.3V$                  | +25°C |     | 3.3 |       | 20   |  |

| High to Low Propagation Delay        | t <sub>PHL</sub> | nor to hon, see rigule 2              | V <sub>CC</sub> = 2.7V                    | +25°C |     | 3.5 |       | ns   |  |

| Off State to Lligh Branagation Dalay |                  |                                       | $V_{CC} = 3.3V \pm 0.3V$                  | +25°C |     | 4.3 |       | 20   |  |

| Off-State to High Propagation Delay  | t <sub>PZH</sub> | nOE to nQn, see Figure 3              | V <sub>CC</sub> = 2.7V                    | +25°C |     | 3.9 |       | ns   |  |

| Off-State to Low Propagation         | +                |                                       | $V_{CC} = 3.3V \pm 0.3V$                  | +25°C |     | 4.4 |       | 20   |  |

| Delay                                | t <sub>PZL</sub> | nOE to nQn, see Figure 3              | V <sub>CC</sub> = 2.7V                    | +25°C |     | 4.3 |       | ns   |  |

|                                      |                  | $n\overline{OE}$ to nQn, see Figure 3 | $V_{CC} = 3.3V \pm 0.3V$                  | +25°C |     | 4.5 |       | 20   |  |

| High to Off-State Propagation Delay  | t <sub>PHZ</sub> |                                       | V <sub>CC</sub> = 2.7V                    | +25°C |     | 4   |       | ns   |  |

| Low to Off-State Propagation         | +                |                                       | $V_{CC} = 3.3V \pm 0.3V$                  | +25°C |     | 3.8 |       | 20   |  |

| Delay                                | t <sub>PLZ</sub> | $n\overline{OE}$ to nQn, see Figure 3 | V <sub>CC</sub> = 2.7V                    | +25°C |     | 3.4 |       | ns   |  |

| Cat Lin Tima                         |                  | nDn to nCP, high or low,              | $V_{CC} = 3.3V \pm 0.3V$                  | +25°C |     | 0.3 |       | 20   |  |

| Set-Up Time                          | ts∪              | see Figure 4                          | V <sub>CC</sub> = 2.7V                    | +25°C |     | 0.3 |       | ns   |  |

| Hold Time                            |                  | nDn to nCP, high or low,              | $V_{CC} = 3.3V \pm 0.3V$                  | +25°C |     | 0.2 |       | 20   |  |

|                                      | t <sub>H</sub>   | see Figure 4                          | V <sub>CC</sub> = 2.7V                    | +25°C |     | 0.2 |       | ns   |  |

|                                      |                  |                                       | $V_{CC} = 3.3V \pm 0.3V$                  | +25°C |     | 1.5 |       |      |  |

| Dulas Width                          | +                | nCP high, see Figure 2                | V <sub>CC</sub> = 2.7V                    | +25°C |     | 1.5 |       |      |  |

| Pulse Width                          | tw               |                                       | $V_{CC} = 3.3V \pm 0.3V$                  | +25°C |     | 1.5 |       | - ns |  |

|                                      |                  | nCP low, see Figure 2                 | V <sub>CC</sub> = 2.7V                    | +25°C |     | 1.5 |       |      |  |

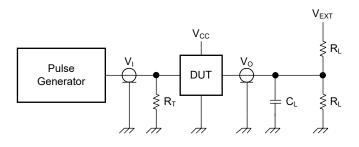

# **TEST CIRCUIT**

Test conditions are given in Table 1.

Definitions for test circuit:

R<sub>L</sub> = Load resistance.

C<sub>L</sub> = Load capacitance including jig and probe capacitance.

$R_T$  = Termination resistance should be equal to output impedance  $Z_0$  of the pulse generator.

V<sub>EXT</sub> = External voltage for measuring switching times.

#### Figure 1. Test Circuit for Measuring Switching Times

#### Table 1. Test Conditions

| SUPPLY VOLTAGE  | INPUT |         |       | LOAD                            |      | V <sub>EXT</sub> |                                     |                    |                                     |

|-----------------|-------|---------|-------|---------------------------------|------|------------------|-------------------------------------|--------------------|-------------------------------------|

| V <sub>cc</sub> | VI    | fi      | tw    | t <sub>R</sub> , t <sub>F</sub> | CL   | RL               | t <sub>PHZ</sub> , t <sub>PZH</sub> | $t_{PLZ}, t_{PZL}$ | t <sub>PLH</sub> , t <sub>PHL</sub> |

| 2.7V to 3.6V    | 2.7V  | ≤ 10MHz | 500ns | ≤ 2.5ns                         | 50pF | 500Ω             | GND                                 | 6V                 | Open                                |

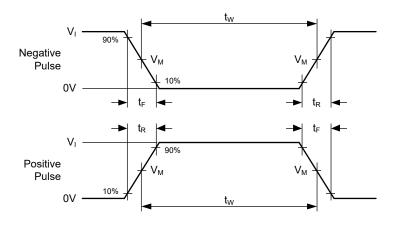

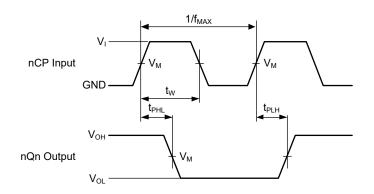

# WAVEFORMS

Test conditions are given in Table 1.

Measurement points are given in Table 2.

Logic levels:  $V_{OL}$  and  $V_{OH}$  are typical output voltage levels that occur with the output load.

#### Figure 2. Clock Input to Output Propagation Delays, Clock Pulse Width and Maximum Clock Frequency

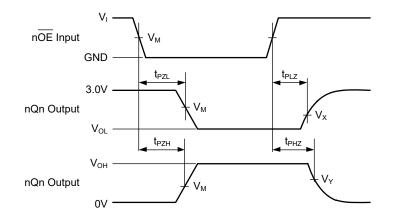

Test conditions are given in Table 1.

Measurement points are given in Table 2.

Logic levels:  $V_{\text{OL}}$  and  $V_{\text{OH}}$  are typical output voltage levels that occur with the output load.

#### Figure 3. Enable and Disable Times

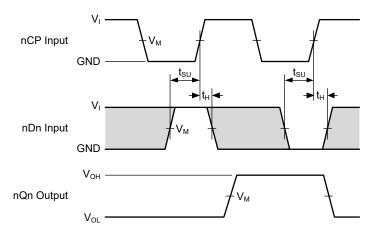

# WAVEFORMS (continued)

Test conditions are given in Table 1.

Measurement points are given in Table 2.

Logic levels:  $V_{OL}$  and  $V_{OH}$  are typical output voltage levels that occur with the output load.

The shaded areas indicate when the input is permitted to change for predictable output performance.

#### Figure 4. Data Set-Up and Hold Times

#### Table 2. Measurement Points

| SUPPLY VOLTAGE  | INF  | TU             |                |                        |                        |

|-----------------|------|----------------|----------------|------------------------|------------------------|

| V <sub>cc</sub> | VI   | V <sub>M</sub> | V <sub>M</sub> | V <sub>Y</sub>         |                        |

| 2.7V to 3.6V    | 2.7V | 1.5V           | 1.5V           | V <sub>OL</sub> + 0.3V | V <sub>OH</sub> - 0.3V |

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| NOVEMBER 2021 – REV.A to REV.A.1                      | Page |

|-------------------------------------------------------|------|

| Updated HBM value in Absolute Maximum Ratings section | 2    |

|                                                       |      |

| Changes from Original (MARCH 2021) to REV.A           | Page |

| Changed from product preview to production data       | All  |

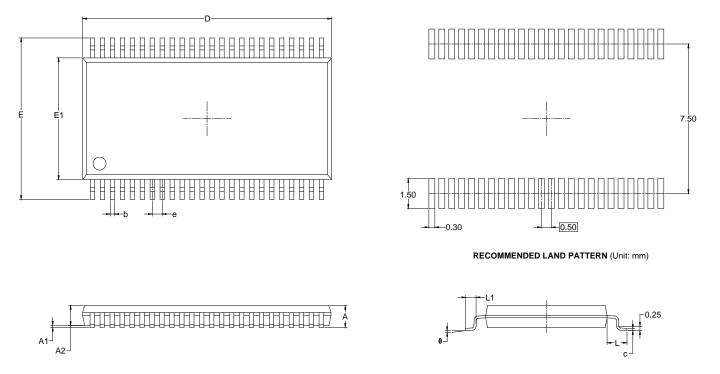

# **PACKAGE OUTLINE DIMENSIONS**

## **TSSOP-48**

| Symbol | D     | imensions In Millimet | ers   |

|--------|-------|-----------------------|-------|

| Symbol | MIN   | MOD                   | MAX   |

| A      |       |                       | 1.20  |

| A1     | 0.05  | 0.10                  | 0.15  |

| A2     | 0.85  | 0.95                  | 1.05  |

| b      | 0.18  |                       | 0.26  |

| С      | 0.15  |                       | 0.19  |

| D      | 12.40 | 12.50                 | 12.60 |

| E      | 7.90  | 8.10                  | 8.30  |

| E1     | 6.00  | 6.10                  | 6.20  |

| е      |       | 0.50 BSC              |       |

| L      |       | 1.00 REF              |       |

| L1     | 0.45  |                       | 0.75  |

| θ      | 0°    |                       | 8°    |

NOTES: 1. Body dimensions do not include mode flash or protrusion.

2. This drawing is subject to change without notice.

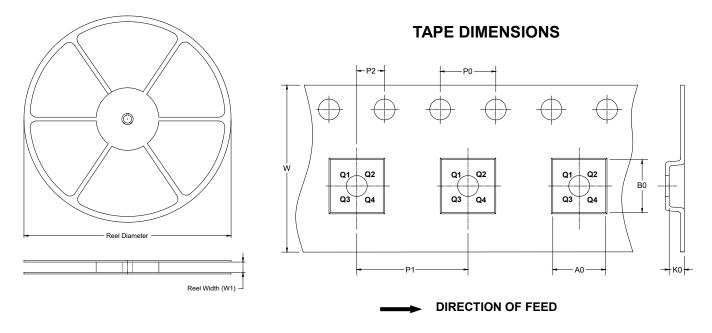

# TAPE AND REEL INFORMATION

### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TSSOP-48     | 13"              | 24.4                     | 8.60       | 13.00      | 1.80       | 4.0        | 12.0       | 2.0        | 24.0      | Q1               |

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |