### **GENERAL DESCRIPTION**

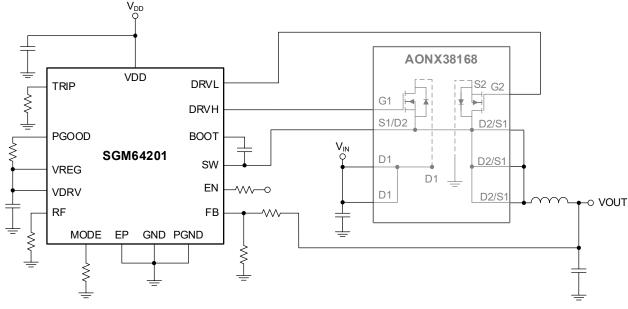

The SGM64201 is a 4.5V to 25V controller with adaptive constant on-time (ACOT) control for synchronous Buck converters. It is capable to efficiently drive two N-MOSFETs over the whole voltage range. The SGM64201 exports the maximize power and limits the maximum valley current of the low-side MOSFET. The forced pulse width modulation (FPWM) mode or power saving mode (PSM) at light load is configurable through the voltage of MODE pin.

Eight preset switching frequency can be selected by an external resistor between the RF pin and GND or between the RF pin and the VREG pin.

The SGM64201 is available in a Green TQFN-3×3-16FL package.

### **APPLICATIONS**

Server Computers Storage Computers Embedded Computing Multi-Function Printers

# FEATURES

- Wide Conversion Input Voltage: 3V to 26V

- Wide VDD Input Voltage: 4.5V to 25V

- Adjustable Output Voltage: 0.6V to 5.5V

- Continuous Output Current: > 20A

- Precise Reference of 600mV: ±0.7%

- 5.2V Built-in LDO

- Power Saving Mode for Light-Load Efficiency

- Adaptive Constant On-Time Mode Control

- 8 Selectable Frequency Settings

- 4700ppm/°C R<sub>DSON</sub> Current Sensing

- 4 Selectable Soft-Start Time Settings with Pre-Biased Capability

- Power Good (PG) Indicator

- Output OVP and UVP Protections

- Over Temperature Protection (OTP) with Auto Recovery

- Available in a Green TQFN-3×3-16FL Package

### **PACKAGE/ORDERING INFORMATION**

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM64201 | TQFN-3×3-16FL          | -40°C to +125°C                   | SGM64201YTUZ16G/TR | 0TKUZ<br>XXXXX     | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

| Х | Х | Х | Х | Х |

|---|---|---|---|---|

| Τ |   |   |   | T |

└─── Vendor Code ───── Trace Code

Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

Input Voltage

| 1 5                                                |  |

|----------------------------------------------------|--|

| BOOT0.3V to 34.5V                                  |  |

| BOOT (with Respect to the SW Terminal)0.3V to 6.5V |  |

| VDD0.3V to 28V                                     |  |

| SW (DC)2V to 28V                                   |  |

| SW (Pulse < 20ns, E = 5µJ)6.5V                     |  |

| VDRV, EN, TRIP, FB, RF, MODE0.3V to 6.5V           |  |

| Output Voltage                                     |  |

| DRVH2V to 34.5V                                    |  |

| DRVH (with Respect to the SW Terminal)0.3V to 6.5V |  |

| DRVL, VREG0.5V to 6.5V                             |  |

| PGOOD0.3V to 6.5V                                  |  |

| Package Thermal Resistance                         |  |

| TQFN-3×3-16FL, θ <sub>JA</sub> 62.7°C/W            |  |

| TQFN-3×3-16FL, θ <sub>JB</sub>                     |  |

| TQFN-3×3-16FL, θ <sub>JC(TOP)</sub> 51°C/W         |  |

| TQFN-3×3-16FL, θ <sub>JC(BOT)</sub> 5.8°C/W        |  |

| Junction Temperature+150°C                         |  |

| Storage Temperature Range65°C to +150°C            |  |

| Lead Temperature (Soldering, 10s)+260°C            |  |

| ESD Susceptibility <sup>(1) (2)</sup>              |  |

| HBM±2000V                                          |  |

| CDM±1000V                                          |  |

|                                                    |  |

#### NOTES:

1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### **RECOMMENDED OPERATING CONDITIONS**

Input Voltage BOOT .....--0.1V to 31V

| BOOT (with Respect to the SW Terminal)0.1 <sup>1</sup><br>VDD4.5V |          |

|-------------------------------------------------------------------|----------|

| SW1V                                                              | to 26V   |

| VDRV, EN, TRIP, FB, RF, MODE0.11                                  | V to 5V  |

| Output Voltage                                                    |          |

| DRVH1V                                                            | to 31V   |

| DRVH (with Respect to the SW Terminal)0.1                         | V to 5V  |

| DRVL, VREG0.3                                                     | V to 5V  |

|                                                                   | to EV    |

| PGOOD0.1                                                          | V 10 5 V |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

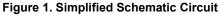

### **PIN CONFIGURATION**

### **PIN DESCRIPTION**

| PIN            | NAME  | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                              |

|----------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | TRIP  | I    | Set Pin for Over-Current Threshold. Place a resistor from this pin to GND, $V_{TRIP} = I_{TRIP} \times R_{TRIP}$ , $V_{OCL} = V_{TRIP}/8$ .                                                                                                                                              |

| 2              | EN    | I    | Active-High Enable Input Pin. Pull it up to a logic high voltage to enable, pull it down to disable the device. Place a $100k\Omega$ resistor in series with EN pin if the source voltage is higher than 5.5V. The input UVLO level can be programmed using a resistor divider from VIN. |

| 3              | FB    | I    | Output Feedback Input Pin. Tap an output feedback resistor divider to this pin.                                                                                                                                                                                                          |

| 4              | RF    | I    | Switching Frequency Setting Pin. The switching frequency can be set by an external resistor connected between RF and GND or RF and VREG.                                                                                                                                                 |

| 5              | MODE  | I    | Set Pin for Selection of FPWM mode or Power Saving Mode (PSM). For FPWM mode, place a resistor from this pin to PGOOD. For PSM, place a resistor from this pin to GND. The soft-start time varies when choosing different resistor.                                                      |

| 6              | VDD   | I    | 4.5V to 25V Power Supply Input Pin. Place a decoupling ceramic capacitor between this pin and PGND.                                                                                                                                                                                      |

| 7              | GND   | G    | Analog Ground. Reference for internal analog signals and logic. Connect it to system ground.                                                                                                                                                                                             |

| 8              | PGND  | G    | Power Ground. Connect it to system ground, exposed pad and GND together.                                                                                                                                                                                                                 |

| 9              | VREG  | 0    | Internal Bias Supply Rail. Decouple this pin to PGND with a ceramic capacitor.                                                                                                                                                                                                           |

| 10             | VDRV  | Ι    | Gate Drive Supply Voltage Input. Connect it to VREG if using LDO output as gate drive supply.                                                                                                                                                                                            |

| 11             | DRVL  | 0    | Gate Driving Output for the Low-side MOSFET (the External Synchronous N-MOSFET).                                                                                                                                                                                                         |

| 12             | SW    | I    | Switching Node. Connect it to the switching node of the converter and act as the return of bootstrap supply, and provide a path for the high-side MOSFET high bootstrapping currents.                                                                                                    |

| 13             | DRVH  | 0    | Gate Driving Output for the High-side MOSFET. Drive the high-side N-MOSFET. The DRVH is powered from the bootstrap (BOOT) capacitor (returned to SW) that is a floating supply.                                                                                                          |

| 14             | BOOT  | I    | Bootstrap Input. Bootstrap supply for high-side driver. Connect a 100nF ceramic capacitor between BOOT and SW pins.                                                                                                                                                                      |

| 15             | NC    | -    | No Connection.                                                                                                                                                                                                                                                                           |

| 16             | PGOOD | 0    | Open-Drain Power Good Flag Output. Connect it to suitable voltage supply through a $10k\Omega$ resistor. High = power good, Low = power not good. Flag pulls low when EN = Low.                                                                                                          |

| Exposed<br>Pad | EP    | -    | Thermal Exposed Pad. It is the main thermal relief path of the die connected to the ground plane on the PCB.                                                                                                                                                                             |

NOTE: I = input, O = output, G = ground.

# **ELECTRICAL CHARACTERISTICS**

( $V_{DD}$  = 12V,  $T_{J}$  = -40°C to +85°C, typical values are measured at  $T_{J}$  = +25°C, unless otherwise noted.)

| PARAMETER                                       | SYMBOL                     | CONDITIONS                                                                                                             | MIN   | TYP   | MAX   | UNITS |  |

|-------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Supply Current                                  |                            |                                                                                                                        |       |       |       |       |  |

| VDD Supply Current                              | I <sub>VDD</sub>           | VDD current, no load, V <sub>EN</sub> = 5V, V <sub>FB</sub> = 0.630V, V <sub>TRIP</sub> = 0.5V, T <sub>J</sub> = +25°C |       | 380   | 590   | μA    |  |

| VDD Shutdown Current                            | IVDDSDN                    | VDD current, no load, $V_{EN}$ = 0V, $T_J$ = +25°C                                                                     |       |       | 5     | μA    |  |

| Internal Reference Voltage                      |                            |                                                                                                                        |       |       |       |       |  |

| Foodbook Deference Voltage                      | V                          | T <sub>J</sub> = +25°C                                                                                                 | 597   | 600   | 603   | mV    |  |

| Feedback Reference Voltage                      | V <sub>FB</sub>            | $T_J = -40^{\circ}C$ to $+85^{\circ}C$                                                                                 | 596   | 600   | 604   |       |  |

| Feedback Input Current                          | I <sub>FB</sub>            | V <sub>FB</sub> = 0.630V, T <sub>J</sub> = +25°C                                                                       |       | 0.002 | 0.2   | μA    |  |

| Output Drivers                                  |                            |                                                                                                                        |       |       |       | -     |  |

|                                                 | Р                          | Source, I <sub>DRVH</sub> = -50mA                                                                                      |       | 1.5   | 3     | 0     |  |

| DRVH Resistance                                 | R <sub>DRVH</sub>          | Sink, I <sub>DRVH</sub> = 50mA                                                                                         |       | 0.8   | 1.5   | Ω     |  |

|                                                 | Р                          | Source, I <sub>DRVL</sub> = -50mA                                                                                      |       | 1     | 2     | 0     |  |

| DRVL Resistance                                 | R <sub>DRVL</sub>          | Sink, I <sub>DRVL</sub> = 50mA                                                                                         |       | 0.6   | 1.2   | Ω     |  |

| Dood Time                                       |                            | DRVH-off to DRVL-on                                                                                                    |       | 18    |       | 1     |  |

| Dead Time                                       | t <sub>DEAD</sub>          | DRVL-off to DRVH-on                                                                                                    |       | 22    | ns    |       |  |

| LDO Output                                      |                            |                                                                                                                        |       |       | •     | •     |  |

| LDO Output Voltage                              | V <sub>VREG</sub>          | $0mA \le I_{VREG} \le 50mA$                                                                                            | 4.74  | 5.2   | 5.65  | V     |  |

| LDO Output Current <sup>(1)</sup>               | I <sub>VREG</sub>          | Maximum current allowed from LDO                                                                                       |       |       | 50    | mA    |  |

| LDO Drop Output Voltage                         | V <sub>DO</sub>            | V <sub>DD</sub> = 4.5V, I <sub>VREG</sub> = 50mA                                                                       |       |       | 500   | mV    |  |

| Bootstrap Switch                                | •                          |                                                                                                                        |       |       | •     |       |  |

| Forward Voltage                                 | V <sub>BOOT_F</sub>        | $V_{VREG}$ - $V_{BOOT}$ , $I_F$ = 10mA                                                                                 |       | 0.05  | 0.12  | V     |  |

| BOOT Leakage Current                            | I <sub>BOOT_LK</sub>       | V <sub>BOOT</sub> = 22V, V <sub>SW</sub> = 17V                                                                         |       | 0.01  | 1     | μA    |  |

| Duty and Frequency Control                      | •                          |                                                                                                                        |       |       | •     |       |  |

| Minimum Off-Time                                | $t_{OFF}$ MIN              |                                                                                                                        | 154   | 250   | 342   | ns    |  |

| Minimum On-Time <sup>(1)</sup>                  | t <sub>on_MIN</sub>        | $V_{IN}$ = 25V, $V_{OUT}$ = 0.6V, $R_{RF}$ = 0 $\Omega$ to VREG                                                        |       | 45    |       | ns    |  |

| Soft-Start                                      | 1                          |                                                                                                                        |       | I.    |       |       |  |

|                                                 |                            | $0V \le V_{OUT} \le 95\%$ , $R_{MODE} = 39k\Omega$                                                                     |       | 0.6   |       |       |  |

|                                                 |                            | $0V \le V_{OUT} \le 95\%$ , $R_{MODE} = 100k\Omega$                                                                    |       | 1.2   |       |       |  |

| Internal Soft-Start Time                        | t <sub>ss</sub>            | $0V \le V_{OUT} \le 95\%$ , $R_{MODE} = 200k\Omega$                                                                    |       | 2.4   |       | ms    |  |

|                                                 |                            | $0V \le V_{OUT} \le 95\%$ , $R_{MODE} = 470k\Omega$                                                                    |       |       |       | 1     |  |

| Power Good                                      | 1                          |                                                                                                                        |       | 1     |       |       |  |

| Power Good Threshold, V <sub>OUT</sub> Rising   |                            | PG becomes high, TJ = +25℃                                                                                             | 92    | 96    | 99.8  |       |  |

| Power Good Hysteresis, V <sub>OUT</sub> Falling |                            | PG becomes low, TJ = +25°C                                                                                             | 2     | 4.5   | 7     |       |  |

| Power Good Threshold, V <sub>OUT</sub> Falling  | V <sub>THPG</sub>          | PG becomes high, TJ = +25℃                                                                                             | 106.5 | 110.5 | 114.5 | %     |  |

| Power Good Hysteresis, VOUT Rising              | 1                          | PG becomes low, TJ = +25°C                                                                                             | 3     | 6.5   | 8.5   | 1     |  |

| PG Transistor On-Resistance                     | R <sub>PG</sub>            |                                                                                                                        | 15    | 30    | 50    | Ω     |  |

| PG Delay after Soft-Start                       | t <sub>PG_DEL</sub>        | T <sub>J</sub> = +25°C                                                                                                 | 0.6   | 1     | 1.3   | ms    |  |

| Logic Threshold and Setting Condition           |                            |                                                                                                                        |       |       |       |       |  |

| EN Input Level Required to Start<br>Switching   | $V_{\text{EN}_{\text{H}}}$ |                                                                                                                        | 1.1   | 1.2   | 1.3   | v     |  |

| EN Input Level Required to Stop<br>Switching    | V <sub>EN_L</sub>          |                                                                                                                        | 1     | 1.1   | 1.2   | v     |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{DD}$  = 12V,  $T_J$  = -40°C to +85°C, typical values are measured at  $T_J$  = +25°C, unless otherwise noted.)

| PARAMETER                                                          | SYMBOL                 |                                                 | CONDITIONS                       | MIN  | TYP  | MAX  | UNITS  |

|--------------------------------------------------------------------|------------------------|-------------------------------------------------|----------------------------------|------|------|------|--------|

| EN Input Level Required to Turn on<br>Internal LDO                 | V <sub>EN-VREG_H</sub> |                                                 |                                  | 0.7  | 0.85 | 1    | V      |

| EN Input Level Required to Turn off<br>Internal LDO                | V <sub>EN-VREG_L</sub> |                                                 |                                  | 0.6  | 0.75 | 0.9  | V      |

| EN Input Current                                                   | I <sub>EN</sub>        | $V_{EN} = 5V$                                   |                                  |      |      | 1    | μA     |

|                                                                    |                        |                                                 | $R_{RF} = 0\Omega$ to GND        | 230  | 280  | 330  |        |

|                                                                    |                        |                                                 | $R_{RF}$ = 187k $\Omega$ to GND  | 280  | 330  | 380  | 1      |

|                                                                    |                        |                                                 | $R_{RF} = 619k\Omega$ to GND     | 370  | 420  | 470  | 1      |

| $\mathbf{O}_{\mathbf{r}}$ it to be a $\mathbf{F}_{\mathbf{r}}$ (2) | £                      | T 0500                                          | R <sub>RF</sub> = Open           | 450  | 500  | 550  | 1      |

| Switching Frequency <sup>(2)</sup>                                 | f <sub>sw</sub>        | T <sub>J</sub> = +25°C                          | $R_{RF}$ = 866k $\Omega$ to VREG | 540  | 650  | 760  | - kHz  |

|                                                                    |                        |                                                 | $R_{RF}$ = 309k $\Omega$ to VREG | 580  | 720  | 860  | 1      |

|                                                                    |                        |                                                 | $R_{RF}$ = 124k $\Omega$ to VREG | 620  | 800  | 980  | 1      |

|                                                                    |                        |                                                 | $R_{RF} = 0\Omega$ to VREG       | 655  | 875  | 1095 | 1      |

| V <sub>o</sub> Discharge                                           |                        |                                                 |                                  |      |      |      | -      |

| V <sub>0</sub> Discharge Current                                   | IDISCHG                | $V_{EN}$ = 0V, $V_{SW}$                         | = 0.5V, V <sub>VREG</sub> = 5V   | 8    | 13.4 |      | mA     |

| Protection: Current Sense                                          | •                      |                                                 |                                  |      | •    |      | -      |

| TRIP Source Current                                                | I <sub>TRIP</sub>      | $V_{\text{TRIP}}$ = 1V, $T_{\text{J}}$          | = +25°C                          | 9    | 10   | 11   | μA     |

| TRIP Current Temp. Coef. (1)                                       | TCITRIP                | T <sub>J</sub> = +25°C                          |                                  |      | 4700 |      | ppm/°C |

| Current Limit Threshold Setting Range                              | V <sub>TRIP</sub>      | V <sub>TRIP</sub> - GND voltage                 |                                  | 0.2  |      | 3    | V      |

| Current Limit Threshold                                            | V <sub>OCL</sub>       | V <sub>TRIP</sub> = 3V                          |                                  | 300  | 360  | 420  | mV     |

|                                                                    |                        | V <sub>TRIP</sub> = 1.6V                        |                                  | 160  | 195  | 230  |        |

|                                                                    |                        | V <sub>TRIP</sub> = 0.2V                        |                                  | 17   | 25   | 33   |        |

|                                                                    |                        | V <sub>TRIP</sub> = 3V                          | V <sub>TRIP</sub> = 3V           |      | -360 | -300 | mV     |

| Negative Current Limit Threshold                                   | V <sub>OCLN</sub>      | V <sub>TRIP</sub> = 1.6V                        |                                  | -230 | -195 | -160 |        |

|                                                                    |                        | V <sub>TRIP</sub> = 0.2V                        |                                  | -42  | -25  | -7   |        |

|                                                                    |                        | Positive, T <sub>J</sub> = +25°C                |                                  | 1.5  | 6.5  |      |        |

| Auto Zero Cross Adjustable Range                                   | V <sub>AZC_ADJ</sub>   | Negative, T <sub>J</sub> =                      | +25°C                            |      | -6.5 | -1.5 | mV     |

| Protection: UVP and OVP                                            | •                      |                                                 |                                  |      | •    | •    | -      |

| OVP Trip Threshold Voltage                                         | V <sub>OVP</sub>       | OVP detect                                      |                                  | 115  | 121  | 127  | %      |

| OVP Propagation Delay Time <sup>(1)</sup>                          | t <sub>OVP_DEL</sub>   | FB delay with                                   | 50mV overdrive                   |      | 1    |      | μs     |

| Output UVP Trip Threshold Voltage                                  | V <sub>UVP</sub>       | UVP detect                                      |                                  | 65   | 70   | 75   | %      |

| Output UVP Propagation Delay Time                                  | t <sub>UVP_DEL</sub>   | T <sub>J</sub> = +25°C                          |                                  | 0.6  | 1    | 1.3  | ms     |

| Output UVP Enable Delay Time                                       | t <sub>UVP_EN</sub>    | From EN to UVP workable, $R_{MODE} = 39k\Omega$ |                                  | 1.5  | 2.6  | 3.7  | ms     |

| UVLO                                                               | •                      |                                                 |                                  |      | •    | •    | -      |

|                                                                    | N                      | Wake up<br>Hysteresis                           |                                  | 3.65 | 4.1  | 4.5  | - V    |

| VREG UVLO Threshold                                                | VUVVREG                |                                                 |                                  |      | 0.2  |      |        |

| Thermal Shutdown                                                   |                        |                                                 |                                  | •    |      |      | •      |

| The model Objected as an Theorem to a lot (1)                      | Ŧ                      | Shutdown tem                                    | perature                         |      | 140  |      |        |

| Thermal Shutdown Threshold <sup>(1)</sup>                          | T <sub>SDN</sub>       | Hysteresis                                      |                                  |      | 10   |      | °C     |

#### NOTES:

1. Ensured by design. Not production tested.

2. Not production tested. Test conditions are  $V_{IN}$  = 12V,  $V_{OUT}$  = 1.35V,  $I_{OUT}$  = 10A and using the application circuit.

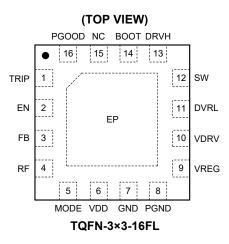

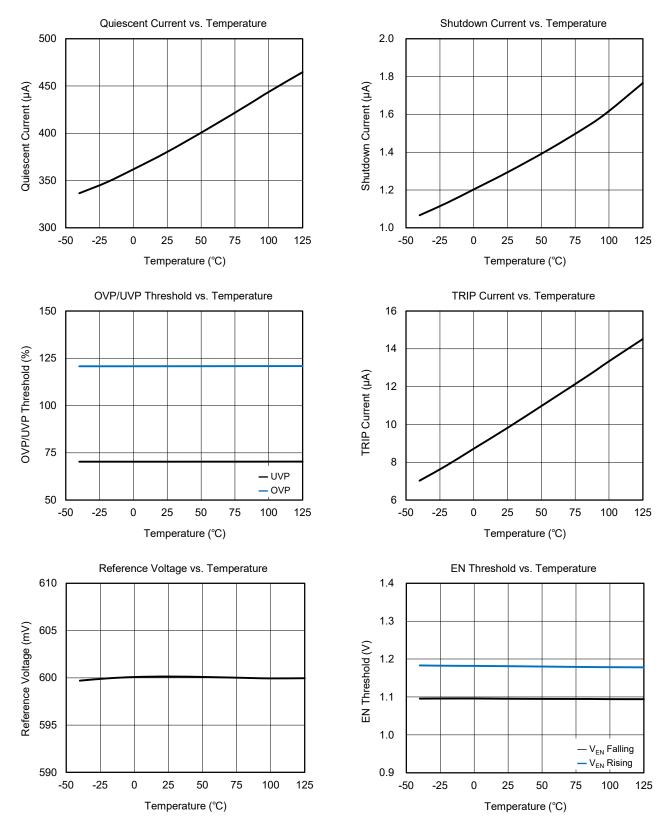

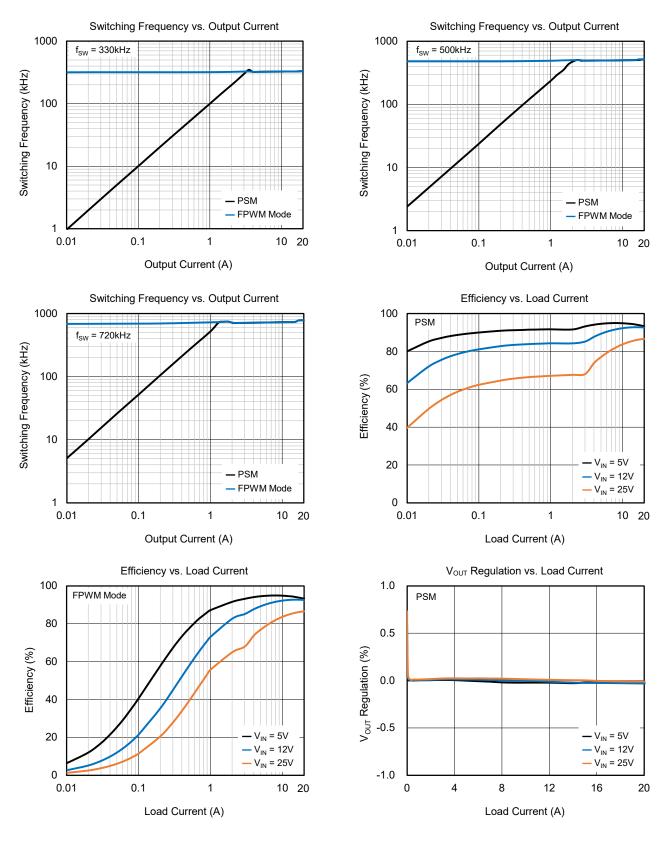

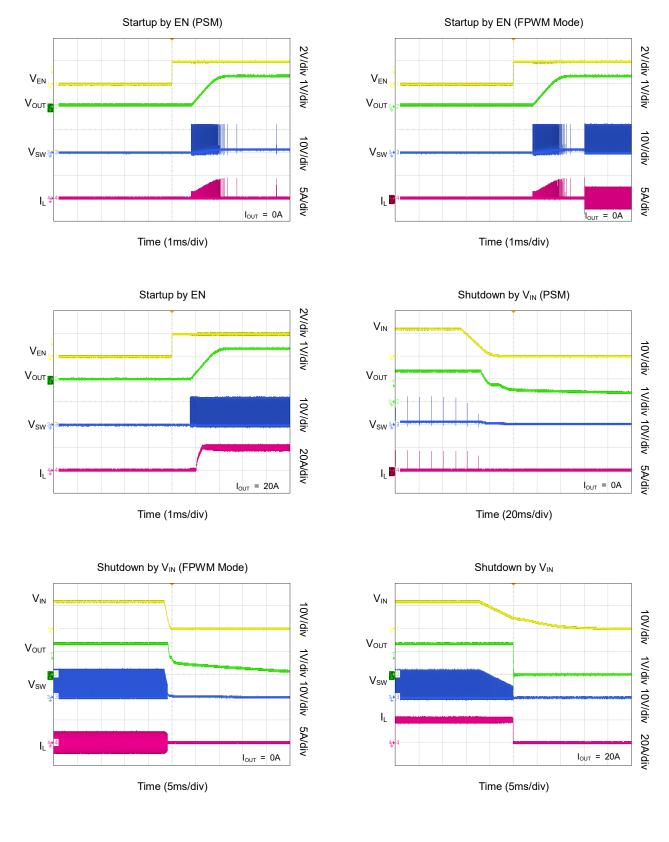

### **TYPICAL PERFORMANCE CHARACTERISTICS**

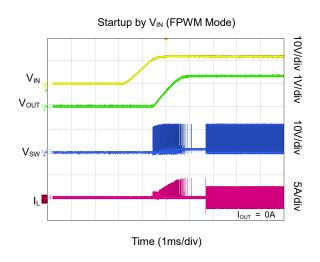

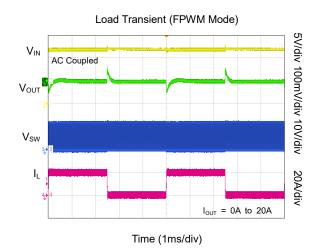

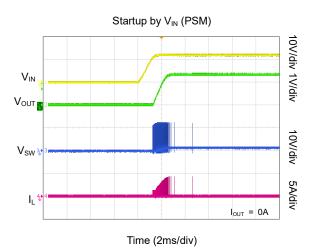

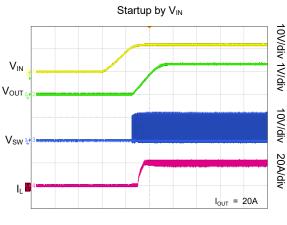

$T_A$  = +25°C,  $V_{IN}$  = 12V,  $V_{OUT}$  = 1.35V,  $f_{SW}$  = 500kHz , L = 0.44µH and  $C_{OUT}$  = 100µF × 4, unless otherwise noted.

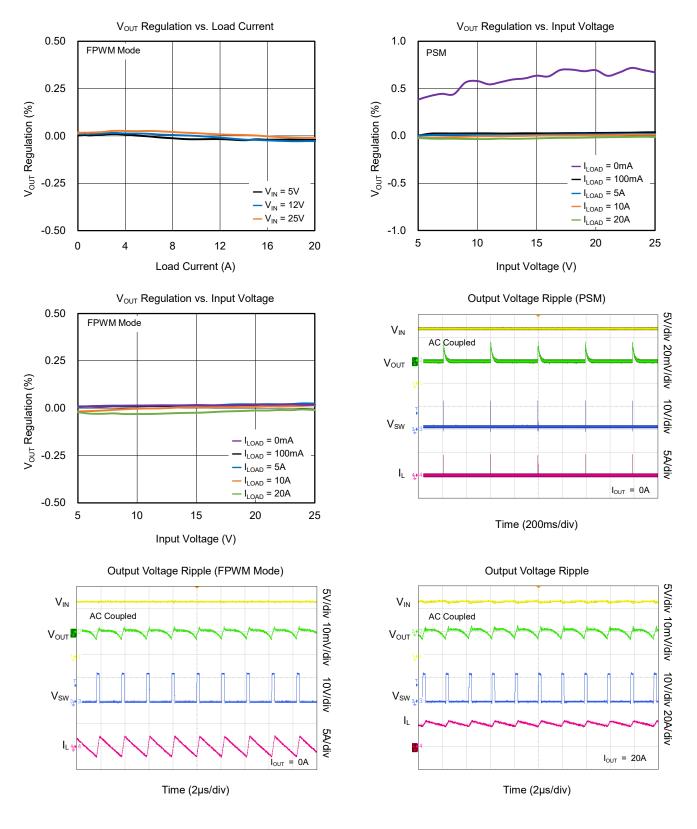

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25^{\circ}C$ ,  $V_{IN} = 12V$ ,  $V_{OUT} = 1.35V$ ,  $f_{SW} = 500$ kHz ,  $L = 0.44\mu$ H and  $C_{OUT} = 100\mu$ F × 4, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25^{\circ}C$ ,  $V_{IN} = 12V$ ,  $V_{OUT} = 1.35V$ ,  $f_{SW} = 500$ kHz , L = 0.44µH and  $C_{OUT} = 100$ µF × 4, unless otherwise noted.

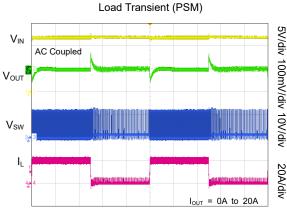

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_{A} = +25^{\circ}C, V_{IN} = 12V, V_{OUT} = 1.35V, f_{SW} = 500kHz , L = 0.44\mu H and C_{OUT} = 100\mu F \times 4, unless otherwise noted.$

Time (1ms/div)

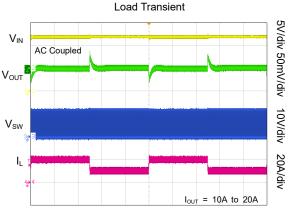

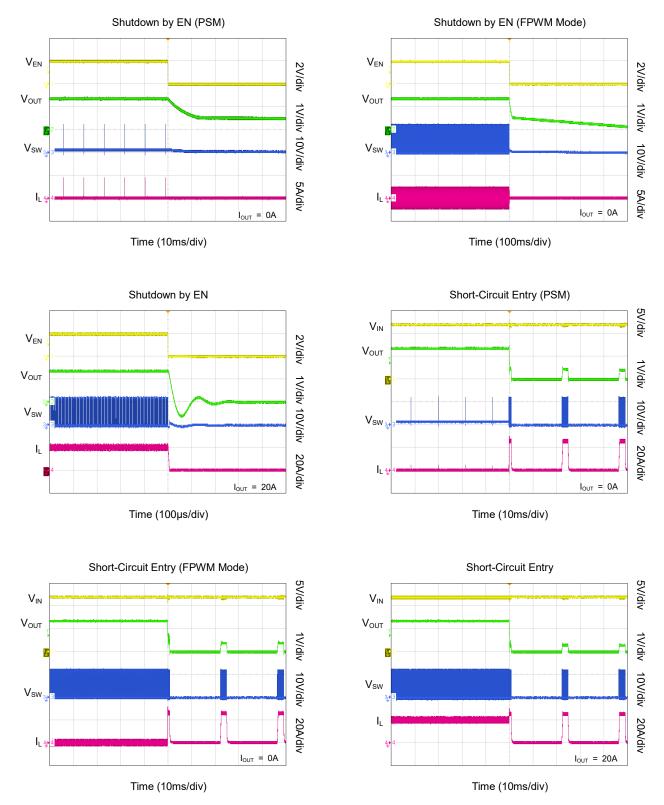

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_{A} = +25^{\circ}C, V_{IN} = 12V, V_{OUT} = 1.35V, f_{SW} = 500kHz , L = 0.44\mu H and C_{OUT} = 100\mu F \times 4, unless otherwise noted.$

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_{A} = +25^{\circ}C, V_{IN} = 12V, V_{OUT} = 1.35V, f_{SW} = 500kHz , L = 0.44\mu H and C_{OUT} = 100\mu F \times 4, unless otherwise noted.$

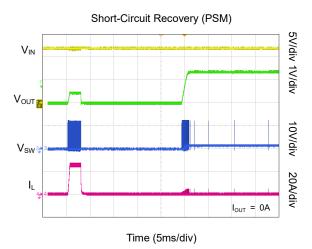

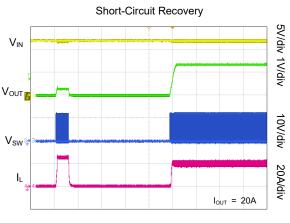

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_{A} = +25^{\circ}C, V_{IN} = 12V, V_{OUT} = 1.35V, f_{SW} = 500kHz , L = 0.44\mu H and C_{OUT} = 100\mu F \times 4, unless otherwise noted.$

Time (5ms/div)

Time (5ms/div)

### **3V to 26V Input, ACOT Synchronous Buck Controller**

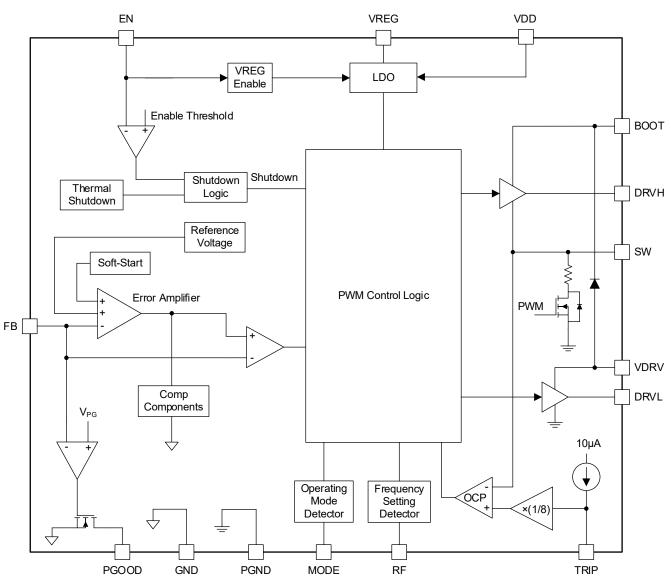

### FUNCTIONAL BLOCK DIAGRAM

Figure 2. Block Diagram

### DETAILED DESCRIPTION

#### **Overview**

The SGM64201 is a 4.5V to 25V wide input controller with adaptive constant on-time (ACOT) control for synchronous Buck converters. The SGM64201 can provide adjustable output voltage in range of 0.6V to 5.5V. It is capable to driver external N-MOSFET efficiently with the conversion input voltage from 3V to 26V.

Eight preset switching frequency values from 280kHz to 875kHz can be selected through a resistor connected from the RF pin to ground or RF pin to VREG. The switching frequency is determined before soft-start and ACOT control can dynamically adjust the on-time duration based on the input and output voltage, achieving a relatively constant frequency during steady-state operation.

The SGM64201 features a MODE pin. At light load. power saving mode (PSM) can be selected to improve the efficiency by connecting a resistor from MODE pin to ground, or forced pulse width modulation (FPWM) mode can be selected to decrease the output ripple by connecting a resistor from MODE pin to a voltage higher than 1.3V. SGMICRO recommends to connect the MODE pin to the PGOOD pin if FPWM mode is desired. Additionally, the MODE pin facilitates the selection of four preset soft time between 0.6ms, 1.2ms, 2.4ms and 4.8ms when using different resistor.

Cycle-by-cycle over-current limiting control is integrated in SGM64201, and over-current threshold is configured using a resistor connect from TRIP pin to ground.

#### **UVLO Protection**

The under-voltage lockout protection (UVLO) is necessary to avoid device malfunction due to insufficient supply voltage. The SGM64201 incorporates VREG UVLO as a safety mechanism. Whenever the VREG voltage drops below 3.9V, the device automatically shuts down to prevent damage. Conversely, when the VREG voltage exceeds 4.1V, a new startup sequence begins seamlessly.

#### Enable and Soft-Start

The EN pin can be used to turn the device on and off or to change the UVLO thresholds. The device is enabled if the EN pin voltage exceeds the enable threshold and VREG exceeds 4.1V. The device is disabled if the EN voltage is externally pulled low or the VREG pin voltage falls below 3.9V. The EN pin cannot be left floating and can be connected to  $V_{\mbox{\scriptsize IN}}$  to enable the device. A resistor large than  $100k\Omega$  is needed if EN voltage is higher than 5.5V.

The startup sequence initiates when the voltage of EN pin rises above the enable threshold voltage. The internal LDO regulator startup after a deglitch time and regulates VREG to 4.6V first. After VREG is ready, the controller then uses the next calibrate time to determine the operation mode, soft-start (SS) time through resistor attached to the MODE pin and switching frequency through resistor attached to the RF pin. This information is encoded in internal registers, remaining unchanged until a new startup sequence begins.

During the second phase, an internal ramp voltage begins to rise from 0V to 0.6V with a ramp time varies from 0.6ms to 4.8ms, depending on the MODE pin resistor. The soft-start is needed to avoid high inrush currents caused by rapid increase of output voltage across output capacitors and the load.

| Table 1. Soft-Start and MODE |                              |                         |                           |  |  |  |

|------------------------------|------------------------------|-------------------------|---------------------------|--|--|--|

| Mode<br>Selection            | Action                       | Soft-Start Time<br>(ms) | R <sub>MODE</sub><br>(kΩ) |  |  |  |

|                              |                              | 0.6                     | 39                        |  |  |  |

| PSM                          | Pull MODE pin<br>down to GND | 1.2                     | 100                       |  |  |  |

| PSM                          |                              | 2.4                     | 200                       |  |  |  |

|                              |                              | 4.8                     | 470                       |  |  |  |

| FPWM                         |                              | 0.6                     | 39                        |  |  |  |

|                              | Connect MODE<br>pin to PGOOD | 1.2                     | 100                       |  |  |  |

|                              |                              | 2.4                     | 200                       |  |  |  |

|                              |                              | 4.8                     | 470                       |  |  |  |

Table 1 Soft Start

#### Adaptive Constant On-Time Control and **Frequency Selection**

The adaptive constant on-time (ACOT) control differs from voltage mode control (VMC) or current mode control (CMC) in that it operates without clock signal and instead uses hysteretic mode control. At the start of each switching cycle, the ACOT control generates a relatively constant on-time pulse when the internal comparator detects that the output voltage has dropped below the desired level. The feedback (FB) pin senses the output voltage through a resistor divider and compares it to the internal reference voltage ( $V_{RFF}$ ) using an error amplifier. The amplifier output is then sent to a comparator.

## **DETAILED DESCRIPTION (continued)**

When the feedback voltage (V<sub>FB</sub>) falls below the amplifier output, the on-time control logic is triggered which turns on the high-side MOSFET. ACOT control can dynamically adjust the on-time duration based on the input and output voltage ( $t_{on} \propto V_{OUT}/V_{IN}$ ), achieving a relatively constant frequency during steady-state operation over a wide input voltage range.

Eight preset switching frequency range of 280kHz to 875kHz is programmed by a resistor connected between the RF pin and GND or VREG pin. Please refer to Table 2. The switching frequency is default 500kHz if the RF pin is left open.

| Resistor (R <sub>RF</sub> ) Connections | Switching Frequency (kHz) |

|-----------------------------------------|---------------------------|

| 0Ω to GND                               | 280                       |

| 187kΩ to GND                            | 330                       |

| 619kΩ to GND                            | 420                       |

| Open                                    | 500                       |

| 866kΩ to VREG                           | 650                       |

| 309kΩ to VREG                           | 720                       |

| 124kΩ to VREG                           | 800                       |

| 0Ω to VREG                              | 875                       |

#### Table 2. Resistor and Switching Frequency

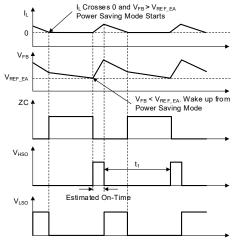

# Light Load Condition with Power Saving Mode (PSM)

SGM64201 operates in power saving mode (PSM) with light loads when the MODE pin is pulled low through  $R_{MODE}$  in which internal power dissipation is significantly reduced. Moreover, the operating frequency starts to drop depending on the load.

The details are explained in Figure 3 that shows the timings of the ACOT control in discontinuous conduction mode (DCM). Inductor current ( $I_L$ ) is monitored with a zero-crossing detector and when  $I_L$  crosses the zero and  $V_{FB} > V_{REF\_EA}$  (the output of the error amplifier), both high-side and low-side MOSFETs are turned off. They will not turn on again until the  $V_{FB}$  falls below  $V_{REF\_EA}$  and triggers a new on-time pulse. During this off-time period, the load is supplied by the output capacitor stored energy.

#### Light Load Condition with Forced Pulse Width Modulation (FPWM) Mode

The SGM64201 is locked in continuous current mode from full load to no load when the MODE pin is pulled high to PGOOD through a resistor. Negative inductor currents are allowed at light load to keep continuous inductor current operation. It is a tradeoff that sacrifices light load efficiency in order to keep switching frequency relatively fixed, achieve lower output ripple, and ensure better output regulation.

#### **Ramp Signal**

The SGM64201 enhances jitter performance by incorporating a ramp signal into  $V_{REF}$ . According to the ACOT, the feedback voltage ( $V_{FB}$ ) is continuously compared with the output of error amplifier, ensuring that the output voltage remains regulated. By incorporating a slight ramp signal into the reference, the relative slope rate of  $V_{FB}$  is significantly improved, thereby reducing jitter and promoting operational stability.

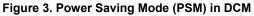

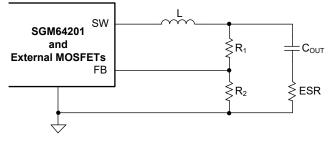

#### **Output Voltage Programming**

The output voltage is set by a resistor divider between  $V_{OUT}$  and GND that is tapped to the FB pin. It is recommended to use 1% or higher quality resistors with low thermal tolerance for an accurate and thermally stable output voltage.

Use Equation 1 to calculate the output voltage. Lower divider resistor values increase loss and reduce light load efficiency. Consider larger resistors to improve efficiency at light load. Note that if  $R_1$  is too high (> 1M $\Omega$ ), the FB pin leakage current and other noises can easily affect the accuracy and performance of the regulator.

$$V_{\text{OUT}} = V_{\text{REF}} \times \left(\frac{R_1 + R_2}{R_2}\right)$$

(1)

### **DETAILED DESCRIPTION (continued)**

Figure 4. Adjustable Output Voltage

#### **Adaptive Zero Crossing Detection**

The SGM64201 features an adaptive zero-crossing circuit that optimizes the detection of zero inductor current during PSM operation at light load.

Based on the voltage of switching node when the low-side MOSFET is turned off, the threshold current for the zero-crossing circuit detection in the next cycle is adaptively adjusted to achieve the ideal turn off time for the low-side MOSFET, resulting in higher light load efficiency and better electromagnetic interference (EMI) performance.

#### **Output Discharge Control**

When EN is low, the SGM64201 utilizes an internal MOSFET connected between the SW pin and the PGND pin to discharge the output capacitor stored energy, while ensuring that both the high-side and low-side MOSFETs remain in the OFF state. The typical discharge resistance is  $40\Omega$ . The internal MOSFET turns off and the discharge function is disabled once VREG becomes low.

#### **Floating Driver and Bootstrap Charging**

The low-side driver is specifically crafted to efficiently power high-current, low on-resistance N-channel MOSFET. The driving voltage VDRV can be supplied either from 5.2V VREG power source or an external source ranging from 4.5V to 6V.

The high-side driver is specifically crafted to efficiently power high-current, low on-resistance N-channel MOSFET. To power the high-side MOSFET gate driver, a voltage higher than  $V_{IN}$  is needed. Bootstrap technique is used to provide this voltage from the switching node by using a  $0.1\mu$ F bootstrap capacitor ( $C_{BOOT}$ ) between SW and BOOT pins along with an internal bootstrap diode. An X5R or X7R ceramic capacitor is recommended for  $C_{BOOT}$  to have stable capacitance against temperature and voltage variations.

$C_{\text{BOOT}}$  is normally charged by VDRV when the high-side MOSFET turns off.

#### **Power Good**

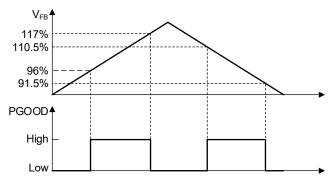

The SGM64201 features a power-good (PG) pin that indicates whether the output voltage is at the desired level. This pin is an open-drain output that requires a resistor of  $10k\Omega$  pulled up to a DC voltage. Figure 5 illustrates that when the FB voltage is within the power-good range, the PG switch is turned off, and the PG pin is pulled up to high after 1ms internal delay. Conversely, when the FB voltage is outside the power-good range, the PG switch is turned on, and the PG pin is pulled down to low after 2µs internal delay. When EN is pulled low, the flag output will also be forced low.

Figure 5. Power-Good Flag

#### **Current Sense and Over-Current Protection**

The SGM64201 supports overload mode. When the output current continues overload while the system is powered up, the SGM64201 exports the maximum power and limits the maximum valley current of the low-side MOSFET. The device keeps in cycle-by-cycle limit to meet the system's power request. The SGM64201 does not shut down until the device heats and then goes to thermal shutdown. As the load increases continuously, the output voltage decreases. If the FB pin voltage drops to 70% of V<sub>REF</sub> for 1ms delay, the hiccup current-protection mode will be activated. In hiccup mode, the regulator is shut down and kept off for 16ms (with 0.6ms soft-start configuration) typically before the SGM64201 tries to start again. If over-current or a short-circuit fault condition still exists. the hiccup mode will repeat until the fault condition is removed. Hiccup mode can help to reduce power dissipation and prevent overheating and potential damage to the device.

# **DETAILED DESCRIPTION (continued)**

The over-current threshold can be adjusted by the voltage of TRIP pin.  $V_{TRIP}$  is programmed by a resistor  $R_{TRIP}$  connected from TRIP pin to GND. The  $V_{TRIP}$  can be calculated from Equation 2:

$$V_{\text{TRIP}}\left(mV\right) = R_{\text{TRIP}}\left(k\Omega\right) \times I_{\text{TRIP}}\left(\mu A\right)$$

(2)

Where:

$I_{TRIP}$  is 10µA typically at room temperature.

$V_{\text{TRIP}}$  sets the valley level of the inductor current. Use Equation 3 to calculate the over-current threshold.

$$I_{OCP} = \frac{V_{TRIP}}{8 \times R_{DSON\_LS}} + \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times L \times V_{IN} \times f_{SW}}$$

(3)

Where:

$\mathsf{R}_{\mathsf{DSON\_LS}}$  is low-side MOSFET on-resistance at room temperature.

When FPWM is chosen, to avoid fatal negative current in the low-side MOSFET, the negative current limit (NCL) is limited as the same absolute value as positive  $I_{OCP}$ , but with a negative polarity.

#### **Under-Voltage and Over-Voltage Protection**

The output voltage is monitored through FB pin voltage. If soft-start is ready and the FB voltage drops to 70% of  $V_{REF}$ , hiccup current-protection mode is activated after 1ms UVP delay. In hiccup mode, the regulator is shut down and kept off for 16ms (with 0.6ms soft-start configuration) typically before the SGM64201 tries to start again.

An over-voltage protection is included in the device to minimize the output voltage overshoots that may occur after recovery from an output fault or a large unloading transient. The FB pin voltage is compared with the OVP thresholds. If the V<sub>FB</sub> exceeds 121% of the V<sub>REF</sub>, the high-side MOSFET driver is forced to turn off, and the low-side MOSFET driver is turned on until negative current limit is triggered. The output voltage decreases. The device enters hiccup mode and high-side and low-side MOSFETs driver will be OFF if FB voltage drops to 70% of V<sub>REF</sub>.

#### **Thermal Shutdown**

The SGM64201 monitors junction temperature and will stop switching if it becomes too high. If the junction temperature exceeds +140 °C (TYP), the device is forced to stop switching. It will recover automatically

when  $T_J$  the junction temperature decreases by approximately 10°C.

#### **Ripple Injection**

The SGM64201 is an ACOT control device in which the PWM timing is based on the output voltage ripple feedback to the FB pin. As explained before, every time the V<sub>FB</sub> voltage falls below the amplifier output voltage, the high-side MOSFET is turned on and the inductor current starts to rise. High-side MOSFET is kept on for a constant on-time. At the end of on-time, the high-side MOSFET is turned off and after a very short dead-time, the low-side MOSFET is turned on (off-time) and current in the inductor starts to decrease. The next on-time and current rise in the inductor start when the V<sub>FB</sub> falls below the amplifier output voltage threshold again. Therefore, in ACOT control the ripple initiates each cycle and there is no clock signal for switching.

The required V<sub>FB</sub> peak-to-peak ripple range for stable PWM operation is at least 20mV. At high output voltage applications (typically V<sub>OUT</sub> > 5V), the natural output ripple is usually large enough for proper PWM operation because the output filter is usually designed such that the output ripple magnitude is roughly 1% to 2% of the output voltage. However, in some design conditions like low output voltage applications, such as a 1V, the output voltage ripple is usually low (e.g. 10mV) and it will not be possible to get enough in phase ripple on the FB pin without a new strategy.

In fact, the ripple feedback is even lower than output ripple due to the voltage divider. If the FB ripple is small, the internal amplifier and comparator are not able to sense that and the control will be lost. In such condition, the output voltage is either not regulated or has large ripple due to missing or wrong multiple pulses. With the low ESR output capacitors such as ceramic ones, the ripple is also small. Therefore ripple injection methods are proposed for low output ripple applications to avoid instability.

Remember that naturally, the output ripple ( $\Delta V_{OUT}$ ) has two main components. One is in phase with inductor ripple and is produced by the inductor AC current going through the output capacitors ( $V_{rr} = ESR \times \Delta I_L$ ), and the other one that has a lag phase is due to the charge and discharge of capacitor by  $\Delta I_L$  current in each cycle (estimated by  $V_{cr} \approx \Delta I_L/8f_{SW}C_{OUT}$ ).

# **DETAILED DESCRIPTION (continued)**

The output capacitor  $C_{OUT}$  is usually designed large enough to filter switching ripples such that  $\Delta V_{OUT}$  and output peak transients in response to load changes, remain within the acceptable range in the application. Too large output capacitor may result in startup issues.

Three main cases can be classified based on the amount of peak-to-peak feedback ripple ( $\Delta V_{FB}$ ) and the ripple injection technique used for ACOT converters.

**Case 1**: If the output capacitor has large ESR, the output ripple at the FB pin is mainly due to the ESR that carries the inductor current ripple (see Figure 6). If the output voltage is small ( $R_2$  is large compared to  $R_1$ ) the ripples seen by FB pin are large enough and with proper phase. In this case converter has a stable operation without any ripple injection. The stability criterion is:

$$\mathsf{ESR} \times \mathsf{C}_{\mathsf{OUT}} > \frac{\mathsf{t}_{\mathsf{ON}}}{2} \tag{4}$$

The feedback voltage ripple is given by Equation 5:

$$\Delta V_{FB} \approx \frac{R_2}{R_1 + R_2} \times ESR \times \Delta I_L$$

(5)

where:

$\Delta I_L$  = peak-to-peak value of the inductor current ripple.

#### Figure 6. Feedback Circuit when Enough Ripple at FB Pin

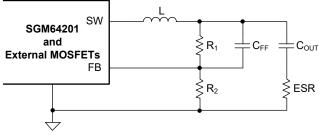

**Case 2**: In this case, the in-phase ripple of the output is large enough, but it is weakened by the resistor divider. As shown in Figure 7, a small feed-forward capacitor  $(C_{FF})$ , across the upper resistor  $(R_1)$  bypasses the resistor divider at the ripple frequency  $(f_{SW})$  and the ripple seen on the FB pin is essentially the same as the output voltage ripple (not weakened by the divider). The other advantage of using  $C_{FF}$  is the improvement of the converter transient response, because feeding back the actual over/under-voltage transients of the output with no weakening helps a quicker reaction and faster response to transients. In fact, it is sometimes used for applications like Case 1 for better transient

response. However, the drawback of  $C_{FF}$  is that it may worsen the regulation of the converter output. The time constant seen by  $C_{FF}$  should be much longer than switching period, and Equation 6 defines the minimum feed-forward capacitance,  $C_{FF}$ .

Figure 7. Use of Feed-Forward Capacitor when Inadequate Ripple at FB Pin

With the feed-forward capacitor, the feedback voltage ripple is very close to the output voltage ripple, giving in Equation 7.

$$C_{FF} > \frac{1}{2 \times \pi \times f_{SW} \times (R_1 || R_2)}$$

(6)

$$\Delta V_{FB} \approx ESR \times \Delta I_{L}$$

(7)

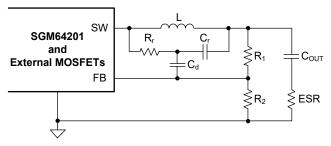

**Case 3**: In modern designs, ceramic capacitors are extensively used due to their small size and good stability. Due to very low ESR of the output capacitors, there is virtually no ripple at the FB pin. This is usually more critical at low output voltage in which lower output ripple is required. Therefore, additional ripple (in phase with inductor current) needs to be injected artificially into the FB pin to keep stable switching. The additional ripple can be injected by only two capacitors and one resistor. The ripple is generated by  $R_r$  and  $C_r$  using DCR of the inductor. And then coupled into the FB pin through  $C_d$ .

Figure 8. Ripple Injection from SW Pin

### **DETAILED DESCRIPTION (continued)**

Note that if too much ripple is injected, the transient response will get worse, because the impact of the actual output variations on the feedback signal is reduced. The key point is that the ripple should be kept as small as possible without losing the stability.

The process of sizing the ripple injection resistor and capacitors in Figure 8 is as follows:

• Select  $R_r$  and  $C_r$ . Set  $R_r$  range from  $10k\Omega$  to  $100k\Omega$  and ensure  $R_rC_r$  satisfies the loop stability condition:

$$\frac{L \times C_{OUT}}{R_r \times C_r} > \frac{t_{ON}}{2}$$

(8)

• Select  $C_d$  to couple the ripples into the FB pin. The impedance of  $C_d$  should be small compared to the feedback divider impedance at the desired switching frequency. The impedance of the feedback network is the parallel combination of  $R_1 || R_2$ . The impedance of  $C_d$

at the switching frequency can be taken to be about one tenth of this value.

$$C_{d} > \frac{10}{2 \times \pi \times f_{sw} \left( R_{1} || R_{2} \right)}$$

(9)

Note that  $C_d$  should be smaller than  $C_r$ , also the selection of capacitance of  $C_d$  will influence the transient response of the converter. The transient is faster and undershoot is smaller if  $C_d$  is small. The transient is slower and undershoot is bigger if  $C_d$  is large.

With the ripple injection network, the feedback voltage ripple is calculated in Equation 10.

$$\Delta V_{FB} = \frac{V_{IN} - V_{OUT}}{R_r C_r} \times t_{ON}$$

(10)

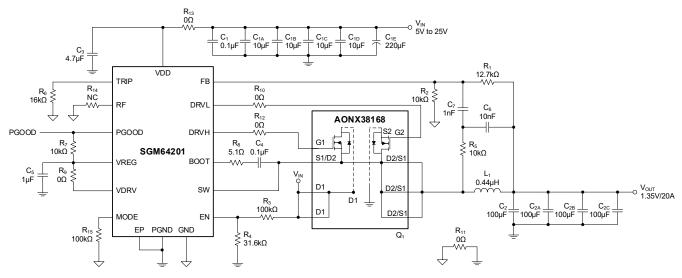

### APPLICATION INFORMATION

Figure 9. Typical Application Circuit Diagram

**Design Requirements**

This section describes the design calculations and device selection for applications with all ceramic output capacitors. Table 3 shows the design objectives.

| Design Parameters                          | Example Values                |

|--------------------------------------------|-------------------------------|

| Input Voltage                              | 12V (TYP), 5V to 25V          |

| Start Input Voltage (Rising $V_{IN}$ )     | 5V                            |

| Output Voltage                             | 1.35V                         |

| Output Voltage Ripple                      | 13.5mV, 1% of $V_{OUT}$ (CCM) |

| Output Current Rating                      | 20A                           |

| Over-Current Threshold                     | 25A                           |

| Transient Response,<br>0A to 20A Load Step | 67.5mV, 5% of $V_{OUT}$       |

| Operation Frequency                        | 500kHz                        |

| Operation Mode                             | PSM                           |

| Soft-Start Time                            | 1.4ms                         |

Table 3. Design Specifications

# Input Capacitor Selection (C<sub>1</sub>, C<sub>1A</sub>, C<sub>1B</sub>, C<sub>1C</sub>, C<sub>1D</sub>, C<sub>1E</sub>)

The input capacitor is necessary to circulate the high frequency ripples and switching currents of the converter and keep them away from the input line and the source. The selected capacitors must have enough RMS current rating to absorb all AC currents on the input. The input capacitors must deliver the RMS current according to:

$$\begin{split} I_{\text{CIN}_{\text{RMS}}} &= I_{\text{OUT}} \times \sqrt{\frac{V_{\text{OUT}}}{V_{\text{IN}}} \times \frac{(V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}}}} \\ &= I_{\text{OUT}} \times \sqrt{D \times (1 - D)} \end{split} \tag{11}$$

Where the duty cycle is  $D = V_{OUT}/V_{IN}$ . For example, at D = 20% duty cycle, the input/output current multiplier is 0.40. Therefore, if the regulator is delivering 20A of steady-state load current, the input capacitor(s) must support an RMS current of 8A (0.40 × 20A).

The input capacitance determines the regulator input voltage ripple. This ripple can be calculated from Equation 12. In this example, a  $220\mu$ F/35V electrolytic capacitor and four  $10\mu$ F/50V ceramic capacitors are used.

$$\Delta V_{IN} = \frac{I_{OUT} \times D \times (1 - D)}{C_{IN} \times f_{SW}}$$

(12)

It recommended placing an additional small size  $0.1 \mu F$  ceramic capacitor right beside  $V_{\rm IN}$  and GND pins for high frequency filtering.

#### Inductor Selection (L<sub>1</sub>)

Equation 13 is conventionally used to calculate the output inductance of a Buck converter. The ratio of inductor current ripple ( $\Delta I_L$ ) to the maximum output current ( $I_{OUT}$ ) is represented as  $K_{IND}$  factor ( $\Delta I_L/I_{OUT}$ ). The inductance is typically selected such that  $K_{IND}$  is between 20% to 40%. The DC current rating of the selected inductor should be at least 25% above the maximum load current. The inductor saturation current must be high enough such that it does not saturate in any normal or transient operating condition.  $\Delta I_L$  can be selected equal to 30% of maximum load current.

### **APPLICATION INFORMATION (continued)**

$$L = \frac{V_{OUT} \times (V_{IN\_MAX} - V_{OUT})}{V_{IN\_MAX} \times I_{OUT} \times K_{IND} \times f_{SW}}$$

(13)

In this example, the calculated inductance will be  $0.43\mu$ H with K<sub>IND</sub> = 0.3, so the nearest inductance of  $0.44\mu$ H is selected.

The maximum inductor peak current and inductor ripple are calculated by Equation 14 and 15:

$$I_{L_{MAX}} = I_{LOAD} + \frac{\Delta I_{L}}{2}$$

(14)

$$\Delta I_{L} = \frac{V_{IN}MAX}{L} + V_{OUT} \times \frac{V_{OUT}}{V_{IN}MAX} \times f_{SW}$$

(15)

# Output Capacitor Selection (C<sub>2</sub>, C<sub>2A</sub>, C<sub>2B</sub>, C<sub>2C</sub>)

The output capacitors and inductor filter the AC part of the PWM switching voltage and provide an acceptable level of output voltage ripple superimposed on the desired output DC voltage. Capacitors also store energy to help maintain of the output voltage regulation during a load transient. The output voltage ripple ( $\Delta V_{OUT}$ ) depends on the output capacitor value at the operating voltage and temperature (°C) and its parasitics (ESR and ESL):

$$\Delta V_{OUT} = \Delta I_{L} \times ESR + \frac{V_{IN} - V_{OUT}}{L} \times ESL + \frac{\Delta I_{L}}{8 \times f_{SW} \times C_{OUT}} (16)$$

The voltage rating of the output capacitors should be selected with enough margins to ensure that capacitance drop (voltage and temperature derating) is not significant. The type of output capacitors will determine which terms of Equation 16 are dominant. For ceramic output capacitors, the ESR and ESL are virtually zero so the output voltage ripple will be dominated by the capacitive term.

$$\Delta V_{\text{OUT}} \approx \frac{\Delta I_{\text{L}}}{8 \times f_{\text{SW}} \times C_{\text{OUT}}}$$

(17)

To reduce the voltage ripple either switching frequency or the total capacitance is increased. Inductance may also be increased to reduce the inductor current ripple. For electrolytic output capacitors, the value of capacitance is relatively high, and the third term in Equation 16 can be ignored compared to the ESR and ESL terms:

$$\Delta V_{OUT} = \Delta I_{L} \times ESR + \frac{V_{IN} - V_{OUT}}{L} \times ESL$$

(18)

Higher quality capacitors, larger inductance or using parallel capacitors can help reduce the output ripple in a design using electrolytic output capacitors. The ESR of some commercial electrolytic capacitors can be quite high, and it is recommended to use quality capacitors with the ESR or the total impedance clearly documented in their datasheet. ESR of an electrolytic capacitor may increase significantly at cold ambient temperatures with a factor of 10 or so, which increases the ripple and can deteriorate the regulator stability.

The design of the output capacitor typically satisfies the typical  $\pm 1\%$  ripple requirement. The appropriate output capacitor value can be selected through calculations based on the capacitor ripple and ESR ripple. However, in scenarios involving low voltage and high current, it is crucial to consider the overshoot and undershoot of the output voltage during load transient. Additionally, with the same output capacitor, the COT control response is faster than voltage mode control or current mode control. Therefore, the design of the output capacitor must always take into account the load transient response. Equation 19 and Equation 20 calculate the minimum capacitor required to keep the output voltage overshoot or undershoot to a desired value.

$$C_{OUT} > \frac{I_{MAX}^{2}}{2 \times V_{OVER}} \left( \frac{L}{V_{OUT}} - \frac{1}{I_{SR_{FALLING}}} \right)$$

(19)

$$C_{\text{OUT}} > \frac{I_{\text{MAX}}^2}{2 \times V_{\text{UNDER}}} \left( \frac{1}{I_{\text{SR}_{eq}}} - \frac{1}{I_{\text{SR}_{R}\text{ISING}}} \right)$$

(20)

Where:

$I_{SR\_FALLING}$  is the load current drop slew rate (5A/µs, TYP) during load transient from full load to no load.

$I_{SR\_RISING}$  is the load current rise slew rate (5A/µs, TYP) during load transient from no load to full load.

$I_{SR\_eq}$  is the equivalent slew rate of inductor current during load transient from no load to full load.

$V_{\text{OVER}}$  is the output overshoot during load transient from full load to no load.

$V_{\text{UNDER}}$  is the output undershoot during load transient from no load to full load.

In this case according to Table 3, 4  $\times$  100 $\mu$ F/10V ceramic capacitors can meet the above conditions.

### **APPLICATION INFORMATION (continued)**

#### **MOSFET Selection (Q<sub>1</sub>)**

Select the AONX38168. The device integrates two MOSFETs at the size of 5mm × 6mm, and flows through 20A. The  $R_{ON}$  of the high-side MOSFET is 3.6m $\Omega$ , and the  $R_{ON}$  of the low-side MOSFET is 0.85m $\Omega$ .

#### VIN UVLO Setting (R<sub>3</sub>, R<sub>4</sub>)

The input UVLO can be programmed by using an external voltage divider on the EN pin of the SGM64201. In this design, R<sub>3</sub> is connected between V<sub>IN</sub> pin and EN pin, and R<sub>4</sub> is connected between EN pin and GND (see Figure 9). The UVLO has two thresholds (hysteresis), one for power-up (turn-on) when the input voltage is rising and one for power-down (turn-off) when the voltage is falling. In this design, the turn-on (enable to start switching) occurs when  $V_{\text{IN}}$  rises above  $V_{\text{UV H}}.$  When the regulator is working, it will not stop switching (disabled) until the input falls below V<sub>UV L</sub>. The enable rising threshold voltage  $V_{EN H}$  is 1.2V (TYP) and enable hysteresis voltage  $V_{\text{EN\_HYS}}$  is 0.1V (TYP). Given  $V_{\text{UV\_H}}$  as 5.0V, select  $R_3$  to be  $100k\Omega$  to minimize input current from the supply, then  $R_4$  and  $V_{\rm UV\ L}$  can be calculated by following equations.

$$V_{UV_{H}} = V_{EN_{H}} \times \frac{R_3 + R_4}{R_4}$$

(21)

$$V_{UV_{L}} = \left(V_{EN_{H}} - V_{EN_{HYS}}\right) \times \frac{R_{3} + R_{4}}{R_{4}}$$

(22)

By Equation 21, R<sub>4</sub> is calculated to be 31.58k $\Omega$ , and a standard value of 31.6k $\Omega$  is selected. Based on the

value of  $R_3$  and  $R_4$ ,  $V_{UV_L}$  can be calculated to be 4.58V according to Equation 22.

#### Output Voltage Setting (R<sub>1</sub>, R<sub>2</sub>)

Use an external resistor divider ( $R_1$  and  $R_2$ ) to set the output voltage using Equation 23:

$$R_{1} = R_{2} \times \frac{V_{OUT} - V_{REF}}{V_{REF}}$$

(23)

where  $V_{REF} = 0.6V$  is the internal reference. For example, by choosing  $R_2 = 10k\Omega$ , the  $R_1$  value for 1.35V output will be calculated as  $12.5k\Omega$ , so the nearest resistance of  $12.7k\Omega$  is selected.

#### **TRIP Resistor Selection (R<sub>6</sub>)**

The over-current threshold of the SGM64201 can be set using a resistor placed between TRIP and GND pins. Equation 24 can be used to calculate the  $R_{TRIP}$  to set the desired over-current threshold.

$$R_{\text{TRIP}} = \frac{8 \times R_{\text{DSON}_{\text{LS}}} \times (I_{\text{OCP}} - \Delta I_{\text{L}}/2)}{I_{\text{TRIP}}}$$

(24)

In this example, the calculated inductance will be 15.5k $\Omega$  with  $I_{OCP}$  = 25A, so the nearest resistance of 16k $\Omega$  is selected.

#### Ripple Injection Selection (C<sub>6</sub>, C<sub>7</sub>, R<sub>5</sub>)

For application with all ceramic output capacitor. Due to very low ESR of the output capacitors, additional ripple needs to be injected artificially into the FB pin to keep stable switching using  $C_r$ ,  $C_d$  and  $R_r$ . In this example, according to Equation 8, Equation 9 and Equation 10,  $C_r$ ,  $C_d$  and  $R_r$  are calculated as 10nF, 1nF, 10k $\Omega$  respectively.

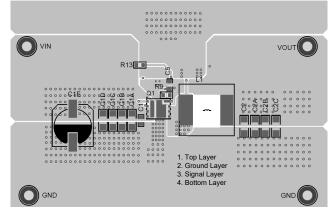

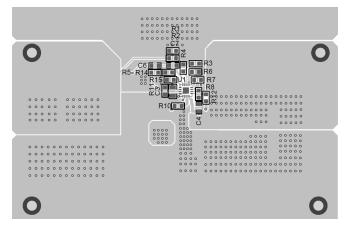

# LAYOUT

#### Layout Guidelines

PCB layout is an important part of the converter design. A weak layout can result in poor performance, resistive losses, EMI issues and instability problems. SGMICRO recommends that the PCB should be designed with at least 4 layers, Figure 10 and Figure 11 only shows the top and bottom layers of the 4-layer board. The following guidelines are helpful for designing a good layout for the SGM64201:

- Place the input capacitors as close as possible to the switches (drain of the high-side MOSFET and the source of the low-side MOSFET) to keep the input AC current loop as small as possible.

- Use small size high frequency decoupling capacitors near input and ground pins.

- Place the inductor pins as close as possible to the switching nodes. Keep the switching node connections short and wide with minimal copper area to minimize capacitive coupling noise and radiation. Keep them away from sensitive traces.

- Keep the BOOT-SW voltage path as short as possible.

- Sensitive signals such as FB, MODE, PGOOD and TRIP should be away from noisy traces and components such as SW node, gate driver and switching side of the inductor body. Place divider resistor as close as possible to the FB and GND pins. Use internal layers as ground planes and shield sensitive signals from noisy traces.

- Place decoupling capacitors on VREG and VDRV as close as possible to those pins.

- Keep the device close to the switch gate pins to minimize gate drive trace lengths. The device can be placed on the opposite side of the PCB. Connect the gates with some parallel vias to minimize gate connection impedance.

- Use separate routes for analog and power grounds.

Use a 0Ω resistor as connection to separate analog and power ground nets in the layout.

- Please connect the frequency setting resistor from the RF pin either to GND or to the PGOOD pin, and make sure that the connections are made as close to the device as possible. Additionally, connect the over-current setting resistors from the TRIP pin to GND, also make sure that the connections are made as close to the device as possible.

- Use large copper areas on all layers and stich them with thermal vias for better heat transfer and dissipation especially for heavy load applications.

#### Layout Example

Figure 10. Layout Example (Top Layer)

Figure 11. Layout Example (Bottom Layer)

### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (DECEMBER 2024) to REV.A  | Page                |

|-------------------------------------------------|---------------------|

| Changed from product preview to production data | All                 |

| SG Micro Corp<br>SGMICRO WWW.Sg-micro.com       | DECEMBER 2024<br>23 |

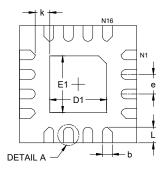

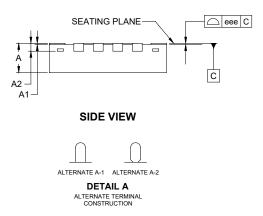

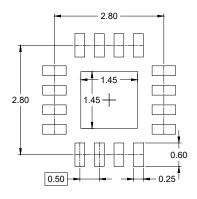

# PACKAGE OUTLINE DIMENSIONS TQFN-3×3-16FL

TOP VIEW

**BOTTOM VIEW**

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dir       | Dimensions In Millimeters |       |  |  |

|--------|-----------|---------------------------|-------|--|--|

|        | MIN       | NOM                       | МАХ   |  |  |

| A      | 0.700     | -                         | 0.800 |  |  |

| A1     | 0.000     | -                         | 0.050 |  |  |

| A2     |           | 0.203 REF                 |       |  |  |

| b      | 0.180     | -                         | 0.300 |  |  |

| D      | 2.900     | -                         | 3.100 |  |  |

| E      | 2.900     | -                         | 3.100 |  |  |

| D1     | 1.300     | -                         | 1.550 |  |  |

| E1     | 1.300     | -                         | 1.550 |  |  |

| е      | 0.500 BSC |                           |       |  |  |

| k      | 0.200     | -                         | -     |  |  |

| L      | 0.300     | -                         | 0.500 |  |  |

| eee    | 0.080     |                           |       |  |  |

NOTE: This drawing is subject to change without notice.

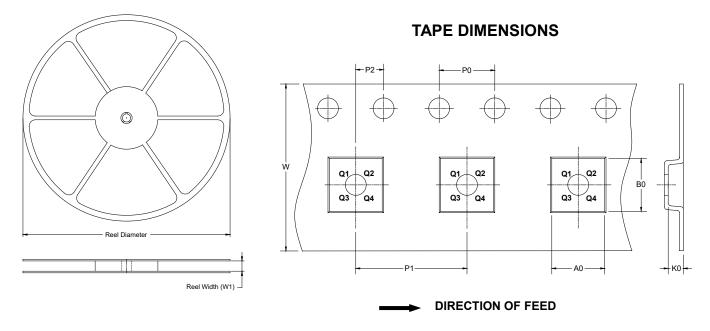

### TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type  | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-3×3-16FL | 13"              | 12.4                     | 3.30       | 3.30       | 1.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q2               |

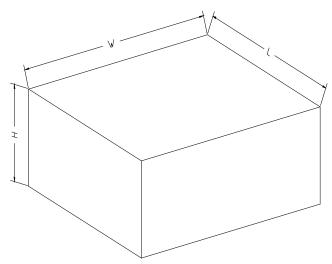

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |