# SGM8196 High Voltage, High-Side Current-Sense Amplifier

## **GENERAL DESCRIPTION**

The SGM8196 is a high voltage, high-side current-sense amplifier that operates from 2.7V to 5.5V single supply. The device also features a wide common mode voltage range from 2.9V to 70V in single-supply operation or  $(-V_s) + 2.9V$  to  $(-V_s) + 70V$  in dual-supply operation. And the input common mode voltage is independent with the power supply voltage.

The SGM8196 is designed to convert the measured small differential voltage across the high-side shunt resistor to the output voltage referred to GND. There are four different gains for SGM8196: 20V/V, 25V/V, 50V/V or 100V/V. The current consumption of the device is only  $320\mu$ A and almost no leakage current flows into the device in standby mode, which minimizes power consumption in applications.

The SGM8196 is available in Green SOIC-8 and TSSOP-8 packages. It is specified over the extended  $-40^{\circ}$ C to  $+125^{\circ}$ C temperature range.

### FEATURES

- Independent Supply and Input Common Mode Voltages

- Wide Common Mode Voltage in Recommended Operating Conditions:

- 2.9V to 70V for Single-Supply Operation

- \*  $(-V_S) + 2.9V$  to  $(-V_S) + 70V$  for Dual-Supply Operation

- Wide Common Mode Voltage in Reversed Battery and Load-Dump Conditions: -75V to 75V

- Supply Voltage Range: 2.7V to 5.5V Single Supply

- Low Supply Current: 320µA (TYP)

- Gain Options: 20V/V, 25V/V, 50V/V or 100V/V

- Output with Buffer

- -40°C to +125°C Operating Temperature Range

- Available in Green SOIC-8 and TSSOP-8 Packages

### **APPLICATIONS**

Current Monitoring Application of Controlling DC Motor Photo-Voltaic Application Battery Charger Precision Current Source Current Monitoring of Laptops Uninterruptible Power Supply High-End Power Supply

### SGM8196

### PACKAGE/ORDERING INFORMATION

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING       | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|--------------------------|---------------------|

| SGM8196  | SOIC-8                 | -40°C to +125°C                   | SGM8196XS8G/TR     | SGM<br>8196XS8<br>XXXXX  | Tape and Reel, 4000 |

| 36100190 | TSSOP-8                | -40°C to +125°C                   | SGM8196XTS8G/TR    | SGM8196<br>XTS8<br>XXXXX | Tape and Reel, 4000 |

### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

- Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

| Differential Voltage of Input Pins (VP - VM), VID±75V                                                 |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Sensing Pins Input Voltages (V <sub>P</sub> , V <sub>M</sub> ) <sup>(1)</sup> , V <sub>IN_SENSE</sub> |  |  |  |  |  |

| -75V to 75V                                                                                           |  |  |  |  |  |

| Voltages Level of Gain-Select Pins (SEL1, SEL2) $^{(2)}$ , V <sub>IN_SEL</sub>                        |  |  |  |  |  |

| -0.3V to (+V <sub>S</sub> ) + 0.3V                                                                    |  |  |  |  |  |

| Positive Supply Voltage $^{(2)},$ +Vs0.3V to 7V                                                       |  |  |  |  |  |

| DC Supply Voltage, (+Vs) - (-Vs)0V to 22V                                                             |  |  |  |  |  |

| DC Output Pin Voltage $^{(2)}$ , V <sub>OUT</sub> 0.3V to $(+V_S) + 0.3V$                             |  |  |  |  |  |

| Package Thermal Resistance                                                                            |  |  |  |  |  |

| SOIC-8, θ <sub>JA</sub> 120°C/W                                                                       |  |  |  |  |  |

| SOIC-8, θ <sub>JB</sub>                                                                               |  |  |  |  |  |

| SOIC-8, θ <sub>JC</sub>                                                                               |  |  |  |  |  |

| TSSOP-8, θ <sub>JA</sub>                                                                              |  |  |  |  |  |

| TSSOP-8, θ <sub>JB</sub> 109.5°C/W                                                                    |  |  |  |  |  |

| TSSOP-8, θ <sub>JC</sub> 55.3°C/W                                                                     |  |  |  |  |  |

| Junction Temperature+150°C                                                                            |  |  |  |  |  |

| Storage Temperature Range65°C to +150°C                                                               |  |  |  |  |  |

| Lead Temperature (Soldering, 10s)+260°C                                                               |  |  |  |  |  |

| ESD Susceptibility                                                                                    |  |  |  |  |  |

| HBM4000V                                                                                              |  |  |  |  |  |

| CDM                                                                                                   |  |  |  |  |  |

|                                                                                                       |  |  |  |  |  |

### **RECOMMENDED OPERATING CONDITIONS**

| Supply Voltage for Single-Supply Operation (-Vs Connected to |              |  |  |  |  |  |

|--------------------------------------------------------------|--------------|--|--|--|--|--|

| GND = 0V), +V <sub>S</sub>                                   | 2.7V to 5.5V |  |  |  |  |  |

| Negative Supply Voltage for Dual-Supply Operation            |              |  |  |  |  |  |

| +Vs = 5.5V (MAX)                                             | 14.5V to 0V  |  |  |  |  |  |

| +V <sub>S</sub> = 2.7V (MAX)                                 | 17.3V to 0V  |  |  |  |  |  |

Common Mode Voltage Range Referred to -Vs Pin

|                                           | J |

|-------------------------------------------|---|

| Operating Temperature Range40°C to +125°C | С |

#### NOTES:

1. These values of voltage are tested relative to the -V<sub>S</sub> pin.

2. These values of voltage are tested relative to the GND pin.

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

### ESD SENSITIVITY CAUTION

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

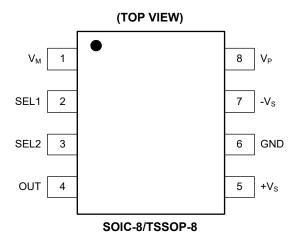

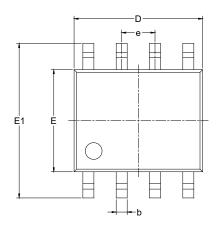

## **PIN CONFIGURATION**

### **PIN DESCRIPTION**

| PIN | NAME | I/O           | FUNCTION                                                                      |  |

|-----|------|---------------|-------------------------------------------------------------------------------|--|

| 1   | VM   | Analog Input  | External Sense Resistor Connection. See Single-Supply<br>Operation Schematic. |  |

| 2   | SEL1 | Digital Input | Gain-Select Pin.                                                              |  |

| 3   | SEL2 | Digital Input | Gain-Select Pin.                                                              |  |

| 4   | OUT  | Analog Output | Output Pin. $V_{OUT}$ is proportional to $V_{SENSE} = V_P - V_M$ .            |  |

| 5   | +Vs  | _             | Positive Power Supply Pin.                                                    |  |

| 6   | GND  | —             | Ground.                                                                       |  |

| 7   | -Vs  | _             | Negative Power Supply Pin.                                                    |  |

| 8   | VP   | Analog Input  | External Sense Resistor Connection. See Single-Supply<br>Operation Schematic. |  |

### **ELECTRICAL CHARACTERISTICS**

$(+V_{S} = 5V, -V_{S} \text{ connected to GND (single-supply operation)}, V_{M} = 12V, V_{SENSE} = V_{P} - V_{M} = 50mV$ , no load on OUT pin, all gain configurations, Full = -40°C to +125°C, typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                               | SYMBOL                                          | CONDITIONS                                                              | TEMP  | MIN  | TYP   | MAX  | UNITS  |  |

|-------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------|-------|------|-------|------|--------|--|

| Input Characteristics                                                   | L                                               |                                                                         | l     |      |       |      |        |  |

| Innut Offeet Veltere (1)                                                | M                                               |                                                                         | +25°C |      | ±15   | ±75  |        |  |

| Input Offset Voltage (1)                                                | Vos                                             |                                                                         | Full  |      |       | ±100 | μV     |  |

| Input Offset Voltage Drift                                              | $\Delta V_{OS} / \Delta T$                      | G = 50V/V                                                               | Full  |      | ±0.05 | ±0.3 | µV/⁰C  |  |

| Input Leakage Current                                                   | I <sub>LK</sub>                                 | V <sub>S</sub> = 0V                                                     | Full  |      |       | 0.5  | μA     |  |

| Input Bias Current                                                      | I <sub>B</sub>                                  | V <sub>SENSE</sub> = 0V                                                 | Full  |      | 20    | 30   | μA     |  |

| DC Common Mode Rejection Ratio, RTI (2)                                 | DC CMRR                                         | V <sub>M</sub> = 2.9V to 70V                                            | Full  | 110  | 145   |      | dB     |  |

| AC Common Mode Rejection Ratio, RTI<br>(Peak-to-Peak Voltage Variation) | AC CMRR                                         | G = 50V/V or G = 100V/V<br>V <sub>M</sub> = 2.9V to 30V, 1kHz sine wave | +25℃  |      | 100   |      | dB     |  |

| Logic Low-Level Input Voltage (SEL1 and SEL2)                           | V <sub>IL</sub>                                 | V <sub>s</sub> = 2.7V to 5.5V                                           | Full  | -0.3 |       | 0.4  | V      |  |

| Logic High-Level Input Voltage (SEL1 and SEL2)                          | V <sub>IH</sub>                                 | V <sub>S</sub> = 2.7V to 5.5V                                           | Full  | 1.2  |       | Vs   | V      |  |

| Input Bias Current of Gain-Select Pins (SEL1 and SEL2)                  | I <sub>SEL</sub>                                | SEL pin connected to GND or $\ensuremath{V}_{\ensuremath{S}}$           | Full  |      | 20    | 150  | nA     |  |

| Output Characteristics                                                  |                                                 |                                                                         |       |      | _     | -    |        |  |

|                                                                         |                                                 | SEL1 = GND, SEL2 = GND                                                  | +25°C |      | 20    |      |        |  |

| Gain                                                                    | G                                               | SEL1 = GND, SEL2 = +V <sub>S</sub>                                      | +25°C |      | 25    |      |        |  |

| Gain                                                                    | 9                                               | SEL1 = +V <sub>S</sub> , SEL2 = GND                                     | +25°C |      | 50    |      |        |  |

|                                                                         |                                                 | SEL1 = +V <sub>S</sub> , SEL2 = +V <sub>S</sub>                         | +25°C |      | 100   |      |        |  |

| Output Voltage Drift <sup>(3)</sup>                                     | $\Delta V_{OUT} / \Delta T$                     | G = 50V/V                                                               | Full  |      | ±10   | ±40  | ppm/°C |  |

| Output Stage Load Regulation                                            | $\Delta V_{\text{OUT}} / \Delta I_{\text{OUT}}$ | G = 50V/V, -10mA < I <sub>OUT</sub> < 10mA                              | +25°C |      | ±0.05 | ±0.8 | mV/mA  |  |

|                                                                         |                                                 | $V_{\text{SENSE}} = 50 \text{mV}^{(5)}$                                 | +25°C |      |       | ±0.8 |        |  |

|                                                                         |                                                 | V SENSE - SOMV A                                                        | Full  |      |       | ±3.0 | - %    |  |

|                                                                         |                                                 | V <sub>SENSE</sub> = 90mV <sup>(5)</sup>                                | +25°C |      |       | ±0.8 |        |  |

|                                                                         |                                                 | V SENSE - 9011V                                                         | Full  |      |       | ±3.0 |        |  |

| Total Output Voltage Accuracy (4)                                       | Δν <sub>ουτ</sub>                               | V <sub>SENSE</sub> = 20mV                                               | +25°C |      |       | ±1   |        |  |

| Total Output Voltage Accuracy                                           | <b>∆v</b> 001                                   | V SENSE - ZOTTV                                                         | Full  |      |       | ±3.5 |        |  |

|                                                                         |                                                 | V <sub>SENSE</sub> = 10mV                                               | +25℃  |      |       | ±1   |        |  |

|                                                                         |                                                 | V SENSE - TOTTV                                                         | Full  |      |       | ±3.5 |        |  |

|                                                                         |                                                 | V <sub>SENSE</sub> = 5mV                                                | +25℃  |      |       | ±1   |        |  |

|                                                                         |                                                 |                                                                         | Full  |      |       | ±4.0 |        |  |

| Output Short-Circuit Current                                            | I <sub>SC</sub>                                 | OUT connected to $V_{\text{S}}$ or GND                                  | +25°C | 30   | 35    |      | mA     |  |

| Output Stage High-State Saturation Voltage                              | V <sub>он</sub>                                 | $V_{OH} = V_S - V_{OUT}, V_{SENSE} = 1V,$<br>$I_{OUT} = 1mA$            | +25℃  |      | 50    | 60   | mV     |  |

| Output Stage Low-State Saturation Voltage                               | V <sub>OL</sub>                                 | V <sub>SENSE</sub> = -1V, I <sub>OUT</sub> = 1mA                        | +25°C |      | 40    | 55   | mV     |  |

NOTES:

1. See Gain (G) and Input Offset Voltage (Vos) section.

2. See Common Mode Rejection Ratio (CMRR) section.

3. See Output Voltage Drift section.

4. See Output Voltage Accuracy section.

5. Except for G = 100V/V.

## **ELECTRICAL CHARACTERISTICS (continued)**

$(+V_{s} = 5V, -V_{s} \text{ connected to GND (single-supply operation)}, V_{M} = 12V, V_{SENSE} = V_{P} - V_{M} = 50mV$ , no load on OUT pin, all gain configurations, Full = -40°C to +125°C, typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                                        | SYMBOL           | CONDITIONS                                                                                                                              |            | TEMP  | MIN | TYP | MAX | UNITS  |

|----------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------|-------|-----|-----|-----|--------|

| Power Supply                                                                     |                  |                                                                                                                                         |            |       |     |     |     |        |

| Total Supply Current                                                             |                  | $V_{SENSE} = 0V$                                                                                                                        |            | Full  |     | 320 |     |        |

| Total Supply Current                                                             | lα               | G = 50V/V, V <sub>SENSE</sub> = 50mV                                                                                                    | Full       |       | 420 | 520 | μA  |        |

| Power Supply Rejection Ratio (6)                                                 | PSRR             | SEL1 = GND, SEL2 = GND,<br>V <sub>S</sub> = 2.7V to 5.5V, $V_{SENSE}$ = 30mV                                                            |            | Full  | 95  | 130 |     | dB     |

| Frequency Response                                                               |                  |                                                                                                                                         |            |       |     |     |     |        |

| 3dB Bandwidth                                                                    | BW               | G = 50V/V,<br>C <sub>L</sub> = 47pF, V <sub>M</sub> = 12V, V <sub>SENSE</sub> = 50mV                                                    |            | +25°C |     | 950 |     | kHz    |

| Slew Rate                                                                        | SR               | $V_{\text{SENSE}}$ = 10mV to 10                                                                                                         | 0mV        | +25°C |     | 1   |     | V/µs   |

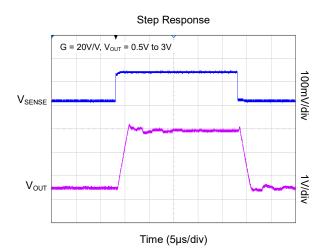

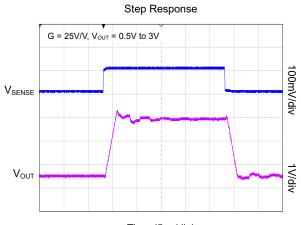

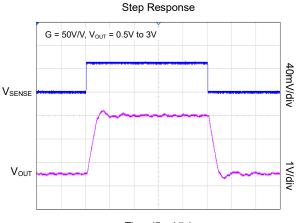

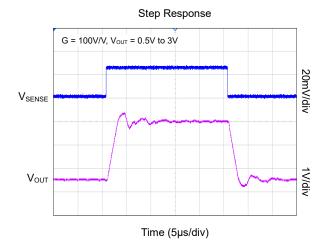

|                                                                                  |                  | $V_{\text{SENSE}}$ square pulse<br>applied to generate<br>a variation of $V_{\text{OUT}}$<br>from 500mV to 3V,<br>$C_{\text{L}}$ = 47pF | G = 20V/V  | +25°C |     | 25  |     | - µs   |

| Response to Input Differential Voltage Change                                    |                  |                                                                                                                                         | G = 25V/V  | +25°C |     | 25  |     |        |

| (Output Settling to 1% of Final Value)                                           | t <sub>s</sub>   |                                                                                                                                         | G = 50V/V  | +25°C |     | 25  |     |        |

|                                                                                  |                  |                                                                                                                                         | G = 100V/V | +25°C |     | 25  |     |        |

| Response to a Gain Change<br>(Output Settling to 1% of Final Value)              | t <sub>SEL</sub> | Any change of state of SEL1 or SEL2 pin                                                                                                 |            | +25°C |     | 15  |     | μs     |

| Response to Common Mode Voltage Change<br>(Output Settling to 1% of Final Value) | t <sub>REC</sub> | $+V_s = 5V$ , $-V_s = -5V$ , $V_M$ step change<br>from -2V to 30V or 30V to -2V                                                         |            | +25°C |     | 35  |     | μs     |

| Noise                                                                            |                  |                                                                                                                                         |            |       |     |     |     |        |

| Equivalent Input Noise Voltage                                                   | en               | f = 1kHz                                                                                                                                |            | +25°C |     | 50  |     | nV/√Hz |

NOTE:

6. See Supply Voltage Rejection Ratio (PSRR) section.

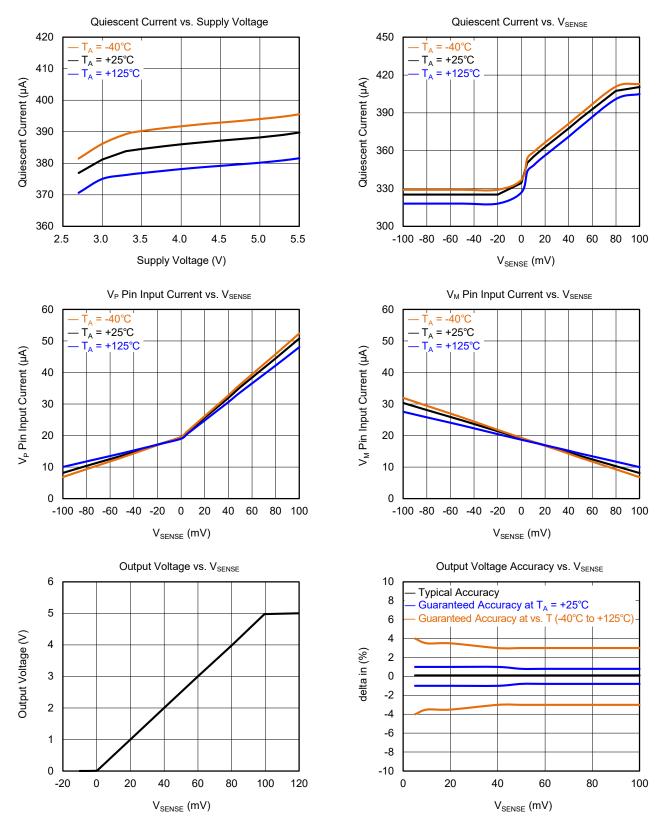

## **TYPICAL PERFORMANCE CHARACTERISTICS**

At  $T_A = +25^{\circ}C$ ,  $V_S = 5V$ ,  $V_{SENSE} = V_P - V_M = 50mV$ ,  $V_M = 12V$ , no load on OUT pin, unless otherwise noted.

SG Micro Corp

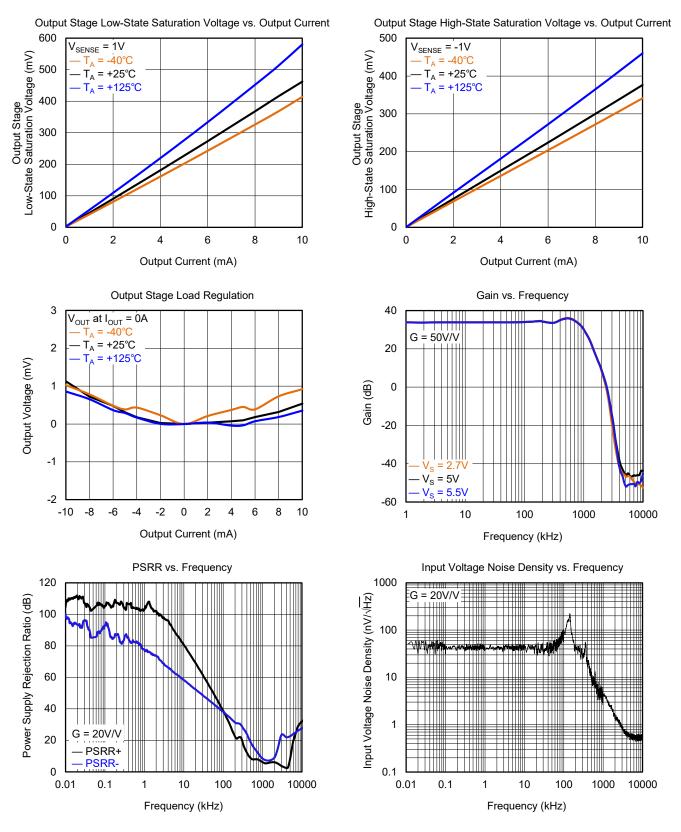

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}$ C,  $V_S = 5$ V,  $V_{SENSE} = V_P - V_M = 50$ mV,  $V_M = 12$ V, no load on OUT pin, unless otherwise noted.

SG Micro Corp

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}$ C,  $V_S = 5$ V,  $V_{SENSE} = V_P - V_M = 50$ mV,  $V_M = 12$ V, no load on OUT pin, unless otherwise noted.

Time (5µs/div)

## DETAILED DESCRIPTION

### **Common Mode Rejection Ratio (CMRR)**

The CMRR measures the ability to reject any variation from input common mode voltage of the SGM8196. The CMRR equation in Equation 1 illustrates the effect on the differential input signal by changing the common mode voltage level:

$$CMRR = -20 \times \log \frac{\Delta V_{OUT}}{\Delta V_{CM} \times G}$$

(1)

### **Power Supply Rejection Ratio (PSRR)**

The PSRR measures the ability of the SGM8196 to reject any variation from the power supply. The PSRR equation in Equation 2 illustrates the effect on the differential input signal by changing the supply voltage level:

$$PSRR = -20 \times \log \frac{\Delta V_{OUT}}{\Delta V_{S} \times G}$$

(2)

#### Gain (G) and Input Offset Voltage (Vos)

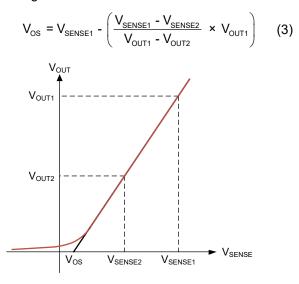

The input offset voltage can be calculated within the linear region of the curve in Figure 1. If the corresponding sense voltage for  $V_{OUT1}$  is  $V_{SENSE1}$  and the corresponding sense voltage for  $V_{OUT2}$  is  $V_{SENSE2}$ , the following equation can be used to calculate the offset voltage of SGM8196:

Figure 1. V<sub>OUT</sub> vs. V<sub>SENSE</sub> Characteristics: Detail for Low V<sub>SENSE</sub> Values

| The values of VSENSE1 and        | V <sub>SENSE2</sub> used for the input |

|----------------------------------|----------------------------------------|

| offset calculations are detailed | ed in Table 1.                         |

Table 1. Test Conditions for Vos Voltage Calculation

| Product | Product Gain (V/V) |    | V <sub>SENSE2</sub> (mV) |

|---------|--------------------|----|--------------------------|

| SGM8196 | 20                 | 50 | 5                        |

|         | 25                 | 50 | 5                        |

|         | 50                 | 50 | 5                        |

|         | 100                | 40 | 5                        |

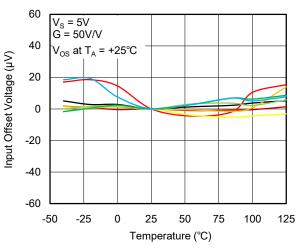

#### Input Offset Voltage Drift

The offset voltage drift versus temperature is the absolute maximum variation of V<sub>OS</sub> relative to its value at +25°C over the temperature range. It is calculated with Equation 5:

$$\frac{\Delta V_{OS}}{\Delta T} = MAX \frac{V_{OS}(T_A) - V_{OS}(+25^{\circ}C)}{T_A - 25^{\circ}C}$$

(5)

with  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$

Figure 2. Input Offset Voltage Drift vs. Temperature

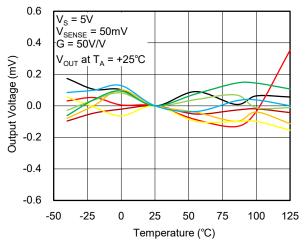

### **Output Voltage Drift**

The output voltage drift versus temperature is the absolute maximum variation of  $V_{OUT}$  relative to its value at +25°C over the temperature range. The following equation illustrates how to calculate the drift of the output voltage:

$$\frac{\Delta V_{\text{out}}}{\Delta T} = MAX \frac{V_{\text{out}}(T_{\text{A}}) - V_{\text{out}}(+25^{\circ}C)}{T_{\text{A}} - 25^{\circ}C}$$

(4)

with  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$

## **DETAILED DESCRIPTION (continued)**

Figure 3. Output Voltage Drift vs. Temperature

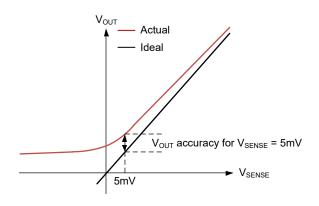

### **Output Voltage Accuracy**

The accuracy of the output voltage is the gap between the actual  $V_{OUT}$  and the ideal  $V_{OUT}$ . For the ideal  $V_{OUT}$ , it equals to the differential input voltage multiplied by the theoretical gain of the SGM8196, which is shown as Equation 6:

$$V_{OUT-TH} = G \times V_{SENSE}$$

(6)

The actual  $V_{OUT}$  is different from the ideal one due to the following two features:

• the input offset voltage Vos

• the non-linearity

Figure 4. V<sub>OUT</sub> vs. V<sub>SENSE</sub> Theoretical and Actual Characteristics

The output voltage accuracy is a percentage value. The Equation 7 illustrates how to calculate the accuracy of the output voltage:

$$\Delta V_{\text{out}} = \frac{\text{ABS}(V_{\text{out}} - (G \times V_{\text{sense}}))}{G \times V_{\text{sense}}}$$

(7)

with 20V/V, 25V/V, 50V/V or 100V/V which can be set by the gain-select pins (SEL1 and SEL2).

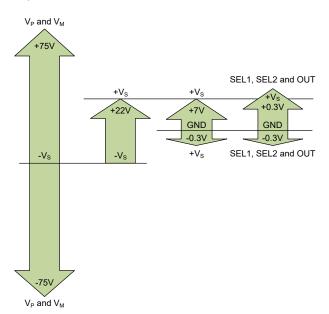

### **Maximum Permissible Voltages on Pins**

Both the single-supply and dual-supply operations can be applied to the SGM8196. For dual-supply mode, the customers need to connect the -V<sub>S</sub> pin to a negative supply voltage. In Figure 5, it shows that the potential voltage for the absolute maximum voltage of V<sub>P</sub> and V<sub>M</sub> is referred to the -V<sub>S</sub> pin, while the absolute voltage for SEL1, SEL2 and positive power supply is referred to the GND pin. Also, one thing should be mentioned that the maximum voltage difference between +V<sub>S</sub> and -V<sub>S</sub> is equal to 22V.

Figure 5. Maximum Voltages on Pins

## **APPLICATION INFORMATION**

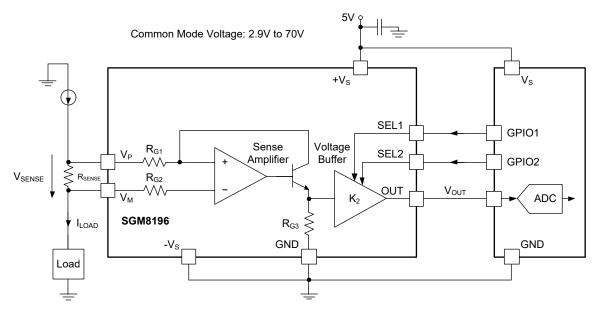

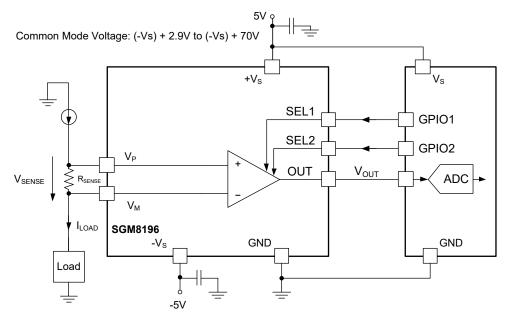

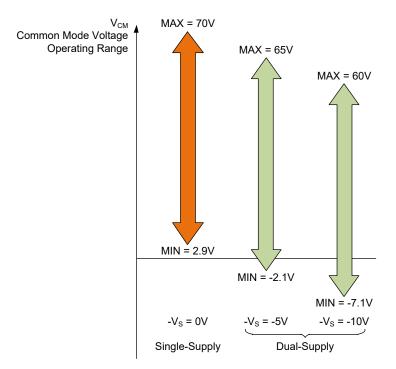

The SGM8196 can operate in single-supply operation or dual-supply operation. If the users desire to apply a single-supply voltage to the SGM8196, the allowable input common mode voltage is not related to the power supply and the range is from 2.9V to 70V. If the users desire to apply a dual-supply voltage to the SGM8196, the allowable input common mode voltage will be shifted by the voltage level of  $-V_s$ . For example, if the  $+V_s$  and  $-V_s$  of the SGM8196 are equal to +5V and -5V respectively, the allowable input common mode voltage range is from -2.1V to 65V. Ramp time of SGM8196 within 1ms could keep from output jitter.

Figure 6. Single-Supply Operation Schematic

The SGM8196 can measure the current from the load and transfer the analog output voltage to the internal ADC of the MCU. The SEL1 and SEL2 pins are also controlled by the I/O pins of MCU to adjust the gain of the SGM8196.

The V<sub>SENSE</sub> is the voltage drop of R<sub>SENSE</sub> due to the current flowing through the shunt resistor. Because of the significant small input current of the sense amplifier, the inverting input voltage is equal to V<sub>M</sub>. The open-loop gain of the amplifier is special large, so the non-inverting input of the amplifier is forced to be equal to the inverting input. Consequently, the V<sub>SENSE</sub> is matched with the voltage drop across R<sub>G1</sub>.

The voltage drop at  $R_{G1}$  is equal to:

$$V_{RG1} = V_{SENSE} = R_{SENSE} \times I_{LOAD}$$

(8)

$I_{RG1}$  is the amount of current that flows through the  $R_{G1}$ , so the calculation of  $I_{RG1}$  is given as follows:

$$I_{RG1} = V_{SENSE}/R_{G1}$$

(9)

All of the  $I_{RG1}$  flows into the resistor  $R_{G3}$  (the input impedance of the buffer is significant large). As a result, the voltage drop across  $R_{G3}$  can be calculated as below:

$$V_{RG3} = R_{G3} \times I_{RG1} = (R_{G3}/R_{G1}) \times V_{SENSE} = K_1 \times V_{SENSE}$$

with  $K_1 = R_{G3}/R_{G1}$  (10)

The  $V_{RG3}$  will be buffered by the second stage amplifier with a voltage gain of  $K_2$  (can be adjusted by SEL1 and SEL2):

$$V_{OUT} = K_1 \times K_2 \times V_{SENSE} = G \times V_{SENSE}$$

with G = K<sub>1</sub> × K<sub>2</sub> (11)

or:

$$V_{OUT} = G \times R_{SENSE} \times I_{LOAD}$$

(12)

The first gain  $K_1$ , which is equal to  $R_{G3}/R_{G1}$ , can be set to 20V/V. The second gain  $K_2$  can be set to 1, 1.25, 2.5 or 5 by the voltage level of SEL1 and SEL2. The values of  $R_{SENSE}$  and gain will determine the full-scale output voltage range of the SGM8196, so these values should be selected properly based on the application.

# **APPLICATION INFORMATION (continued)**

Figure 7. Dual-Supply Operation Schematic

Figure 8. Common Mode vs. Supply Voltage in Dual-Supply Operation

Page

# **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Original (AUGUST 2024) to REV.A

| Changed from product preview to production dataAll |

|----------------------------------------------------|

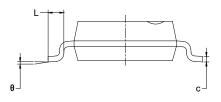

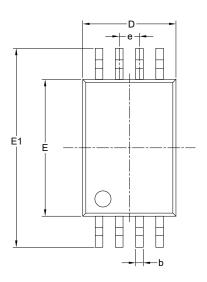

# PACKAGE OUTLINE DIMENSIONS SOIC-8

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | -     | Dimensions<br>In Millimeters |       | nsions<br>ches |

|--------|-------|------------------------------|-------|----------------|

|        | MIN   | MAX                          | MIN   | MAX            |

| A      | 1.350 | 1.750                        | 0.053 | 0.069          |

| A1     | 0.100 | 0.250                        | 0.004 | 0.010          |

| A2     | 1.350 | 1.550                        | 0.053 | 0.061          |

| b      | 0.330 | 0.510                        | 0.013 | 0.020          |

| с      | 0.170 | 0.250                        | 0.006 | 0.010          |

| D      | 4.700 | 5.100                        | 0.185 | 0.200          |

| E      | 3.800 | 4.000                        | 0.150 | 0.157          |

| E1     | 5.800 | 6.200                        | 0.228 | 0.244          |

| е      | 1.27  | BSC                          | 0.050 | BSC            |

| L      | 0.400 | 1.270                        | 0.016 | 0.050          |

| θ      | 0°    | 8°                           | 0°    | 8°             |

NOTES: 1. Body dimensions do not include mode flash or protrusion.

2. This drawing is subject to change without notice.

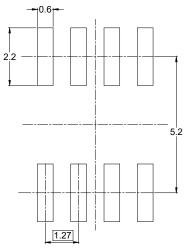

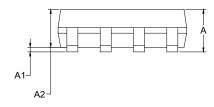

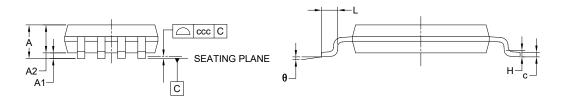

# **PACKAGE OUTLINE DIMENSIONS TSSOP-8**

#### RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dir       | nensions In Millimet | ers   |  |  |

|--------|-----------|----------------------|-------|--|--|

|        | MIN       | NOM                  | МАХ   |  |  |

| A      | -         | -                    | 1.200 |  |  |

| A1     | 0.050     | -                    | 0.150 |  |  |

| A2     | 0.800     | -                    | 1.050 |  |  |

| b      | 0.190     | -                    | 0.300 |  |  |

| С      | 0.090     | -                    | 0.200 |  |  |

| D      | 2.900     | -                    | 3.100 |  |  |

| E      | 4.300     | -                    | 4.500 |  |  |

| E1     | 6.200     | -                    | 6.600 |  |  |

| е      |           | 0.650 BSC            |       |  |  |

| L      | 0.450     | -                    | 0.750 |  |  |

| Н      | 0.250 TYP |                      |       |  |  |

| θ      | 0°        | -                    | 8°    |  |  |

| ССС    | 0.100     |                      |       |  |  |

#### NOTES:

This drawing is subject to change without notice.

The dimensions do not include mold flashes, protrusions or gate burrs.

3. Reference JEDEC MO-153.

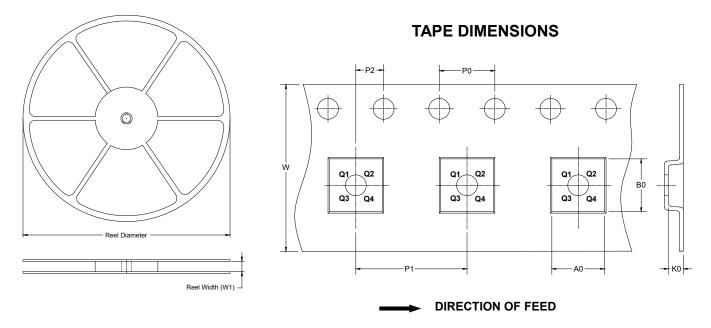

## TAPE AND REEL INFORMATION

### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| SOIC-8       | 13″              | 12.4                     | 6.40       | 5.40       | 2.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| TSSOP-8      | 13″              | 12.4                     | 6.76       | 3.30       | 1.80       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |