#### GENERAL DESCRIPTION

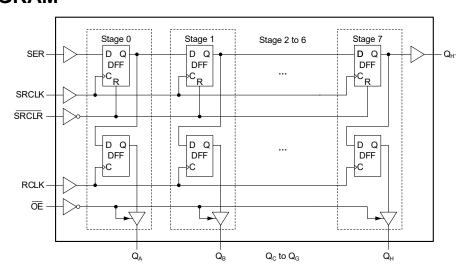

The 74AHC595Q is an 8-bit serial-in/serial-out or parallel-out shift register with 3-state controlled outputs designed for 2.0V to  $5.5V\ V_{CC}$  operation.

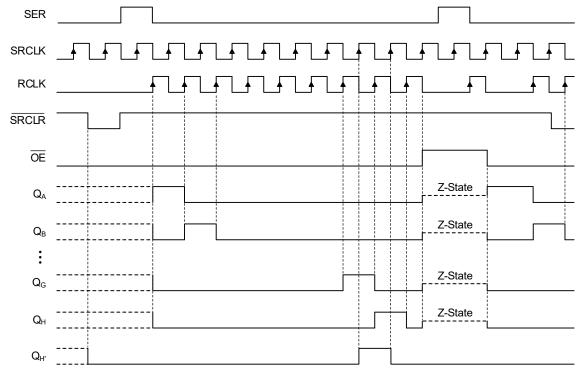

The device integrates an 8-bit shift register and an 8-bit D-type storage register. The storage register features parallel 3-state outputs. The shift register provides a clear input ( $\overline{SRCLR}$ ) with direct overriding function, a serial input ( $\overline{SRCLR}$ ) and a serial output ( $\overline{QH}$ ) to implement cascading. When output enable input ( $\overline{OE}$ ) is held low, the data in storage register will appear at the outputs. When  $\overline{OE}$  is held high, all outputs except  $\overline{QH}$  are in high-impedance state.

Both the shift register and storage register have separate clocks. The shift register clock (SRCLK) and storage register clock (RCLK) are positive-edge triggered. If the SRCLK and RCLK are connected together, the shift register always leads one clock pulse than the storage register all the time.

The device is AEC-Q100 qualified (Automotive Electronics Council (AEC) standard Q100 Grade 1) and it is suitable for automotive applications.

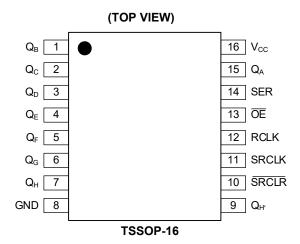

The 74AHC595Q is available in a Green TSSOP-16 package. It operates over an operating temperature range of -40°C to +125°C.

#### **FEATURES**

- AEC-Q100 Qualified for Automotive Applications

Device Temperature Grade 1

T<sub>A</sub> = -40°C to +125°C

- Wide Supply Voltage Range: 2.0V to 5.5V

- 8-Bit Serial-In/Serial-Out or Parallel-Out Shift Register

- Direct Clear Input of Shift Register

- -40°C to +125°C Operating Temperature Range

- Available in a Green TSSOP-16 Package

#### **APPLICATIONS**

Automotive Applications Medical Equipment

#### **LOGIC DIAGRAM**

#### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE TOP<br>MARKING | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|------------------------|---------------------|

| 74AHC595Q | TSSOP-16               | -40°C to +125°C                   | 74AHC595QTS16G/TR  | 1DXTS16<br>XXXXX       | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

#### NOTES:

- 1. The input and output voltage ratings may be exceeded if the input and output clamp current ratings are observed.

- 2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability.

- 3. For human body model (HBM), all pins comply with AEC-Q100-002 specification.

- 4. For charged device model (CDM), all pins comply with AEC-Q100-011 specification.

- 5. Unused input pins must be held at  $V_{\text{CC}}$  or GND to guarantee the device in normal operation.

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range, V <sub>CC</sub>                   | 2.0V to 5.5V          |

|---------------------------------------------------------|-----------------------|

| Input Voltage Range, V <sub>I</sub> <sup>(5)</sup>      | 0V to 5.5V            |

| Output Voltage Range, Vo                                | 0V to V <sub>CC</sub> |

| Input Transition Rise or Fall Rate, $\Delta t/\Delta V$ |                       |

| V <sub>CC</sub> = 3.3V ± 0.3V                           | 100ns/V (MAX)         |

| V <sub>CC</sub> = 5.0V ± 0.5V                           | 20ns/V (MAX)          |

| Operating Temperature Range                             | 40°C to +125°C        |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

### **FUNCTION TABLE**

| (        | CONTRO   | L INPUT | S     | INPUT | OUTI           | PUTS                            | FUNCTION                                                                                                                                                                                 |  |  |  |

|----------|----------|---------|-------|-------|----------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SRCLK    | RCLK     | ŌĒ      | SRCLR | SER   | Q <sub>H</sub> | Q <sub>A</sub> ~ Q <sub>H</sub> | FUNCTION                                                                                                                                                                                 |  |  |  |

| X        | X        | L       | L     | X     | L              | NC                              | When SRCLR is low, it only affects the shift register.                                                                                                                                   |  |  |  |

| X        | <b>↑</b> | L       | L     | X     | L              | L                               | Load the empty shift register into the storage register.                                                                                                                                 |  |  |  |

| Х        | Х        | Н       | L     | Х     | L              | Z                               | Shift register is reset and all parallel outputs are in high -impedance state.                                                                                                           |  |  |  |

| <b>↑</b> | X        | L       | Н     | Н     | $Q_{G'}$       | NC                              | When shift register stage 0 goes high, data of all shift register stages shifted through, e.g. the serial output $(Q_{H'})$ presents the previous state of stage 6 (internal $Q_{G'}$ ). |  |  |  |

| X        | 1        | L       | Н     | X     | NC             | $Q_{x'}$                        | Data of shift register (internal $Q_{x'}$ ) is transferred to the storage register and parallel output stages.                                                                           |  |  |  |

| <u></u>  | 1        | L       | Н     | X     | $Q_{G^{'}}$    | $Q_{x'}$                        | Data of shift register shifted through, previous data of the shift register is transferred to the storage register and parallel output stages.                                           |  |  |  |

H = High Voltage Level

L = Low Voltage Level

↑ = Low-to-High Clock Transition

Z = High-Impedance State

NC = No Change

X = Don't Care

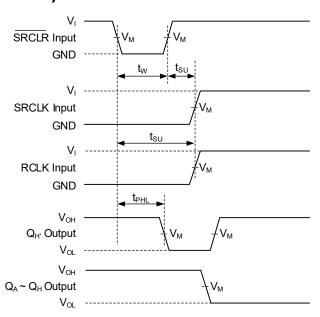

#### **TIMING DIAGRAM**

Figure 1. Timing Diagram

#### **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN                     | NAME                              | FUNCTION                                              |

|-------------------------|-----------------------------------|-------------------------------------------------------|

| 15, 1, 2, 3, 4, 5, 6, 7 | $Q_A,Q_B,Q_C,Q_D,Q_E,Q_F,Q_G,Q_H$ | Parallel Data Outputs.                                |

| 8                       | GND                               | Ground.                                               |

| 9                       | Q <sub>H</sub> '                  | Serial Data Output.                                   |

| 10                      | SRCLR                             | Shift Register Clear Input (Active-Low).              |

| 11                      | SRCLK                             | Shift Register Clock Input (Rising Edge Triggered).   |

| 12                      | RCLK                              | Storage Register Clock Input (Rising Edge Triggered). |

| 13                      | ŌĒ                                | Output Enable Input (Active-Low).                     |

| 14                      | SER                               | Serial Data Input.                                    |

| 16                      | V <sub>CC</sub>                   | Power Supply.                                         |

# **ELECTRICAL CHARACTERISTICS**

(Full = -40°C to +125°C, all typical values are measured at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                 | SYMBOL          | CONDITIONS                                                                                                            | TEMP  | MIN  | TYP                                                                           | MAX  | UNITS |  |

|---------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|-------|------|-------------------------------------------------------------------------------|------|-------|--|

|                           |                 | V <sub>CC</sub> = 2.0V                                                                                                | Full  | 0.5  |                                                                               |      |       |  |

| High-Level Input Voltage  | $V_{IH}$        | V <sub>CC</sub> = 3.0V                                                                                                | Full  | 0.9  |                                                                               |      | V     |  |

|                           |                 | V <sub>CC</sub> = 5.5V                                                                                                | Full  | 1.65 |                                                                               |      |       |  |

|                           |                 | V <sub>CC</sub> = 2.0V                                                                                                | Full  |      |                                                                               | 1.5  |       |  |

| Low-Level Input Voltage   | V <sub>IL</sub> | V <sub>CC</sub> = 3.0V                                                                                                | Full  |      |                                                                               | 2.1  | V     |  |

|                           |                 | V <sub>CC</sub> = 5.5V                                                                                                | Full  |      | 1.995 2.995 4.495 2.85 4.3 0.005 0.005 0.005 0.15 0.20 ±0.01 ±0.01 0.02 4 5.5 | 3.85 |       |  |

|                           |                 | V <sub>CC</sub> = 2.0V, I <sub>OH</sub> = -50μA                                                                       | Full  | 1.9  | 1.995                                                                         |      |       |  |

| High-Level Output Voltage |                 | V <sub>CC</sub> = 3.0V, I <sub>OH</sub> = -50μA                                                                       | Full  | 2.9  | 2.995                                                                         |      | 1     |  |

|                           | V <sub>OH</sub> | V <sub>CC</sub> = 4.5V, I <sub>OH</sub> = -50μA                                                                       | Full  | 4.4  | 4.495                                                                         |      | V     |  |

|                           |                 | V <sub>CC</sub> = 3.0V, I <sub>OH</sub> = -4mA                                                                        | Full  | 2.5  | 2.85                                                                          |      |       |  |

|                           |                 | V <sub>CC</sub> = 4.5V, I <sub>OH</sub> = -8mA                                                                        | Full  | 3.8  | 4.3                                                                           | 1.5  |       |  |

|                           |                 | $V_{CC} = 2.0V, I_{OL} = 50\mu A$                                                                                     | Full  |      | 0.005                                                                         | 0.1  |       |  |

|                           |                 | $V_{CC} = 3.0V, I_{OL} = 50\mu A$                                                                                     | Full  |      | 0.005                                                                         | 0.1  |       |  |

| Low-Level Output Voltage  | V <sub>OL</sub> | $V_{CC} = 4.5V, I_{OL} = 50\mu A$                                                                                     | Full  |      | 0.005                                                                         | 0.1  | V     |  |

|                           |                 | V <sub>CC</sub> = 3.0V, I <sub>OL</sub> = 4mA                                                                         | Full  |      | 0.15                                                                          | 0.5  |       |  |

|                           |                 | V <sub>CC</sub> = 4.5V, I <sub>OL</sub> = 8mA                                                                         | Full  |      | 0.20                                                                          | 0.5  |       |  |

| Input Leakage Current     | l <sub>1</sub>  | V <sub>CC</sub> = 0V to 5.5V, V <sub>I</sub> = 5.5V or GND                                                            | Full  |      | ±0.01                                                                         | ±1   | μA    |  |

| Off-State Output Current  | l <sub>oz</sub> | $Q_A \sim Q_H$ , $V_{CC} = 5.5V$ , $V_I = V_{CC}$ or GND, $V_O = V_{CC}$ or GND, $\overline{OE} = V_{IH}$ or $V_{IL}$ | Full  |      | ±0.01                                                                         | ±5   | μA    |  |

| Supply Current            | Icc             | $V_{CC}$ = 5.5V, $V_I$ = $V_{CC}$ or GND, $I_O$ = 0A                                                                  | Full  |      | 0.02                                                                          | 5    | μΑ    |  |

| Input Capacitance         | Cı              | $V_{CC}$ = 5.0V, $V_I$ = $V_{CC}$ or GND                                                                              | +25°C |      | 4                                                                             |      | pF    |  |

| Output Capacitance        | Co              | $V_{CC}$ = 5.0V, $V_{O}$ = $V_{CC}$ or GND                                                                            | +25℃  |      | 5.5                                                                           |      | pF    |  |

# **DYNAMIC CHARACTERISTICS**

(See Figure 2 for test circuit. Full = -40°C to +125°C,  $C_L$  = 50pF, all typical values are measured at  $T_A$  = +25°C,  $V_{CC}$  = 3.3V and 5.0V respectively, unless otherwise noted.)

| PARAMETER                      | SYMBOL           | CONI                                      | DITIONS                  | TEMP | MIN (1) | TYP  | MAX (1) | UNITS   |  |

|--------------------------------|------------------|-------------------------------------------|--------------------------|------|---------|------|---------|---------|--|

|                                |                  | RCLK to Q <sub>A</sub> ~ Q <sub>H</sub> , | $V_{CC} = 3.3V \pm 0.3V$ | Full | 1       | 8.5  | 14.2    |         |  |

| Low to Lligh Propagation Daloy |                  | see Figure 4                              | $V_{CC} = 5.0V \pm 0.5V$ | Full | 0.5     | 6.5  | 10.2    |         |  |

| Low-to-High Propagation Delay  | t <sub>PLH</sub> | SRCLK to Q <sub>H</sub> ,                 | $V_{CC} = 3.3V \pm 0.3V$ | Full | 1       | 9.0  | 14.4    | ns      |  |

|                                |                  | see Figure 3                              | $V_{CC} = 5.0V \pm 0.5V$ | Full | 1       | 6.5  | 10.3    |         |  |

|                                |                  | RCLK to Q <sub>A</sub> ~ Q <sub>H</sub> , | $V_{CC} = 3.3V \pm 0.3V$ | Full | 1       | 8.5  | 13.6    |         |  |

|                                |                  | see Figure 4                              | $V_{CC} = 5.0V \pm 0.5V$ | Full | 1       | 6.5  | 10.2    |         |  |

| High-to-Low Propagation Delay  |                  | SRCLK to Q <sub>H</sub> ,                 | $V_{CC} = 3.3V \pm 0.3V$ | Full | 1       | 8.5  | 13.9    |         |  |

| High-to-Low Propagation Delay  | t <sub>PHL</sub> | see Figure 3                              | $V_{CC} = 5.0V \pm 0.5V$ | Full | 0.5     | 8.5  | 13.7    | ns<br>- |  |

|                                |                  | SRCLR to Q <sub>H</sub> , see Figure 6    | $V_{CC} = 3.3V \pm 0.3V$ | Full | 1       | 7.5  | 14.9    |         |  |

|                                |                  |                                           | $V_{CC} = 5.0V \pm 0.5V$ | Full | 0.5     | 6.5  | 11.7    |         |  |

| Off-to-High Propagation Delay  |                  |                                           | $V_{CC} = 3.3V \pm 0.3V$ | Full | 1       | 7.5  | 13.0    | - ns    |  |

| On-to-riigh Fropagation Delay  | t <sub>PZH</sub> | ŌĒ to Q <sub>A</sub> ∼ Q <sub>H</sub> ,   | $V_{CC} = 5.0V \pm 0.5V$ | Full | 0.5     | 6.0  | 9.6     |         |  |

| Off-to-Low Propagation Delay   | 4                | see Figure 7                              | $V_{CC} = 3.3V \pm 0.3V$ | Full | 1       | 7.5  | 12.0    |         |  |

| On-to-Low Propagation Delay    | t <sub>PZL</sub> |                                           | $V_{CC} = 5.0V \pm 0.5V$ | Full | 0.5     | 6.0  | 9.4     |         |  |

| High-to-Off Propagation Delay  |                  |                                           | $V_{CC} = 3.3V \pm 0.3V$ | Full | 1       | 11.0 | 15.8    |         |  |

| High-to-Off Propagation Delay  | t <sub>PHZ</sub> | $\overline{OE}$ to $Q_A \sim Q_H$ ,       | $V_{CC} = 5.0V \pm 0.5V$ | Full | 1       | 8.0  | 11.4    | ns      |  |

| Low-to-Off Propagation Delay   | 4                | see Figure 7                              | $V_{CC} = 3.3V \pm 0.3V$ | Full | 1       | 11.0 | 16.8    |         |  |

| Low-to-On Propagation Delay    | t <sub>PLZ</sub> |                                           | $V_{CC} = 5.0V \pm 0.5V$ | Full | 1       | 6.5  | 12.2    |         |  |

| Maximum Frequency              | f                | See Figure 3 and                          | $V_{CC} = 3.3V \pm 0.3V$ | Full | 90      | 130  |         | - MHz   |  |

| Iviaximum Frequency            | f <sub>MAX</sub> | Figure 4                                  | $V_{CC} = 5.0V \pm 0.5V$ | Full | 100     | 155  |         |         |  |

#### NOTE:

1. Specified by design and characterization, not production tested.

# **DYNAMIC CHARACTERISTICS (continued)**

(See Figure 2 for test circuit. Full = -40°C to +125°C,  $C_L = 50$ pF, all typical values are measured at  $T_A = +25$ °C,  $V_{CC} = 3.3$ V and 5.0V respectively, unless otherwise noted.)

| PARAMETER                             | SYMBOL          | CONDITIONS                                      | 3                             | TEMP  | MIN <sup>(1)</sup> | TYP | MAX <sup>(1)</sup> | UNITS |

|---------------------------------------|-----------------|-------------------------------------------------|-------------------------------|-------|--------------------|-----|--------------------|-------|

|                                       |                 | SRCLK high or low, see Figure 3                 | $V_{CC} = 3.3V \pm 0.3V$      | Full  | 6                  |     |                    |       |

|                                       |                 | SKOLK High or low, see Figure 3                 | $V_{CC} = 5.0V \pm 0.5V$      | Full  | 6                  |     |                    |       |

| Pulse Width                           |                 | DCL K high or low one Figure 4                  | $V_{CC} = 3.3V \pm 0.3V$      | Full  | 6                  |     |                    |       |

|                                       | t <sub>W</sub>  | RCLK high or low, see Figure 4                  | $V_{CC} = 5.0V \pm 0.5V$      | Full  | 6                  |     |                    | ns    |

|                                       |                 | CDCLD law are Figure C                          | $V_{CC} = 3.3V \pm 0.3V$      | Full  | 9                  |     |                    |       |

|                                       |                 | SRCLR low, see Figure 6                         | V <sub>CC</sub> = 5.0V ± 0.5V | Full  | 9                  |     |                    |       |

|                                       |                 | SER before SRCLK ↑,                             | $V_{CC} = 3.3V \pm 0.3V$      | Full  | 4                  |     |                    |       |

|                                       |                 | see Figure 5                                    | $V_{CC} = 5.0V \pm 0.5V$      | Full  | 3                  |     |                    |       |

| Setup Time                            |                 | SRCLK ↑ before RCLK ↑ (2),                      | $V_{CC} = 3.3V \pm 0.3V$      | Full  | 7                  |     |                    |       |

|                                       |                 | see Figure 4                                    | V <sub>CC</sub> = 5.0V ± 0.5V | Full  | 4                  |     |                    | no    |

| Setup Time                            | t <sub>su</sub> | SRCLR low before RCLK↑,                         | $V_{CC} = 3.3V \pm 0.3V$      | Full  | 7                  |     |                    | ns    |

|                                       |                 | see Figure 6                                    | $V_{CC} = 5.0V \pm 0.5V$      | Full  | 5                  |     |                    |       |

|                                       |                 | SRCLR high (inactive) before                    | $V_{CC} = 3.3V \pm 0.3V$      | Full  | 2                  |     |                    |       |

|                                       |                 | SRCLK ↑, see Figure 6                           | $V_{CC} = 5.0V \pm 0.5V$      | Full  | 2                  |     |                    |       |

|                                       | 4               | CCD ofter CDCL // A con Figure F                | $V_{CC} = 3.3V \pm 0.3V$      | Full  | 2.5                |     |                    | 20    |

| Hold Time                             | t <sub>H</sub>  | SER after SRCLK ↑, see Figure 5                 | V <sub>CC</sub> = 5.0V ± 0.5V | Full  | 2                  |     |                    | ns    |

| Power Dissipation Capacitance (3) (4) | C <sub>PD</sub> | No load, V <sub>CC</sub> = 5.0V ± 0.5V, f = 10N | МНz                           | +25°C |                    | 85  |                    | pF    |

#### NOTES:

- 1. Specified by design and characterization, not production tested.

- 2. The setup time enables the storage register to get stable data from the shift register. In this case where clocks can be tied together, the shift register is a clock pulse in front of the storage register.

- 3.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ).

$$P_D = C_{PD} \times V_{CC}^2 \times f_i \times N + \Sigma (C_L \times V_{CC}^2 \times f_o)$$

where:

$f_i$  = Input frequency in MHz.

$f_o$  = Output frequency in MHz.

C<sub>L</sub> = Output load capacitance in pF.

V<sub>CC</sub> = Supply voltage in Volts.

N = Number of inputs switching.

$\Sigma(C_L \times V_{CC}^2 \times f_0) = \text{Sum of outputs.}$

4. All 9 outputs switching.

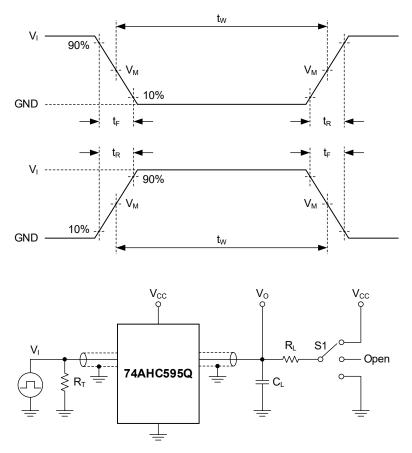

#### **TEST CIRCUIT**

Test conditions are given in Table 1.

Definitions test circuit:

R<sub>L</sub>: Load resistance.

C<sub>L</sub>: Load capacitance (includes jig and probe).

$R_T$ : Termination resistance (equals to output impedance  $Z_0$  of the pulse generator).

S1: Test selection switch.

Figure 2. Test Circuit for Measuring Switching Times

**Table 1. Test Conditions**

| SUPPLY VOLTAGE  | INF                                            | TU      | LO                            | AD  | S1 POSITION                         |                                     |                                     |  |

|-----------------|------------------------------------------------|---------|-------------------------------|-----|-------------------------------------|-------------------------------------|-------------------------------------|--|

| V <sub>cc</sub> | V <sub>I</sub> t <sub>R</sub> , t <sub>F</sub> |         | C <sub>L</sub> R <sub>L</sub> |     | t <sub>PHL</sub> , t <sub>PLH</sub> | t <sub>PZH</sub> , t <sub>PHZ</sub> | t <sub>PZL</sub> , t <sub>PLZ</sub> |  |

| 2.0V to 5.5V    | V <sub>CC</sub>                                | ≤ 3.0ns | 50pF                          | 1kΩ | Open                                | GND                                 | V <sub>CC</sub>                     |  |

#### **WAVEFORMS**

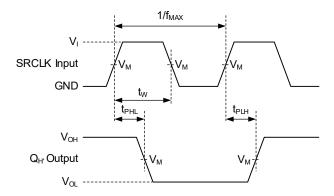

Test conditions are given in Table 1.

Measurement points are given in Table 2.

Logic levels: V<sub>OL</sub> and V<sub>OH</sub> are typical output voltage levels that occur with the output load.

Figure 3. Shift Register Clock Input to Output Propagation Delay Times, Pulse Width and Maximum Frequency

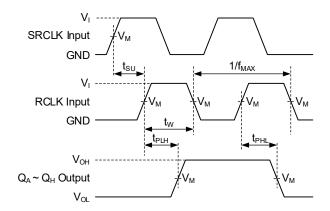

Test conditions are given in Table 1.

Measurement points are given in Table 2.

Logic levels: V<sub>OL</sub> and V<sub>OH</sub> are typical output voltage levels that occur with the output load.

Figure 4. Storage Register Clock Input to Output Propagation Delay Times, Shift Register Clock to Storage Register Clock Setup time, Pulse Width and Maximum Frequency

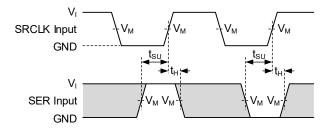

Test conditions are given in Table 1.

Measurement points are given in Table 2.

The shaded areas refer to when the input is allowed to change for predictable output performance.

Figure 5. Data Setup and Hold Times

# **WAVEFORMS** (continued)

Test conditions are given in Table 1.

Measurement points are given in Table 2.

Logic levels:  $V_{\text{OL}}$  and  $V_{\text{OH}}$  are typical output voltage levels that occur with the output load.

Figure 6. Clear Input to Output Propagation Delay times, Pulse Width and Setup Time

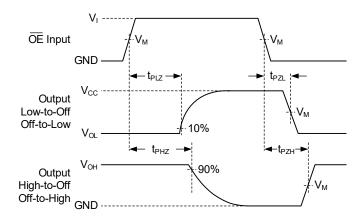

Test conditions are given in Table 1.

Measurement points are given in Table 2.

Logic levels:  $V_{\text{OL}}$  and  $V_{\text{OH}}$  are typical output voltage levels that occur with the output load.

Figure 7. Enable and Disable Times

**Table 2. Measurement Points**

| SUPPLY VOLTAGE  | INF             | TUT                           | OUTPUT                |

|-----------------|-----------------|-------------------------------|-----------------------|

| V <sub>cc</sub> | Vı              | V <sub>M</sub> <sup>(1)</sup> | $V_{M}$               |

| 2.0V to 5.5V    | V <sub>CC</sub> | 0.5 × V <sub>CC</sub>         | 0.5 × V <sub>CC</sub> |

#### NOTE:

1. The measurement points should be  $V_{IH}$  or  $V_{IL}$  when the input rising or falling time exceeds 3.0ns.

# 74AHC595Q

# Automotive, 8-Bit Serial-In/Serial-Out or Parallel-Out **Shift Register with 3-State Controlled Outputs**

# **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Original (FEBRUARY 2025) to REV.A

Page

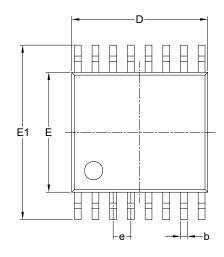

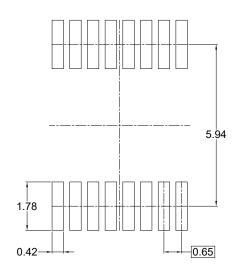

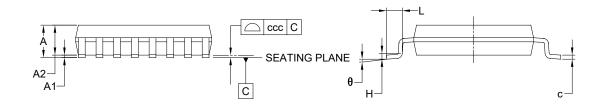

# **PACKAGE OUTLINE DIMENSIONS** TSSOP-16

RECOMMENDED LAND PATTERN (Unit: mm)

| Cumbal | Dir   | nensions In Millimet | ers   |

|--------|-------|----------------------|-------|

| Symbol | MIN   | NOM                  | MAX   |

| А      | -     | -                    | 1.200 |

| A1     | 0.050 | -                    | 0.150 |

| A2     | 0.800 | -                    | 1.050 |

| b      | 0.190 | -                    | 0.300 |

| С      | 0.090 | -                    | 0.200 |

| D      | 4.860 | -                    | 5.100 |

| Е      | 4.300 | -                    | 4.500 |

| E1     | 6.200 | -                    | 6.600 |

| е      |       | 0.650 BSC            |       |

| L      | 0.450 | -                    | 0.750 |

| Н      |       | 0.250 TYP            |       |

| θ      | 0°    | -                    | 8°    |

| ccc    |       | 0.100                |       |

- This drawing is subject to change without notice.

The dimensions do not include mold flashes, protrusions or gate burrs.

- 3. Reference JEDEC MO-153.

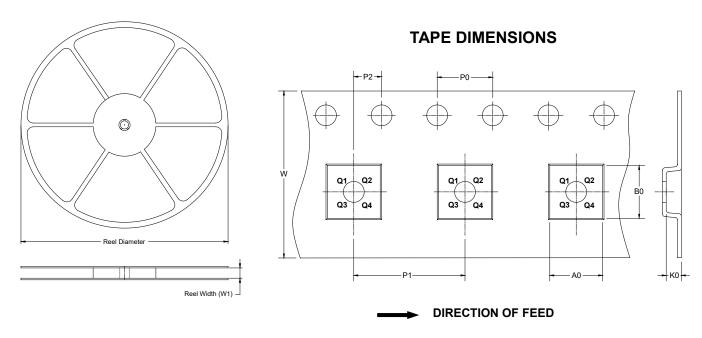

# TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TSSOP-16     | 13"              | 12.4                     | 6.80       | 5.40       | 1.50       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

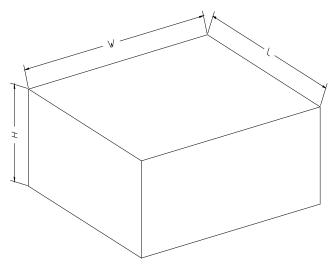

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

# **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |