# SGM61280 8A, 23V, Synchronous Buck Converters with 3.3V/5V LDO

### **GENERAL DESCRIPTION**

The SGM61280 family is a high efficiency and miniature size synchronous Buck converter for wide input voltage applications.

The SGM61280 family, 8A synchronous Buck converter with integrated low  $R_{DSON}$  MOSFET switches, provides both SGM61280-3.3 and SGM61280-5.1 efficient fixed output voltage versions. The device uses constant on-time (COT) control for fast transient response and supports input voltage range from 4.5V to 23V for the SGM61280-3.3, and 5.1V to 23V for the SGM61280-5.1.

The SGM61280 is available in a space-saving Green UTQFN-3×3-12AL package.

## **APPLICATIONS**

Industrial Low Power Systems Laptops and Notebook Computers LCD Monitors and TVs Green Electronics and Appliances DSP, FPGA and ASIC Power Supplies

## FEATURES

- 8A Output Current

- Fixed Output Voltages

- Wide Input Voltage Range:

- 4.5V to 23V Input Range for SGM61280-3.3

- 5.1V to 23V Input Range for SGM61280-5.1

- Constant On-Time (COT) Control

- Low R<sub>DSON</sub> MOSFET Switches (22mΩ/7mΩ)

- 21mΩ/6mΩ for SGM61280-3.3

- 21mΩ/7mΩ for SGM61280-5.1

- Fast Transient Response, Accurate Regulation

- Supports All Low ESR MLCC Output Capacitors

- Fixed Switching Frequency

- LDO Output Voltage

- Internal Soft-Start

- Integrated Output Discharge Resistance

- Cycle-by-Cycle Valley Over-Current Protection

- Input Under-Voltage Lockout

- Thermal Shutdown Protection

- Output Over/Under-Voltage Protection

- Audio Avoid Mode (AAM) to Avoid PFM Acoustic Noise

- Available in a Green UTQFN-3×3-12AL Package

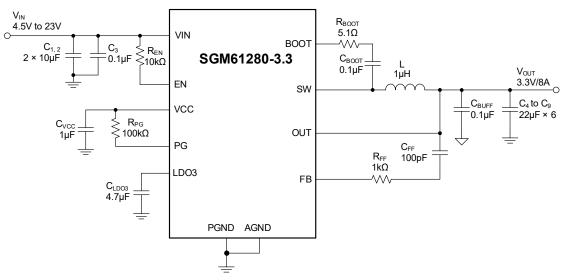

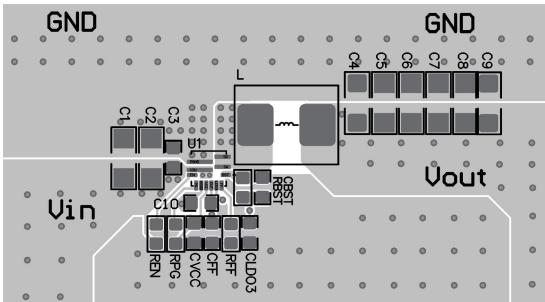

# **TYPICAL APPLICATION**

Figure 1. SGM61280-3.3 Typical Application

### PACKAGE/ORDERING INFORMATION

| MODEL        | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER     | PACKAGE<br>MARKING        | PACKING<br>OPTION   |

|--------------|------------------------|-----------------------------------|------------------------|---------------------------|---------------------|

| SGM61280-3.3 | UTQFN-3×3-12AL         | -40°C to +125°C                   | SGM61280-3.3XUSD12G/TR | SGM029<br>XUSD12<br>XXXXX | Tape and Reel, 1500 |

| SGM61280-5.1 | UTQFN-3×3-12AL         | -40°C to +125°C                   | SGM61280-5.1XUSD12G/TR | SGM02A<br>XUSD12<br>XXXXX | Tape and Reel, 1500 |

### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

- Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage, V <sub>IN</sub> 0.3V to 27V                     |

|-----------------------------------------------------------------|

| Enable Pin Voltage, V <sub>EN</sub> 0.3V to 27V                 |

| FB Pin Voltage, V <sub>FB</sub> 0.3V to 4.5V                    |

| OUT Pin Voltage, V <sub>OUT</sub> (SGM61280-3.3)0.3V to 4.5V    |

| OUT Pin Voltage, V <sub>OUT</sub> (SGM61280-5.1)0.3V to 6V      |

| Switch Voltage                                                  |

| SW (DC)0.3V to (V <sub>IN</sub> + 0.3V)                         |

| SW (AC, Less than 30ns)6V to 28V                                |

| BOOT Voltage, $V_{BOOT}$ ( $V_{SW}$ - 0.3V) to ( $V_{SW}$ + 6V) |

| Other I/O Pin Voltages0.3V to 6V                                |

| Power Dissipation, $P_D @ T_A = +25^{\circ}C$                   |

| UTQFN-3×3-12AL1.5W                                              |

| Package Thermal Resistance                                      |

| UTQFN-3×3-12AL, θ <sub>JA</sub> 81.8°C/W                        |

| UTQFN-3×3-12AL, θ <sub>JB</sub> 10.2°C/W                        |

| UTQFN-3×3-12AL, θ <sub>JC</sub>                                 |

| Junction Temperature+150°C                                      |

| Storage Temperature Range65°C to +150°C                         |

| Lead Temperature (Soldering, 10s)+260°C                         |

| ESD Susceptibility <sup>(1) (2)</sup>                           |

| HBM (SGM61280-3.3)±4000V                                        |

| HBM (SGM61280-5.1) ±3000V                                       |

| CDM±1000V                                                       |

| NOTES                                                           |

#### NOTES:

1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

### **RECOMMENDED OPERATING CONDITIONS**

Supply Input Voltage V<sub>IN</sub> (SGM61280-5.1)......5.1V to 23V Operating Junction Temperature Range.....-40°C to +125°C

NOTE: 1.  $V_{UVLO RISING}$  is 4.6V but  $V_{UVLO FALLING}$  is lower than 4.5V, so input must be > 4.6V for startup, and after startup SGM61280-3.3V can work down to 4.5V input voltage.

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### ESD SENSITIVITY CAUTION

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

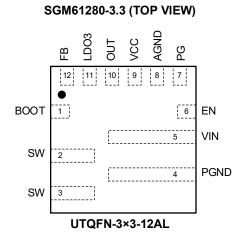

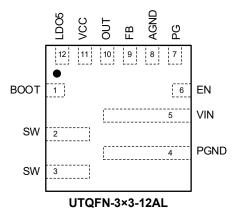

### **PIN CONFIGURATIONS**

#### SGM61280-5.1 (TOP VIEW)

### **PIN DESCRIPTION**

| PIN              |                  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SGM61280<br>-3.3 | SGM61280<br>-5.1 | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1                | 1                | воот | Upper Gate Driver Supply Bootstrap Input. Place a $0.1\mu$ F/10V ceramic capacitor C <sub>BOOT</sub> in series with a 5.1 $\Omega$ R <sub>BOOT</sub> resistor between BOOT and SW pins as close as possible to the IC.                                                                                                                                                                                                                                                        |

| 2, 3             | 2, 3             | SW   | Switching Node Output of the Internal Switches. These pins connect to one terminal of the output inductor and the bootstrap circuit. Keep this trace short with minimal copper area to minimize noise coupling, but it should be enough to carry inductor current.                                                                                                                                                                                                            |

| 4                | 4                | PGND | Power Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5                | 5                | VIN  | Input Supply Pin. Decouple this pin to PGND with at least $10\mu F$ ceramic capacitor as close as possible to these two pins.                                                                                                                                                                                                                                                                                                                                                 |

| 6                | 6                | EN   | Enable Input. Applying a logic high voltage (above 0.6V and below V <sub>IN</sub> ) to EN pin enables the device and a logic low (below 0.5V) will shut it down. EN pin should not be left open. This pin is also used to activate the audio avoid mode (AAM) to prevent audio noise at light loads. The AAM is allowed if the V <sub>EN</sub> voltage is in the 0.6V to 1.9V range. The device is enabled without AAM if V <sub>EN</sub> is between 2V and V <sub>IN</sub> . |

| 7                | 7                | PG   | Open-Drain Power Good Indicator. With a pull-up resistor, this output will go high when the $V_{OUT}$ is above 91% of is nominal value. Pull it up to VCC or a 5.6V or less voltage rail with a resistor (like $100k\Omega$ ).                                                                                                                                                                                                                                                |

| 8                | 8                | AGND | Analog Ground. Decouple VCC to AGND with a $1\mu F$ ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9                | 11               | VCC  | 5.6V Internal Supply Linear Regulator Output. Connect a $1\mu$ F ceramic capacitor between VCC and AGND pins as close to the device as possible.                                                                                                                                                                                                                                                                                                                              |

| 10               | 10               | OUT  | Output Feedback Pin. OUT is an input pin into the IC and must be connected to the output capacitor (regulation point). Output discharge (56 $\Omega$ ) is also through this pin when the device is disabled. It also replaces VIN as input source of the LDO regulator when the V <sub>OUT</sub> is high enough (>3.1V for SGM61280-3.3 and >4.7V for SGM61280-5.1 devices respectively).                                                                                     |

| 11               | _                | LDO3 | 3.3V LDO Output (SGM61280-3.3 Only). It is the power supply source for the internal analog and gate driving circuits, and it can supply up to 100mA to external loads. It must be decoupled to PGND with at least a 4.7µF ceramic capacitor.                                                                                                                                                                                                                                  |

| 12               | 9                | FB   | Feedback Input Pin. Connect the output voltage with an RC network for closed loop control. Keep this line away from noise sources such as SW node.                                                                                                                                                                                                                                                                                                                            |

| _                | 12               | LDO5 | 5.0V LDO Output (SGM61280-5.1 Only). It is the power supply source for the internal analog and gate driving circuits and can supply up to 100mA to external loads. It must be decoupled to PGND with at least a 4.7µF ceramic capacitor.                                                                                                                                                                                                                                      |

# **ELECTRICAL CHARACTERISTICS**

(V<sub>IN</sub> = 12V, typical values are measured at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                        | SYMBOL                         | COND                                 | DITIONS           | MIN  | ТҮР  | MAX  | UNITS |

|----------------------------------|--------------------------------|--------------------------------------|-------------------|------|------|------|-------|

| Input Supply                     |                                |                                      |                   |      |      |      |       |

|                                  |                                | SGM61280-3.3                         |                   | 4.5  |      | 23   |       |

| VIN Input Voltage Range          | Vin                            | SGM61280-5.1                         |                   | 5.1  |      | 23   | V     |

|                                  |                                |                                      | SGM61280-3.3      | 45   | 68   | 90   |       |

| Shutdown Current into VIN        | I <sub>SD</sub>                | $V_{EN} = 0V$                        | SGM61280-5.1      | 45   | 64   | 90   | μA    |

|                                  |                                | V <sub>EN</sub> = 2.3V,              | SGM61280-3.3      | 100  | 140  | 180  | - μΑ  |

| Quiescent Current into VIN       | lα                             | no switching                         | SGM61280-5.1      | 100  | 136  | 180  |       |

| Under-Voltage Lockout            |                                |                                      |                   |      |      |      |       |

| Under-Voltage Lockout Threshold  | Vuvlo                          | SGM61280-3.3, rising                 | g V <sub>IN</sub> |      |      | 4.6  | v     |

| Under-Voltage Lockout Threshold  | V UVLO                         | SGM61280-5.1, rising V <sub>IN</sub> |                   |      |      | 5.5  | v     |

| Under-Voltage Lockout Hysteresis | $V_{\text{UVLO}_{\text{HYS}}}$ |                                      |                   |      | 0.2  |      | V     |

| Logic Input Threshold            |                                |                                      |                   |      | -    | -    | _     |

| EN Input Low Threshold           | $V_{\text{EN}_{L}}$            | Shutdown                             |                   |      |      | 0.4  | V     |

| EN Input High Threshold          | $V_{\text{EN}_{\text{H}}}$     | Enabled                              |                   | 0.8  |      |      | V     |

| Allow Audio Avoid Mode           | V <sub>EN_H1</sub>             | Anti-Sound mode                      | SGM61280-3.3      |      |      | 1.6  | v     |

|                                  | VEN_H1                         | Anti-Sound mode                      | SGM61280-5.1      |      |      | 1.55 | v     |

| Do not Allow Audio Avoid Mode    | $V_{\text{EN}\_\text{H2}}$     | Normal mode                          |                   | 2.3  |      |      | V     |

| Output Voltage                   |                                |                                      |                   |      |      |      |       |

| Output Voltage                   | Vout                           | SGM61280-3.3                         |                   | 3.18 | 3.3  | 3.42 | v     |

| Output Voltage                   | VOUT                           | SGM61280-5.1                         |                   | 4.85 | 5.05 | 5.25 | v     |

| VCC Regulator Voltage            | Vcc                            | Internal regulator                   |                   | 5.2  | 5.6  | 6    | V     |

| Discharge Pull Down Resistance   | R <sub>DIS</sub>               | $V_{EN} = 0V$                        |                   | 33   | 55   | 73   | Ω     |

| Soft-Start                       |                                |                                      |                   |      |      |      |       |

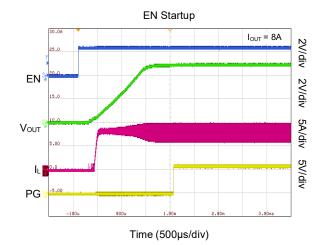

| Coft Start Time                  |                                | From EN rising to                    | SGM61280-3.3      | 1.15 | 1.9  | 2.6  | ms    |

| Soft-Start Time                  | tss                            | PG Release to High                   | SGM61280-5.1      | 1.20 | 1.9  | 2.9  |       |

| Output Rising Time               | +_                             | VOUT rising from 10%                 | SGM61280-3.3      |      | 0.6  |      | ms    |

|                                  | t <sub>R</sub>                 | to 90%                               | SGM61280-5.1      |      | 0.8  |      |       |

| Power Switch                     |                                |                                      |                   |      |      |      |       |

| High-side Switch On-Resistance   | R <sub>ON_HS</sub>             |                                      |                   | 14   | 21   | 26   | mΩ    |

| Low-side Switch On-Resistance    | Ron LS                         | SGM61280-3.3                         |                   | 4    | 6    | 9    |       |

|                                  | NON_LS                         | SGM61280-5.1                         |                   | 4    | 7    | 9    | mΩ    |

| Current Limit                    |                                |                                      |                   |      |      |      |       |

| Low-side Switch Current Limit    |                                | SGM61280-3.3                         |                   | 8    | 12.6 | 17   | ۸     |

|                                  | ILIM_LS                        | SGM61280-5.1                         |                   | 8    | 11.6 | 17   | A     |

| Switching Frequency              |                                |                                      |                   |      |      |      |       |

| PW/M Switching Frequency         | f                              | h ava = 84                           | SGM61280-3.3      | 400  | 470  | 530  | г⊔⊸   |

| PWM Switching Frequency          | f <sub>sw</sub>                | $I_{LOAD} = 8A$                      | SGM61280-5.1      | 600  | 720  | 800  | - kHz |

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>IN</sub> = 12V, typical values are measured at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                       | SYMBOL                 | CONDITIONS                   |              | MIN | ТҮР  | MAX | UNITS |  |

|---------------------------------|------------------------|------------------------------|--------------|-----|------|-----|-------|--|

| Timer Control                   | •                      |                              |              |     |      | •   |       |  |

|                                 |                        |                              | SGM61280-3.3 |     | 85   |     |       |  |

| Minimum On-Time                 | t <sub>on_min</sub>    | $V_{IN} = V_{IN}MAX$         | SGM61280-5.1 |     | 92   |     | ns    |  |

| Minimum Off Time                |                        | SGM61280-3.3                 |              | 105 | 178  | 240 |       |  |

| Minimum Off-Time                | t <sub>OFF_MIN</sub>   | SGM61280-5.1                 |              | 105 | 173  | 240 | ns    |  |

| Audio Avoid Mode (AAM)          | ·                      |                              |              |     |      |     |       |  |

| Operation Period                | t <sub>ASMD</sub>      |                              |              |     | 29   |     | μs    |  |

| Output Over-Voltage Protection  |                        |                              |              |     |      |     |       |  |

| Output Over-Voltage Threshold   | V <sub>TH_OVP</sub>    | V <sub>OUT</sub> % (rising)  |              | 115 | 121  | 127 | %     |  |

| Output Over-Voltage Hysteresis  | OVP <sub>HYS</sub>     | V <sub>OUT</sub> %           |              |     | 5    |     | %     |  |

| Output Over-Voltage Delay Time  | t <sub>ovp_dly</sub>   |                              |              |     | 20   |     | μs    |  |

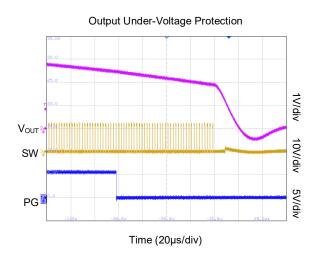

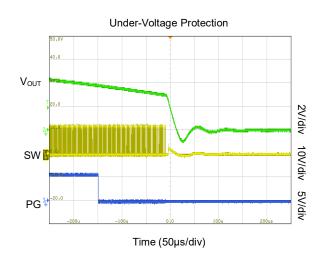

| Output Under-Voltage Protection |                        |                              |              |     |      |     |       |  |

| Output Under-Voltage Threshold  | $V_{\text{TH\_UVP}}$   | V <sub>FB</sub> % (falling)  |              | 54  | 62   | 70  | %     |  |

| Output Under-Voltage Delay Time | tuvp_dly               | FB forced below UV threshold |              |     | 20   |     | μs    |  |

| UVP Blanking Time               | t <sub>uvp_blank</sub> | From EN_HTH                  |              |     | 1.9  |     | ms    |  |

| Power Good                      |                        |                              |              |     |      |     |       |  |

| PG Threshold                    | PG <sub>TH_LtoH</sub>  | V <sub>OUT</sub> % (rising)  |              | 85  | 91   | 97  | %     |  |

| PG Hysteresis                   | PG <sub>HYS</sub>      |                              |              |     | 15   |     | %     |  |

| PG Delay Time                   | tpg_dly                | PG from low to hig           | gh           |     | 10   |     | μs    |  |

| LDO Regulator                   | ·                      |                              |              |     |      |     |       |  |

| LDO Output Voltage              | Maria                  | SGM61280-3.3                 |              |     | 3.3  |     | v     |  |

| LDO Output voltage              | VLD03                  | SGM61280-5.1                 |              |     | 5.0  |     | v     |  |

| LDO Dropout Voltago             | Vdropout               | SGM61280-3.3                 |              |     | 154  |     | mV    |  |

| LDO Dropout Voltage             | V DROPOUT              | SGM61280-5.1                 |              |     | 146  |     | IIIV  |  |

| LDO Output Current Limit        | ILIM_LDO               |                              |              | 150 |      |     | mA    |  |

|                                 | Б                      | SGM61280-3.3                 |              |     | 1.67 |     | 0     |  |

| Bypass MOS RON                  | Ron_bp                 | SGM61280-5.1                 |              |     | 1.2  |     | Ω     |  |

| Thermal Protection              |                        |                              |              |     |      |     |       |  |

| OTD Shutdown Threshold          |                        | SGM61280-3.3                 |              |     | 154  |     | - °C  |  |

| OTP Shutdown Threshold          | T <sub>SD</sub>        | SGM61280-5.1                 |              |     | 159  |     |       |  |

|                                 | т                      | SGM61280-3.3                 |              |     | 19   |     | °C    |  |

| OTP Hysteresis                  | T <sub>HYS</sub>       | SGM61280-5.1                 |              |     | 22   |     | °C    |  |

### SGM61280

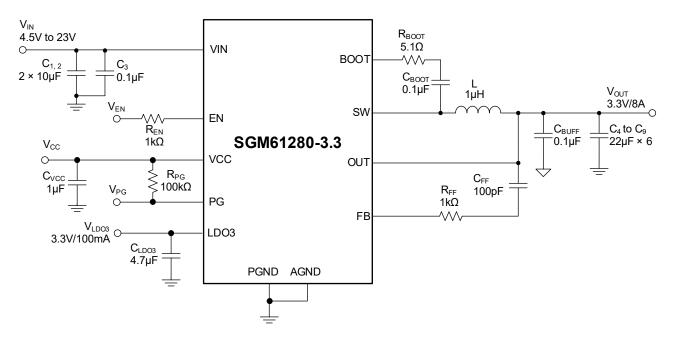

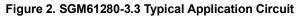

# **TYPICAL APPLICATION CIRCUITS**

### SGM61280

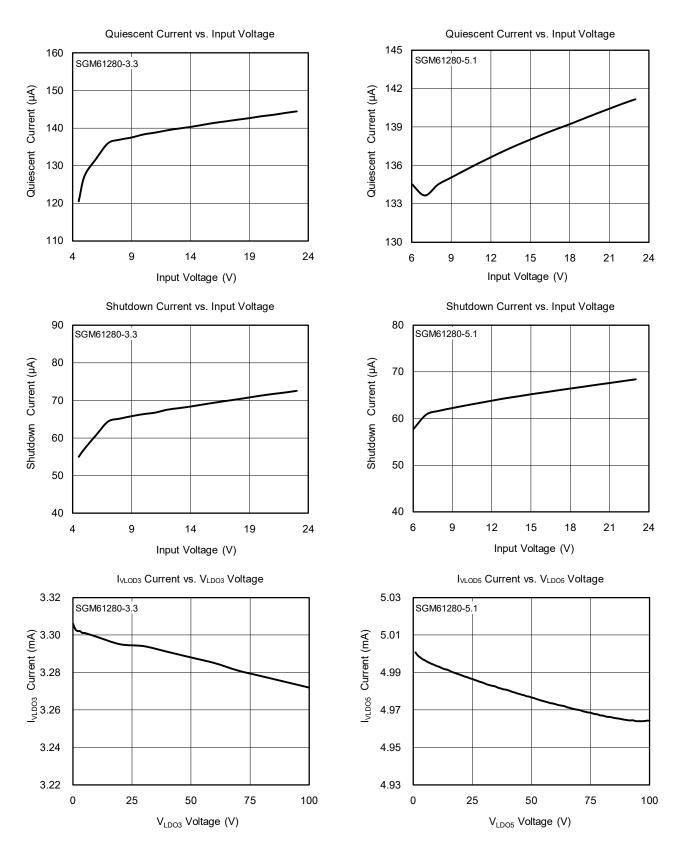

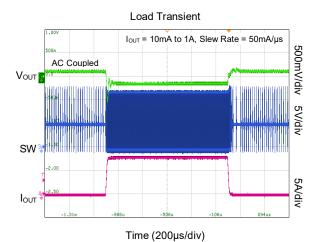

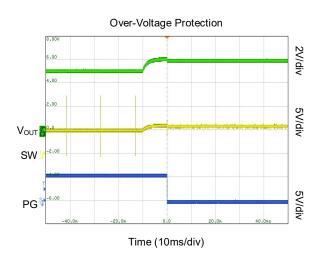

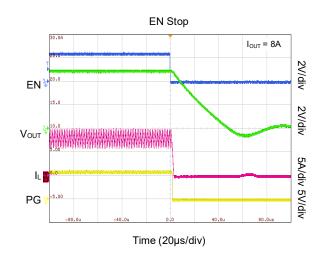

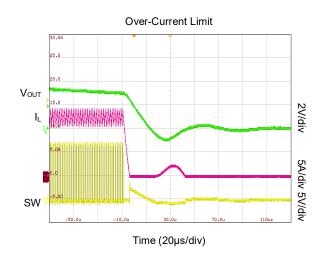

## **TYPICAL PERFORMANCE CHARACTERISTICS**

SG Micro Corp

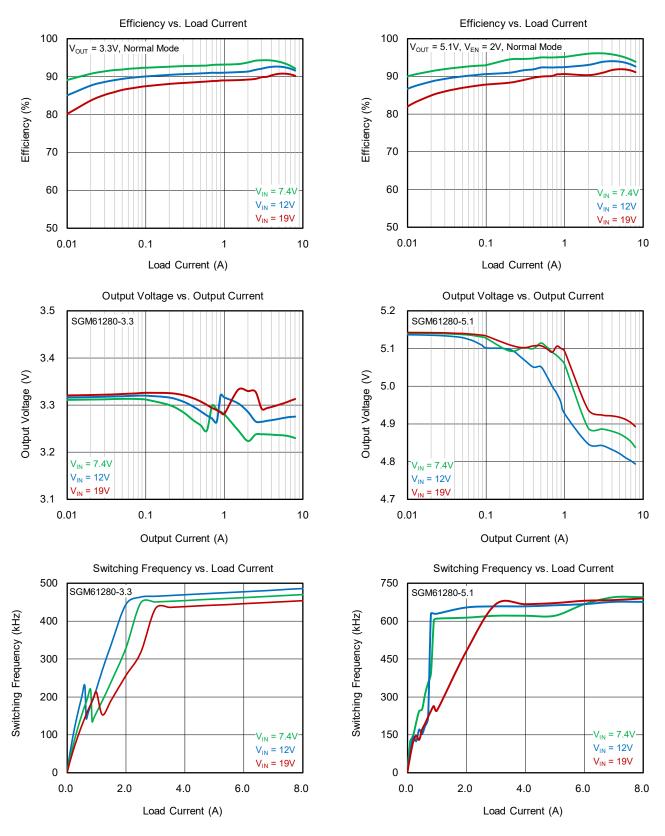

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

SG Micro Corp

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

SGM61280-3.3 only, unless otherwise noted.

SG Micro Corp

### SGM61280

### 8A, 23V, Synchronous Buck Converters with 3.3V/5V LDO

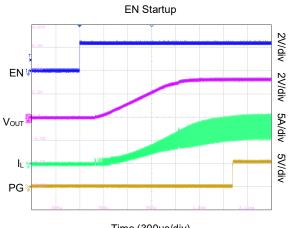

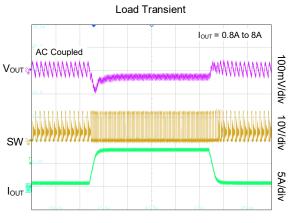

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

SGM61280-5.1 only,  $V_{IN}$  = 12V,  $V_{OUT}$  = 5.1V, unless otherwise noted.

SG Micro Corp

### SGM61280

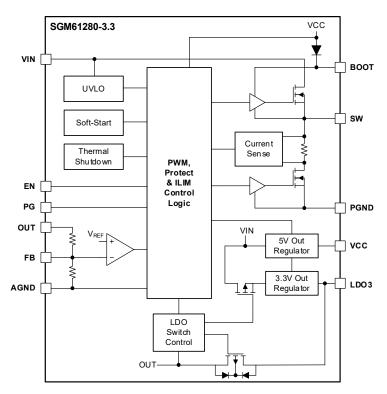

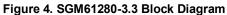

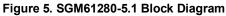

### FUNCTIONAL BLOCK DIAGRAM

### **DETAILED DESCRIPTION**

#### Overview

The SGM61280 is a wide input voltage synchronous Buck converter with constant on-time (COT) control and integrated low R<sub>DSON</sub> power MOSFETs. The COT control loop allows stable operation and fast transient response even with low ESR output ceramic capacitors and no complicated external compensation. It can deliver 8A output current due to its integrated synchronous buck converter with low R<sub>DSON</sub> switches. The V<sub>IN</sub> input range for SGM61280-3.3 is from 4.5V to 23V and for SGM61280-5.1 is from 5.1V to 23V.

The proprietary technology used in the COT control for this device, provides excellent load and line regulation and very fast transient response along with high flexibility.

Transient response is almost instantaneous because the COT is not clock-based unlike other methods using clocked PWM where the loop reacts to the events in the next clock cycles. Therefore, the inductor current reacts to deviations immediately to keep the output in regulation.

This device can employ both low ESR (like POSCAP or SP-CAP) and ultra-low ESR ceramic capacitors for output capacitance.

A linear regulator with 100mA output capacity is provided in the device (3.3V for the SGM61280-3.3 and 5.0V for the SGM61280-5.1). If  $V_{OUT}$  exceeds 3.1V (for 3.3V) or 4.7V (for 5.0V), the regulator source will automatically switch from the input ( $V_{IN}$ ) to the output ( $V_{OUT}$ ) through OUT pin to minimize the losses.

#### Under-Voltage Lockout (UVLO)

The input voltage  $(V_{IN})$  is continuously monitored and if it falls below the under-voltage lockout falling threshold, the device will shut down. The UVLO is necessary to avoid device malfunction due to low supply voltage such as insufficient gate voltage for turning the power switches to fully on-state.

The UVLO is non-latching and if  $V_{IN}$  exceeds the under-voltage lockout rising threshold (if EN is logic high), device will exit shutdown and resume switching.

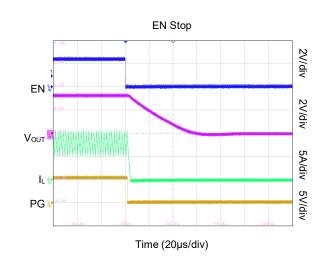

#### Enable Input (EN)

The active-high EN input pin can be used to enable or shutdown the device and to allow the audio avoid mode (AAM). If EN is a logic low voltage (below 0.4V), device will shut down. If EN is a logic high (above 0.8V) and  $V_{IN} > V_{UVLO}$ , the device will be enabled.

This pin is also used to activate the audio avoid mode (AAM) to prevent audio noise at light loads. If the EN voltage is in the 0.6V to 1.9V range, the device is allowed to enter AAM during light load PFM to prevent acoustic noise.

The LDOx output and VCC are in on-state as long as  $V_{\rm IN}$  >  $V_{\rm UVLO}.$  See Table 1 for the SGM61280 power logic.

#### Table 1. SGM61280 Regulator States vs. EN Input

| Device              | EN   | VCC | Vout     | LDOx |

|---------------------|------|-----|----------|------|

| SGM61280-3.3        | High | ON  | Enabled  | ON   |

| and<br>SGM61280-5.1 | Low  | ON  | Disabled | ON   |

#### Bootstrap Circuit (CBOOT and RBOOT)

The high-side (HS) switch gate driver needs a voltage higher than  $V_{IN}$  to turn on the gate of the high-side N-MOSFET switch (for example,  $5V + V_{IN}$  or higher). The external bootstrap capacitor ( $C_{BOOT}$ ) is used to provide this higher voltage for supplying the HS gate driver.  $C_{BOOT}$  is charged through the internal bootstrap diode from VCC when the low-side (LS) switch turns on and SW node is at around 0V. When the LS switch turns off and HS switch turns on, the SW voltage will rise to the  $V_{IN}$  rail voltage and the  $C_{BOOT}$  voltage will supply the HS driver.

Refer to Figure 2 and Figure 3 for  $C_{BOOT}$  and  $R_{BOOT}$  combinations. Use a 0.1µF ceramic capacitor ( $C_{BOOT}$ ) with lower ESR and a series 5.1 $\Omega$  resistor ( $R_{BOOT}$ ) between the BOOT and the SW pins for bootstrapping.

The  $R_{BOOT}$  helps to control the turn-on time of the HS switch and is good to compromise the switching loss and the EMI radiation. The gate driver is designed for fast turn-on and minimal switching loss (that is, for good efficiency). But the additional resistance of the  $R_{BOOT}$  can slow down the turn-on (V<sub>SW</sub> rising) to reduce the EMI at the expense of small increase in the switching loss due to the longer turn-on time of the HS switch.

## **DETAILED DESCRIPTION (continued)**

#### Soft-Start

An internal 1.9ms (TYP) soft-start ramp circuit is implemented to gradually increase the PWM reference voltage for output regulation, in order to limit the startup inrush current from the source and to prevent unwanted over-current protection trips during power-up. This timer starts when EN goes high (if  $V_{IN} > V_{UVLO}$ ) or when  $V_{IN}$  exceeds the under-voltage lockout rising threshold if EN is already high.

#### VCC and LDO3/LDO5 (Linear Regulators)

VCC regulator is powered from VIN to power the internal circuitry and the gate drivers. It should be decoupled with a  $1\mu F$  ceramic capacitor close to the device.

The LDO3 (3.3V) or LDO5 (5.0V) can deliver 100mA to external loads. The LDO should be decoupled with at least 4.7 $\mu$ F ceramic capacitor. When V<sub>OUT</sub> exceeds above 3.1V (SGM61280-3.3) or 4.7V (SGM61280-5.1), the source of the LDO will automatically switch from VIN to OUT by an internal MOSFET to minimize LDO losses.

#### Power Good Indicator Output (PG)

The PG pin is an open-drain output with a pull-up resistor which will go to logic high if the output voltage is near its expected value. It is recommended to connect a  $100k\Omega$  pull-up resistor to a high rail which is not larger than 5V. V<sub>PG</sub> will be pulled low, if V<sub>OUT</sub> drops below 91% (TYP) of its nominal value and will go high if it exceeds 97% of the nominal regulation value.

PG is held low during soft-start state. To avoid false signaling, PG responds with a  $10\mu$ s delay and changes state if at the end of this delay, the new state is still valid.

#### **Output Over/Under-Voltage Protection**

An over-voltage protection (OVP) is triggered if the  $V_{OUT}$  exceeds the over-voltage threshold (above regulation) for about 20µs or longer. Upon OVP trip, the HS switch remains off and the LS switch remains on until the inductor current drops to zero and then the device will shut down.

Output voltage is also protected against under-voltage protection (UVP). If the output voltage falls and remains below the under-voltage threshold for about  $20\mu$ s, the device will shut down.

After OVP or UVP, the device will shut down in latch-off mode and will not restart automatically. An EN toggle or  $V_{IN}$  power cycling is needed to restart the device.

### Pulse Frequency Modulation Mode (PFM)

In light loads, the SGM61280 can enter the PFM mode to keep the efficiency high. Light load condition is detected at the CCM and DCM boundary condition in which inductor valley current reaches to zero due to the output current drop.

In PFM, upon detection of zero inductor current, the LS switch turns off and the output capacitor will take longer time to discharge ( $t_{OFF}$  extends) until the  $V_{OUT}$  (or  $V_{FB}$ ) drops to the level needed to begin a new cycle (HS turn on or  $t_{ON}$  pulse).

#### Audio Avoid Mode (AAM)

To avoid acoustic noise when the PFM frequency drops below audible range (20kHz), the AAM can be activated by bringing the EN voltage between 0.6V and 1.9V. In this mode, a special diode emulation mode will be activated to keep the minimum switching period to about 30µs (about 33.3kHz), which is called audio avoid mode. This mode can keep the switching frequency above the hearing range even in no load condition.

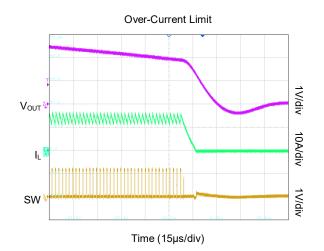

#### **Output Current Limit (OCP)**

cycle-by-cycle valley current А detection is implemented to limit the output current. During TOFF portion of each cycle (in which LS is conducting), the current of the synchronous rectifier (LS switch) is monitored by measuring its drain-to-source voltage that is proportional to its current. This measurement is temperature compensated for better accuracy. If the valley current exceeds the threshold, the one-shot timer that produces the constant on-time (for the t<sub>ON</sub> period) will be disabled and not allowed until the inductor current, which is going through LS during toFF, drops below the valley current limit. During current limiting, the output voltage will drop because the required load current is not supplied by the inductor. If the output voltage drops below the output UVP level (see Output Over/Under-Voltage Protection section), the device will shut down and stop switching to avoid over temperature.

#### **Thermal Shutdown**

The die temperature (T<sub>J</sub>) is constantly monitored for over-temperature protection (OTP). If T<sub>J</sub> exceeds the T<sub>SD</sub> threshold (+154°C, TYP for SGM61280-3.3 and +159°C, TYP for SGM61280-5.1), the device shuts down to avoid damage. OTP is a latch-off mode protection and an EN toggle or V<sub>IN</sub> power cycling is needed to restart the device.

### **APPLICATION INFORMATION**

#### **Typical Application**

The schematic of a typical application circuit that is used for SGM61280-3.3 evaluation module is given in Figure 3.

Figure 6. SGM61280-3.3 Typical Application Circuit

#### **Input Capacitor Selection**

For the input capacitor selection, SGM61280 requires high-quality ceramic decoupling capacitors, such as X5R or X7R or similar. These types of capacitors are commonly used for power regulator capacitors due to their stable dielectric material, which results in less capacitance variation and greater temperature stability. When choosing the input capacitors, the voltage rating of capacitor should have a safe margin from maximum input voltage. Choosing an input capacitor with a voltage rating 1.5 times higher than the maximum input voltage is a safe design practice. The input RMS current can be calculated by Equation 1:

$$I_{\rm RMS} = \sqrt{\frac{V_{\rm OUT}}{V_{\rm IN}}} \times \left[ \left( 1 - \frac{V_{\rm OUT}}{V_{\rm IN}} \right) \times I_{\rm OUT}^2 + \frac{\Delta I_{\rm L}^2}{12} \right]$$

(1)

To select a suitable capacitor for the RMS current rating, it is recommended to use multiple capacitors with low Equivalent Series Resistance (ESR) in parallel to form a capacitor bank. Therefore, two  $10\mu$ F low ESR capacitors are placed at the input. The input ripple voltage can be calculated by Equation 2:

$$\Delta V_{IN} = \frac{I_{OUT} \times V_{OUT}}{C_{IN} \times f_{SW} \times V_{OUT}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(2)

#### Inductor

When selecting an inductor, it is important to specify both the inductance and the peak current required. Inductor selection is usually flexible, and depending on the tradeoff between size, cost, and circuit efficiency. Lower inductor values can reduce size and cost, and

improve transient response. However, the inductor ripple current and output voltage ripple are increased, and the efficiency is also reduced due to the higher peak current. In contrast, higher inductance values result in higher efficiency, but at the cost of increased physical size or increased resistance due to the need for more turns of wire. In addition, the transient response will be slower due to the additional time it takes to change the current in the inductor. The approximate inductor value can be calculated by using Equation 3:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times \Delta I_{L}}$$

(3)

With the selected inductor value, the ripple current ( $\Delta I_L$ ) and the corresponding peak inductor current  $I_{L_PEAK}$  can be calculated using Equation 4 and Equation 5:

$$\Delta I_{L} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times L}$$

(4)

$$I_{L_PEAK} = I_{OUT_MAX} + \frac{\Delta I_{L}}{2}$$

(5)

where,

$I_{OUT\_MAX}$  is the maximum load current. To ensure the full-load range requirement, the saturation current rating ( $I_{SAT}$ ) must be larger than the  $I_{L\_PEAK}$ . To achieve optimal efficiency, select an inductor with low DC resistance that meets size and cost requirements. An inductor with a shielded ferrite core is the best choice for the application, which minimizes the core losses and causes fewer EMI and noise issues.

## **APPLICATION INFORMATION (continued)**

#### **Output Capacitor Selection**

To achieve the best performance, ceramic capacitors are recommended to be used at the output. The capacitance should be chosen based on the desired output ripple level and the transient response, including over-shoot and undershoot during the load transient.

In a Buck converter, the output ripple is mainly caused by the inductor current ripple and its effect on the output capacitor ESR and storage charge, which are called ESR ripple and capacitance ripple, respectively. Due to the extremely low ESR and relatively small capacitance of ceramic capacitors, the amplitudes of the two types of ripple are similar. In applications where ripple performance is important, both ESR ripple and capacitive ripple should be considered.

$$V_{\text{RIPPLE}} = V_{\text{RIPPLE}\_\text{ESR}} + V_{\text{RIPPLE}\_\text{C}}$$

(6)

$$V_{\text{RIPPLE}\_\text{ESR}} = \Delta I_{\text{L}} \times + R_{\text{ESR}}$$

(7)

$$V_{\text{RIPPLE}_{C}} = \frac{\Delta I_{L}}{8 \times C_{\text{OUT}}} \times f_{\text{SW}}$$

(8)

In most applications, transient response is usually the more stringent criterion. The output capacitor must either supply the increased load current or absorb the excess inductor current (as the load current decreases) until the control loop can readjust the inductor current to the new load level. Typically, COT structure has a very fast transient response and small output transients.

However, under some application conditions, such as at low output voltages and low duty cycles, the use of small ceramic capacitors increases the magnitude of output voltage variation when the load changes fast. The following section describes the calculation of worst-case voltage variations in response to very fast load steps.

The following function is to calculate the ESR step:

$$V_{\text{ESR}_{\text{STEP}}} = \Delta I_{\text{OUT}} \times R_{\text{ESR}}$$

(9)

The magnitude of the capacitive undershoot on positive load steps (sag) is determined by various factors, including the load step, the capacitance of the output capacitor, the inductance value, the voltage difference between the input and output, and the maximum duty cycle. The maximum duty cycle in a quick transition is influenced by the on-time and minimum off-time because the COT control method increases current by spacing out on-times with minimal off-times as fast as possible. To find the estimated on-time (ignoring parasitic effects) and maximum duty cycle for a specific input and output voltage, following Equations can be used:

$$t_{\rm oN} = \frac{V_{\rm OUT}}{V_{\rm IN} \times f_{\rm SW}}$$

(10)

$$D_{MAX} = \frac{t_{ON}}{t_{ON} + t_{OFF\_MIN}}$$

(11)

The effective on-time duration may be slightly extended as the integrated circuit adjusts for voltage reductions within the circuit. However, these adjustments can be disregarded as the on-time duration is increased to account for the voltage losses. The output voltage sag can be determined by calculating it as Equation 12:

$$V_{sag} = \frac{L \times (\Delta I_{OUT})^2}{2 \times C_{OUT} \times V_{IN\_MAX} \times D_{MAX} - V_{OUT}}$$

(12)

The magnitude of the capacitive overshoot on negative load steps (soar) is determined by the load step, the capacitance of the output capacitor, the inductance value, and the output voltage, as shown in Equation 13:

$$V_{\text{soar}} = \frac{L \times (\Delta I_{\text{OUT}})^2}{2 \times C_{\text{OUT}} \times V_{\text{OUT}}}$$

(13)

Many applications typically do not encounter immediate full-load changes, and the integrated circuit's high switching frequency and rapid transient response can effectively manage voltage regulation under all circumstances. However, in scenarios involving low-voltage CPU cores or DDR memory supply applications, especially devices operating at high clock frequencies and rapidly switching between sleep modes, voltage sag or soar can cause problems. In such cases, mitigating excessive voltage transients can be achieved by either increasing the quantity of ceramic output capacitors or incorporating additional bulk capacitance. For applications characterized by significant rapid transients, it is advisable to calculate over-shoot and undershoot to ensure that over-voltage protection and under-voltage protection mechanisms are not triggered.

### **APPLICATION INFORMATION (continued)**

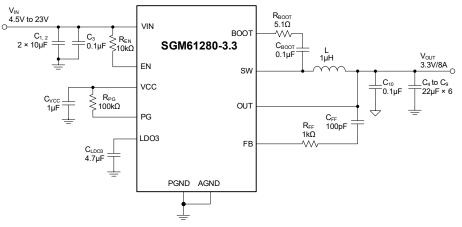

#### Feed-Forward Capacitor C<sub>FF</sub> Design

To enhance adaptability and performance of the SGM61280. а feed-forward capacitor CFF is incorporated into the feedback loop of the integrated compensator within the IC. The purpose of adding a feed-forward loop is to improve the transient response by modifying the gain and phase characteristics. Adding C<sub>FF</sub> in the feedback network forms a new zero and a high-frequency pole in the loop, which results in increased gain and phase at mid-frequencies, thereby extending the bandwidth and enhancing phase margin. In addition, the pole reduces high-frequency noise. These properties enable SGM61280 to obtain faster response during load transients.

Figure 7. Feedback Loop with Feed-Forward Capacitor

The transfer function of the feed-forward network, the positions of the zero and the pole can be determined by the following three Equations:

$$\frac{V_{FB}(s)}{V_{OUT}(s)} = \frac{1}{1 + \frac{R_1}{R_2}} \times \frac{\frac{1 + \frac{s}{R_1}}{R_1}}{\frac{s}{(R_1//R_2) \times C_{FF}}}$$

(14)

$$f_{P} = \frac{1}{2\pi \times (R_{1}/R_{2}) \times C_{FF}}$$

(15)

$$f_z = \frac{1}{2\pi \times R_1 \times C_{FF}}$$

(16)

where,

$R_1$  and  $R_2$  are internal dividing resistors of the SGM61280. The peak value of the phase boost after the introduction of  $C_{FF}$  can be expressed by the following function:

$$f_{\rm PH MAX} = \sqrt{f_{\rm Z} \times f_{\rm P}}$$

(17)

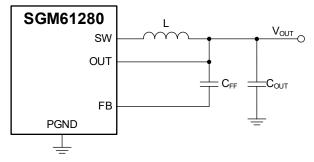

In order to achieve the maximum phase boost, the original bandwidth of the system must be at the maximum phase boost frequency. Therefore, to choose the appropriate feed-forward capacitance, it is necessary to determine the original bandwidth position of the system. The bandwidth of the converter is approximated by observing the voltage deviation frequency during the load step of the converter, as shown in Figure 5.

Figure 8. A Simply Way to Get the BW

Then, the Equation between the bandwidth and the feed-forward  $C_{FF}$  can be expressed as following:

$$\mathsf{BW} = \sqrt{\frac{1}{2\pi \times \mathsf{R}_{1} \times \mathsf{C}_{\mathsf{FF}}} \times \frac{1}{2\pi \times \mathsf{C}_{\mathsf{FF}}} \left(\frac{1}{\mathsf{R}_{1}} + \frac{1}{\mathsf{R}_{2}}\right)} \quad (18)$$

The C<sub>FF</sub> can be obtained by calculating as Equation 19:

$$C_{FF} = \frac{1}{2\pi \times BW} \sqrt{\frac{1}{R_1} \left(\frac{1}{R_1} + \frac{1}{R_2}\right)}$$

(19)

It is important to note that the introduction of feed-forward capacitor could inject bias voltage to the  $V_{OUT}$ , which could lead to the deviation of  $V_{OUT}$ . If the output value exceeds the specification value, the  $C_{FF}$  value needs to be decreased. The internal dividing resistors of the SGM61280 are shown in Table 2.

#### Table 2. Internal Dividing Resistors for SGM61280-3.3

| Resistor       | SGM61280-3.3 |

|----------------|--------------|

| R <sub>1</sub> | 180kΩ        |

| R <sub>2</sub> | 40kΩ         |

# LAYOUT INFORMATION

Designing a good PCB layout has a significant impact on the performance of a switching power supply. For the SGM61280, the layout design can be more critical due to the high switching frequency, high output current and more sensitivity of the COT controllers to the noise. One of the goals of a good layout is to minimize the EMI radiations and the influence (coupling) of the switching noise on the sensitive feedback routes. The voltage gradients induced on the ground planes or other sensitive routes should be minimized to avoid switching instability and deviation from regulation point.

The following layout guidelines are recommended to get the best performance from the SGM61280.

- Consider short, straight, and wide copper traces for the main current paths.

- Place the input capacitor and the output capacitor close to the device with the shortest possible connection traces.

- Keep the SW node area minimal. Also keep this node and the components directly connected to it away from sensitive copper traces and feedback elements (such as FB and OUT pins). Avoid using vias for SW node and make it thick and short for high current.

- Along with the SW, the PGND pin serves as a main heatsinking path. Connect PGND to a large ground plane and stitch it with thermal vias to ground planes on the other layers and specifically to the back side of the PCB for heat sinking and noise reduction.

- Feedback route must be wide and away from the SW node. The input of the 100mA LDO is supplied directly from the OUT feedback line.

- For less parasitic inductance, use multiple vias under the device close to VIN, PGND and the decoupling capacitors pads.

Figure 9. Top Layer of SGM61280-3.3

### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DECEMBER 2024 – REV.A.1 to REV.A.2              | Page |

|-------------------------------------------------|------|

| Added SGM61280-5.1 information                  |      |

| NOVEMBER 2024 – REV.A to REV.A.1                | Page |

| Updated tape and reel information               |      |

| Changes from Original (MARCH 2024) to REV.A     | Page |

| Changed from product preview to production data | All  |

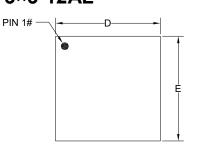

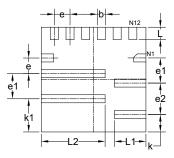

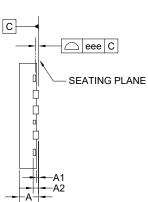

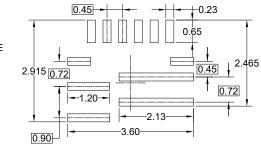

# PACKAGE OUTLINE DIMENSIONS UTQFN-3×3-12AL

#### **TOP VIEW**

#### **BOTTOM VIEW**

SIDE VIEW

#### RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Di          | mensions In Millimet | ers   |  |  |  |  |

|--------|-------------|----------------------|-------|--|--|--|--|

| Symbol | MIN         | NOM                  | МАХ   |  |  |  |  |

| A      | 0.510 0.550 |                      | 0.600 |  |  |  |  |

| A1     | 0.000       | -                    | 0.050 |  |  |  |  |

| A2     |             | 0.152 REF            |       |  |  |  |  |

| b      | 0.180       | 0.230                | 0.280 |  |  |  |  |

| D      | 2.900       | 2.900 3.000          |       |  |  |  |  |

| E      | 2.900       | 3.000                | 3.100 |  |  |  |  |

| е      | 0.450 BSC   |                      |       |  |  |  |  |

| e1     |             | 0.720 BSC            |       |  |  |  |  |

| e2     |             | 0.900 BSC            |       |  |  |  |  |

| k      |             | 0.500 REF            |       |  |  |  |  |

| k1     |             | 0.950 REF            |       |  |  |  |  |

| L      | 0.250       | 0.350                | 0.450 |  |  |  |  |

| L1     | 0.800 0.900 |                      | 1.000 |  |  |  |  |

| L2     | 1.730       | 1.930                |       |  |  |  |  |

| eee    | -           | 0.080                | -     |  |  |  |  |

NOTE: This drawing is subject to change without notice.

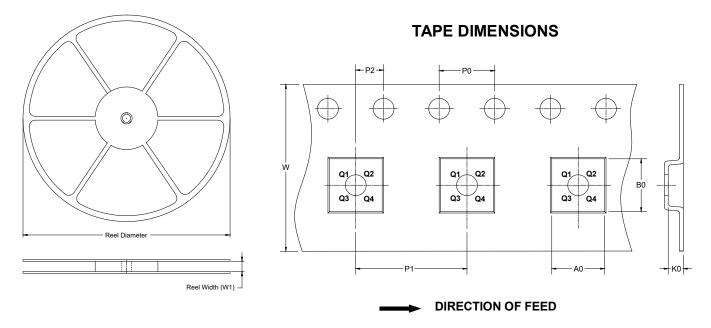

# TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type   | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| UTQFN-3×3-12AL | 7"               | 12.4                     | 3.30       | 3.30       | 0.80       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

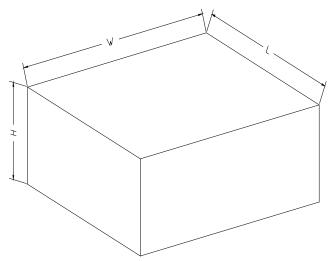

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton | ]      |

|-------------|----------------|---------------|----------------|--------------|--------|

| 7" (Option) | 368            | 227           | 224            | 8            |        |

| 7"          | 442            | 410           | 224            | 18           | DD0002 |