## **GENERAL DESCRIPTION**

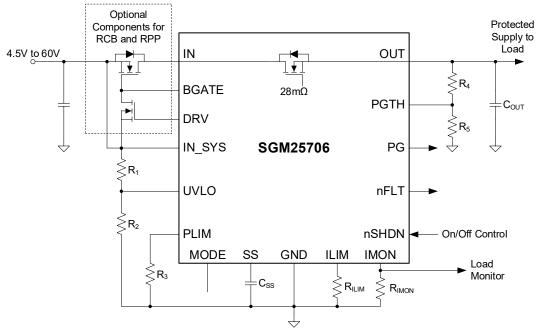

The SGM25706 is a feature-rich 60V, 6A eFuse integrated with a  $28m\Omega$  on-resistance MOSFET. The device provides a BGATE pin to drive an external N-MOSFET which can be connected with the internal MOSFET for reverse current blocking (RCB) and input reverse polarity protection (RPP). Besides, the provides SGM25706 other functions such as under-voltage lockout (UVLO), over-voltage protection (OVP), adjustable over-current protection (OCP), fast short-circuit protection (SCP) and adjustable output slew rate control.

The SGM25706 provides fault indicator (nFLT) pin and accurate load current monitor for system monitoring and downstream load management. Besides, the power good (PG) pin can be used to control the downstream converters. The MODE pin allows the user to configure the device response under current limit faults (latch-off or auto-retry).

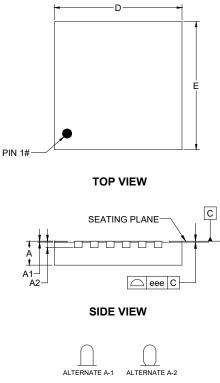

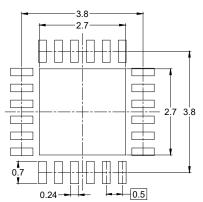

The SGM25706 is available in a Green TQFN-4×4-24L package.

# APPLICATIONS

Industrial Automation and Control Motor Drivers System Circuit Breakers

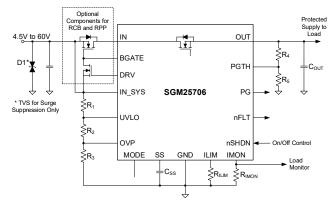

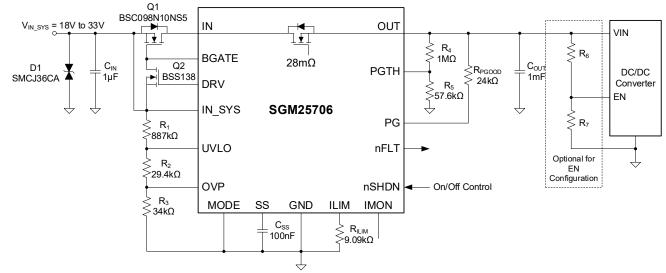

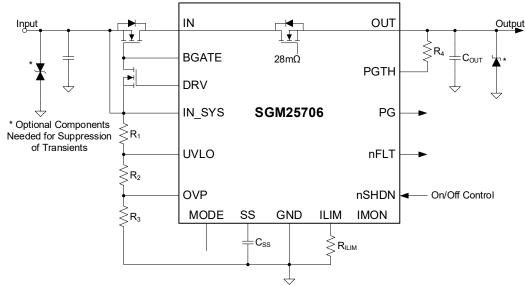

## **TYPICAL APPLICATION**

Figure 1. Typical Application Circuit

## FEATURES

- 4.5V to 60V Operating Voltage, 67V Absolute Maximum

- Integrated 60V, 28mΩ On-Resistance MOSFET

- Support Reverse Polarity Protection (RPP) and Reverse Current Blocking (RCB) with an External N-MOSFET

- 0.6A to 6A Adjustable Current Limit

- Fast Reverse Current Blocking: 0.183µs

- Adjustable Output Power Limiting Variants

- Adjustable UVLO, OVLO, Output Slew Rate Control for Inrush Current Control

- Able to Drive Large and Unknown Capacitive Loads by Employing Thermal Regulation during Device Power-Up

- Variants with 34.7V and 38.4V Maximum Over-Voltage Clamp

- Power Good Indicator (PG)

- Selectable Options for Over-Current Fault Response Offering a Choice between Auto-Retry and Latch-Off

- Variants with 2 × Pulse Over-Current Support

- Analog Current Monitor (IMON) Output

- Available in a Green TQFN-4×4-24L Package

## 60V, 6A Power Limiting, Surge Protection Industrial eFuse

## **PACKAGE/ORDERING INFORMATION**

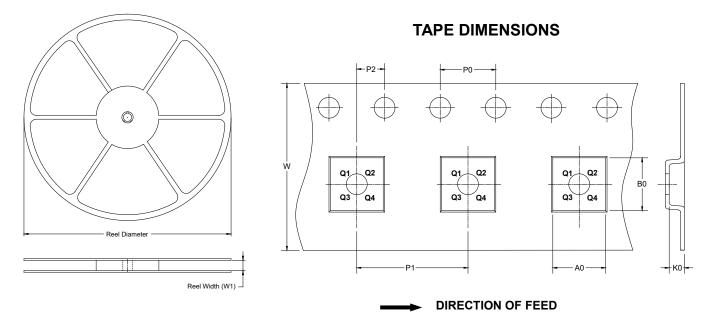

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER  | PACKAGE<br>MARKING        | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|---------------------|---------------------------|---------------------|

| SGM25706A | TQFN-4×4-24L           | -40°C to +125°C                   | SGM25706AXTQF24G/TR | SGM169<br>XTQF24<br>XXXXX | Tape and Reel, 3000 |

| SGM25706B | TQFN-4×4-24L           | -40°C to +125°C                   | SGM25706BXTQF24G/TR | SGM16A<br>XTQF24<br>XXXXX | Tape and Reel, 3000 |

| SGM25706C | TQFN-4×4-24L           | -40°C to +125°C                   | SGM25706CXTQF24G/TR | SGM16B<br>XTQF24<br>XXXXX | Tape and Reel, 3000 |

| SGM25706D | TQFN-4×4-24L           | -40°C to +125°C                   | SGM25706DXTQF24G/TR | SGM16C<br>XTQF24<br>XXXXX | Tape and Reel, 3000 |

| SGM25706E | TQFN-4×4-24L           | -40°C to +125°C                   | SGM25706EXTQF24G/TR | SGM0NI<br>XTQF24<br>XXXXX | Tape and Reel, 3000 |

## MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

| X | Х | Х | Х | Х |  |

|---|---|---|---|---|--|

|   |   |   |   |   |  |

└── Vendor Code

Trace Code

— Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

## **DEVICE COMPARISON TABLE**

| Model     | Over-Voltage Protection               | Overload Fault Response                               | Adjustable Output<br>Power Limiting |

|-----------|---------------------------------------|-------------------------------------------------------|-------------------------------------|

| SGM25706A | Over-Voltage Cut-Off, Adjustable      | Active Current Limit (1 ×)                            | No                                  |

| SGM25706B | Over-voltage Cut-Oli, Aujustable      | Active Current Limit with Pulse Current Support (2 ×) | No                                  |

| SGM25706C | Over Veltere Clemp Fixed 24 7V (MAX)  | Active Current Limit (1 ×)                            | Yes                                 |

| SGM25706D | Over-Voltage Clamp, Fixed 34.7V (MAX) | Active Current Limit with Pulse Current Support (2 ×) | Yes                                 |

| SGM25706E | Over-Voltage Clamp, Fixed 38.4V (MAX) | Active Current Limit with Pulse Current Support (2 ×) | Yes                                 |

## DEVICE OPERATIONAL VARIATIONS WITH DIFFERENT MODE CONFIGURATIONS

| Model                                 | MODE Pin Configuration | Overload Protection Operation                                                                                                                                                                                                                                                       |

|---------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SGM25706A,<br>SGM25706C               | Oren                   | Active current limit at $1 \times I_{OL}$ for a maximum duration of $t_{CL\_PLIM\_DLY}$ , then latches off. Reset the device by setting the nSHDN from low to high, UVLO from low to high, or power cycling IN_SYS.                                                                 |

| SGM25706B,<br>SGM25706D,<br>SGM25706E | Open                   | Active current limit at $2 \times I_{OL}$ for $t_{CB_DLY}$ followed with current limit at $1 \times I_{OL}$ for a maximum duration of $t_{CL_PLIM_DLY}$ , then latches off. Reset the device by setting the nSHDN from low to high, UVLO from low to high, or power cycling IN SYS. |

| SGM25706A,<br>SGM25706C               |                        | Active current limit at 1 × $I_{OL}$ for a maximum duration of $t_{CL_PLIM_DLY}$ , then auto retries after a delay of $t_{TSD}$ RETRY.                                                                                                                                              |

| SGM25706B,<br>SGM25706D,<br>SGM25706E | Shorted to GND         | Active current limit at 2 × $I_{OL}$ for $t_{CB_DLY}$ followed with current limit at 1 × $I_{OL}$ for a maximum duration of $t_{CL_PLIM_DLY}$ , then auto retries after a delay of $t_{TSD_RETRY}$ .                                                                                |

#### **ABSOLUTE MAXIMUM RATINGS**

#### Input Voltage

| IN_SYS                                          | 60V to 67V           |

|-------------------------------------------------|----------------------|

| IN_SYS (10ms Transient), T <sub>A</sub> = +25°C | 60V to 75V           |

| IN, OUT, UVLO, nFLT, PG, PGTH                   | 0.3V to 67V          |

| IN_SYS - OUT (10ms Transient), with a BI        | ocking MOSFET        |

|                                                 | ≥ -85V               |

| IN (10ms Transient), T <sub>A</sub> = +25°C     | 0.3V to 75V          |

| BGATE                                           | 60V to 81V           |

| BGATE - IN_SYS                                  | 0.3V to 15V          |

| DRV                                             | 60V to 72V           |

| DRV - IN_SYS                                    | 0.3V to 7.5V         |

| OVP, SS, IMON, MODE, nSHDN, ILIM, PL            | -IM                  |

|                                                 | 0.3V to 5.5V         |

| Sink Current                                    |                      |

| Inflt, Iss, Ipg                                 | 10mA                 |

| Source Current                                  |                      |

| ISS, IILIM, IPLIM, IMODE, INSHDN                | . Internally Limited |

| Package Thermal Resistance                      |                      |

| TQFN-4×4-24L, θ <sub>JA</sub>                   | 36.7°C/W             |

| TQFN-4×4-24L, θ <sub>JB</sub>                   | 15.5°C/W             |

| TQFN-4×4-24L, θ <sub>JC (TOP)</sub>             | 26.2°C/W             |

| TQFN-4×4-24L, θ <sub>JC (BOT)</sub>             | 12.4°C/W             |

| Junction Temperature                            | +150°C               |

| Storage Temperature Range                       | 65°C to +150°C       |

| Load Tomporature (Coldaring 10a)                |                      |

| Lead Temperature (Soldering, 10s)               | +260°C               |

| ESD Susceptibility <sup>(1) (2)</sup>           | +260°C               |

|                                                 |                      |

| ESD Susceptibility <sup>(1) (2)</sup>           | ±2000V               |

1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

### **RECOMMENDED OPERATING CONDITIONS**

| Input Voltage                        |                 |

|--------------------------------------|-----------------|

| IN_SYS, IN                           | 4.5V to 60V     |

| OUT, UVLO, PGTH, PG, nFLT            | 0V to 60V       |

| OVP, SS, IMON, MODE                  | 0V to 4V        |

| nSHDN                                | 0V to 5V        |

| Resistance                           |                 |

| ILIM                                 | 3kΩ to 30kΩ     |

| IMON                                 | ≥ 1kΩ           |

| PLIM                                 | 60.4kΩ to 150kΩ |

| External Capacitance                 |                 |

| IN, IN_SYS, OUT                      | ≥ 0.1µF         |

| SS                                   | ≥ 10nF          |

| Operating Junction Temperature Range | -40°C to +125°C |

## **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

## 60V, 6A Power Limiting, Surge Protection Industrial eFuse

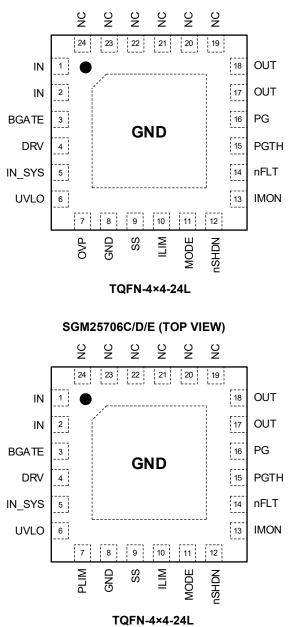

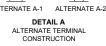

## **PIN CONFIGURATIONS**

SGM25706A/B (TOP VIEW)

## **PIN DESCRIPTION**

| PIN                       | NAME   | TYPE | FUNCTION                                                                                                                                                                                                                                                                                               |

|---------------------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2                      | IN     | Р    | Device Power Input.                                                                                                                                                                                                                                                                                    |

| 3                         | BGATE  | 0    | Gate Driver Output for External Blocking MOSFET. Connect this pin to the external MOSFET GATE. If the external MOSFET is not used, float this pin.                                                                                                                                                     |

| 4                         | DRV    | 0    | Gate Driver Output for Fast Pull-Down Switch MOSFET. Connect this pin to the external pull-down switch GATE. If the external MOSFET is not used, float this pin.                                                                                                                                       |

| 5                         | IN_SYS | Р    | Power Input and Supply Voltage of the Device. Connect this pin to the external MOSFET<br>source if the MOSFET is used. If the external MOSFET is not used, short IN_SYS pin to IN<br>pin.                                                                                                              |

| 6                         | UVLO   | I    | Under-Voltage Lockout Setting Pin. An under-voltage event on this pin turns off the internal MOSFET and asserts the nFLT pin. Tie this pin to GND for selecting the internal default threshold.                                                                                                        |

| 7                         | OVP    | I    | Over-Voltage Protection Threshold Setting Pin. (For SGM25706A/B Only). An over-voltage<br>event on this pin turns off the internal MOSFET and asserts the nFLT pin. Tie the UVLO pin<br>to GND for selecting the internal default threshold.                                                           |

| 7                         | PLIM   | I    | Output Power Limit Threshold Setting Pin. (For SGM25706C/D/E Only). Connect this pin to GND through a resistor to set the output power limit. If the output power limit feature is not used, connect this pin to GND.                                                                                  |

| 8                         | GND    | —    | Device Ground. Connect this pin to System Ground.                                                                                                                                                                                                                                                      |

| 9                         | SS     | I/O  | Soft-Start Pin. Place a capacitor from this pin to GND to set the output voltage slew rate.                                                                                                                                                                                                            |

| 10                        | ILIM   | I/O  | Current Limit Programming Pin. Place a resistor from this pin to GND to set the over-current and short-circuit current limit.                                                                                                                                                                          |

| 11                        | MODE   | I    | Over-Current Fault Response Mode Selection Pin.                                                                                                                                                                                                                                                        |

| 12                        | nSHDN  | I    | Device Shutdown Pin (Active Low). Pulling this pin low activates the low power shutdown mode. Cycle this pin to reset the device that has latched off due to a fault condition.                                                                                                                        |

| 13                        | IMON   | ο    | Current Monitor Pin. The sourcing current of this pin is proportional to the MOSFET current.<br>Placing a resistor from this pin to GND transforms the current to voltage signal. If not used,<br>float this pin.                                                                                      |

| 14                        | nFLT   | 0    | Fault Event Indicator with an Open-Drain Structure. If this pin is not used, float the pin or tie it to GND.                                                                                                                                                                                           |

| 15                        | PGTH   | I    | Power Good Comparator Input.                                                                                                                                                                                                                                                                           |

| 16                        | PG     | 0    | Power Good Indicator (Active High). This pin is asserted high when the voltage at PGTH has reached the $V_{PGTHR}$ threshold and the internal MOSFET is fully turned on. This pin goes low when $V_{PGTH}$ drops below $V_{PGTHF}$ threshold. If this pin is not used, float the pin or tie it to GND. |

| 17, 18                    | OUT    | Ρ    | Device Power Output.                                                                                                                                                                                                                                                                                   |

| 19, 20, 21, 22,<br>23, 24 | NC     | _    | No Connection.                                                                                                                                                                                                                                                                                         |

| Exposed<br>Pad            | GND    | —    | The GND terminal must be connected to the exposed pad, which needs to be connected through numerous vias to a PCB ground plane for effective thermal performance.                                                                                                                                      |

NOTE: P = power, I = input, O = output, I/O = input/output.

# **ELECTRICAL CHARACTERISTICS**

$(T_J = -40^{\circ}C \text{ to } +125^{\circ}C, V_{IN\_SYS} = V_{IN} = 4.5V \text{ to } 60V, V_{nSHDN} = 2V, R_{ILIM} = 30k\Omega$ , IMON = PG = nFLT = open, C<sub>SS</sub> = open. All voltages are with respect to GND, unless otherwise noted.)

| PARAMETER                                     | SYMBOL                        | CONDITIONS                                                                | MIN   | TYP                 | MAX   | UNITS |

|-----------------------------------------------|-------------------------------|---------------------------------------------------------------------------|-------|---------------------|-------|-------|

| Supply Voltage                                |                               |                                                                           |       |                     |       |       |

| Operating Input Voltage                       | V <sub>IN_SYS</sub>           |                                                                           | 4.5   |                     | 60    | V     |

|                                               | I <sub>Q ON</sub>             | Enabled: V <sub>nSHDN</sub> = 2V, V <sub>UVLO</sub> = 2V                  |       | 280                 | 430   |       |

| Supply Current                                |                               | $V_{nSHDN} = 2V, V_{UVLO} = 1V$                                           |       | 58                  | 130   | μA    |

|                                               | I <sub>Q_OFF</sub>            | $V_{nSHDN} = 0V, V_{UVLO} = 0V$                                           |       | 19                  | 50    | 1     |

| Ground Current during Reverse Polarity        | I <sub>GND</sub>              | $V_{IN_SYS}$ = -24V, $V_{IN}$ = floating, $V_{OUT}$ = 0V                  |       | 0.6                 | 1.6   | mA    |

|                                               | N                             | V <sub>IN_SYS</sub> > 35V, SGM25706C/D only                               | 31.7  | 33.2                | 34.7  | V     |

| Over-Voltage Clamp                            | Vovc                          | V <sub>IN_SYS</sub> > 40V, SGM25706E only                                 | 35.6  | 37                  | 38.4  | V     |

| Under-Voltage Lockout (UVLO) Input            |                               |                                                                           |       |                     |       |       |

| Factory Set V <sub>IN SYS</sub> Under-Voltage | V                             | V <sub>IN_SYS</sub> rising, V <sub>UVLO</sub> = 0V                        | 15    | 15.38               | 15.8  | V     |

| Trip Level                                    | V <sub>INSYS_UVLO</sub>       | V <sub>IN_SYS</sub> falling, V <sub>UVLO</sub> = 0V                       | 14    | 14.45               | 14.9  | V     |

| Internal UVLO Select Threshold                | V <sub>SEL_UVLO</sub>         |                                                                           | 190   | 212                 | 230   | mV    |

| UVLO Threshold Voltage, Rising                | V <sub>UVLOR</sub>            |                                                                           | 1.163 | 1.2                 | 1.229 | V     |

| UVLO Threshold Voltage, Falling               | VUVLOF                        |                                                                           | 1.094 | 1.122               | 1.146 | V     |

| UVLO Input Leakage Current                    | I <sub>UVLO</sub>             | $V_{UVLO} = 0V$ to $60V$                                                  | -150  | 10                  | 150   | nA    |

| Over-Voltage Protection (OVP) Input           |                               |                                                                           |       |                     |       |       |

| Factory Set V <sub>IN SYS</sub> Over-Voltage  | V                             | $V_{IN\_SYS}$ rising, $V_{OVP} = 0V$                                      | 33.1  | 34.16               | 35.2  | V     |

| Trip Level                                    | V <sub>IN_SYS_OVP</sub>       | $V_{IN\_SYS}$ falling, $V_{OVP}$ = 0V                                     | 32.6  | 33.67               | 34.7  | V     |

| Internal OVP Select Threshold                 | $V_{\text{SEL}_{\text{OVP}}}$ |                                                                           | 190   | 212                 | 230   | mV    |

| Over-Voltage Threshold Voltage, Rising        | V <sub>OVPR</sub>             |                                                                           | 1.163 | 1.2                 | 1.229 | V     |

| Over-Voltage Threshold Voltage, Falling       | VOVPF                         |                                                                           | 1.094 | 1.122               | 1.146 | V     |

| OVP Input Leakage Current                     | I <sub>OVP</sub>              | $V_{OVP} = 0V \text{ to } 4V$                                             | -150  | 0                   | 150   | nA    |

| Current Limit Programming (ILIM)              |                               |                                                                           |       |                     |       |       |

|                                               | I <sub>OL</sub>               | $R_{ILIM} = 30k\Omega$ , $V_{IN} - V_{OUT} = 1V$ , $V_{IN\_SYS} = 24V$    | 0.47  | 0.59                | 0.71  | Α     |

| Overload Current Limit                        |                               | $R_{ILIM} = 9k\Omega$ , $V_{IN} - V_{OUT} = 1V$ , $V_{IN_{SYS}} = 24V$    | 1.78  | 2                   | 2.18  | Α     |

|                                               | IOL                           | $R_{ILIM} = 4.02k\Omega$ , $V_{IN} - V_{OUT} = 1V$ , $V_{IN_{SYS}} = 24V$ | 4.22  | 4.5                 | 4.77  | A     |

|                                               |                               | $R_{ILIM} = 3k\Omega$ , $V_{IN} - V_{OUT} = 1V$ , $V_{IN}_{SYS} = 24V$    | 5.59  | 6                   | 6.55  | Α     |

| Transient Pulse Over-Current Limit            | I <sub>OL_Pulse</sub>         | $R_{ILIM} = 3k\Omega$ to $30k\Omega$ , SGM25706B/D/E only                 |       | 2 × I <sub>OL</sub> |       | Α     |

| Fast-Trip Comparator Threshold                | IFASTTRIP                     | SGM25706A/C                                                               |       | 2 × I <sub>OL</sub> |       | A     |

|                                               | PASTIRE                       | SGM25706B/D/E only                                                        |       | 3 × I <sub>OL</sub> |       | Α     |

| Short-Circuit Protect Current                 | I <sub>SCP</sub>              |                                                                           |       | 37                  |       | A     |

| Output Power Limiting Control (PLIM)          | nput: SGM                     | 25706C/D/E Only                                                           |       | •                   |       |       |

| Power Limit Feature Select Threshold          | $V_{\text{SEL}\_\text{PLIM}}$ |                                                                           | 190   | 212                 | 230   | mV    |

| PLIM Sourcing Current                         | I <sub>PLIM</sub>             | V <sub>PLIM</sub> = 0V                                                    | 3.9   | 4.97                | 6     | μA    |

|                                               |                               | $R_{PLIM} = 60.4k\Omega, T_J = +25^{\circ}C$                              | 59    | 63                  | 67.5  |       |

|                                               |                               | $R_{PLIM} = 60.4 k\Omega$ , $T_{J} = -40^{\circ}C$ to $+125^{\circ}C$     | 49    | 63                  | 77.3  |       |

| Max Output Power                              | P <sub>PLIM</sub>             | $R_{PLIM} = 100k\Omega, T_J = +25^{\circ}C$                               | 104   | 110                 | 115   | W     |

|                                               | I PLIM                        | $R_{PLIM} = 100k\Omega$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$         | 88    | 110                 | 132   |       |

|                                               |                               | $R_{PLIM} = 150 k\Omega, T_J = +25^{\circ}C$                              | 154   | 180                 | 212   |       |

|                                               |                               | $R_{PLIM} = 150k\Omega$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$         | 130   | 180                 | 235   |       |

| BGATE (Blocking MOSFET Gate Driver            | )                             |                                                                           |       |                     |       |       |

| BGATE Clamp Voltage                           | V <sub>BGATE</sub>            | V <sub>BGATE</sub> - V <sub>IN_SYS</sub> , V <sub>IN_SYS</sub> = 24V      | 9     | 10.08               | 11    | V     |

| Blocking MOSFET Gate Drive Current            | I <sub>BGATE</sub>            | V <sub>BGATE</sub> - V <sub>IN_SYS</sub> = 1V                             | 16.3  | 19.61               | 22.7  | μA    |

| BGATE Pull-Down Resistance <sup>(1)</sup>     | $R_{PD\_BGATE}$               |                                                                           | 500   | 843                 | 1150  | kΩ    |

| DRV Logic High Level                          | V <sub>DRV_OH</sub>           | V <sub>DRV</sub> - V <sub>IN SYS</sub> , V <sub>IN SYS</sub> = 24V        | 3     | 4.71                | 5.2   | V     |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(T_J = -40^{\circ}C \text{ to } +125^{\circ}C, V_{IN_SYS} = V_{IN} = 4.5V \text{ to } 60V, V_{nSHDN} = 2V, R_{ILIM} = 30k\Omega$ , IMON = PG = nFLT = open, C<sub>SS</sub> = open. All voltages are with respect to GND, unless otherwise noted.)

| PARAMETER                                                                                    | SYMBOL               | CONDITIONS                                                                   | MIN   | TYP       | MAX   | UNITS |

|----------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------|-------|-----------|-------|-------|

| Pass MOSFET Output (OUT)                                                                     |                      |                                                                              |       |           |       |       |

|                                                                                              |                      | I <sub>OUT</sub> = 2A, T <sub>J</sub> = +25°C                                | 23    | 27.64     | 33.5  |       |

| N to OUT Total On-Resistance                                                                 | R <sub>DSON</sub>    | $I_{OUT} = 2A, T_J = -40^{\circ}C \text{ to } +85^{\circ}C$                  |       | 27.64     | 44    | mΩ    |

|                                                                                              |                      | I <sub>OUT</sub> = 2A, T <sub>J</sub> = -40°C to +125°C                      |       | 27.64     | 52    |       |

| OUT Leakage during Input Supply<br>Brownout                                                  | I <sub>LKGOUT</sub>  | $V_{IN_SYS} = 0V, V_{OUT} = 24V, V_{IN} = floating, V_{nSHDN} = 2V, sinking$ | -30   |           |       | μΑ    |

| V <sub>IN_SYS</sub> - V <sub>OUT</sub> Rising Threshold for Revers<br>Protection Comparator  | e V <sub>REVTH</sub> |                                                                              | -20   | -14       | -9    | mV    |

| V <sub>IN_SYS</sub> - V <sub>OUT</sub> Falling Threshold for Revers<br>Protection Comparator | e V <sub>FWDTH</sub> | V <sub>IN_SYS</sub> ≥ 5.0V                                                   | 42    | 58        | 75    | mV    |

| Output Ramp Control (SS)                                                                     |                      |                                                                              |       |           |       |       |

| SS Charging Current                                                                          | I <sub>SS</sub>      | V <sub>SS</sub> = 0V                                                         | 1.43  | 1.96      | 2.47  | μA    |

| SS to OUT Gain                                                                               | GAINss               | $V_{OUT}/V_{SS}$ , $V_{IN_SYS} = 24V$                                        | 24.4  | 25        | 25.5  | V/V   |

| SS Maximum Capacitor Voltage                                                                 | $V_{SS_MAX}$         |                                                                              | 4     | 4.3       | 4.6   | V     |

| SS Discharging Resistance                                                                    | R <sub>ss</sub>      |                                                                              | 11    | 20.3      | 29    | Ω     |

| Low I <sub>Q</sub> Shutdown (nSHDN) Input                                                    |                      | •                                                                            | I     | •         | •     |       |

| Open Circuit Voltage                                                                         | $V_{nSHDN}$          | $I_{nSHDN} = 0.1 \mu A$                                                      | 4.1   | 4.3       | 4.5   | V     |

| nSHDN Threshold Voltage for Low I <sub>Q</sub><br>Shutdown, Falling                          | V <sub>nSHUTF</sub>  |                                                                              | 0.8   |           |       | V     |

| nSHDN Threshold Rising                                                                       | V <sub>nSHUTR</sub>  |                                                                              |       |           | 1.8   | V     |

| Leakage Current                                                                              | I <sub>nSHDN</sub>   | V <sub>nSHDN</sub> = 0V                                                      | -8    |           |       | μA    |

| Current Monitor Output (IMON)                                                                |                      | 1                                                                            |       |           |       |       |

|                                                                                              |                      | I <sub>OUT</sub> = 0.6A, V <sub>IN SYS</sub> = 24V                           | 25.17 | 27.51     | 29.86 |       |

|                                                                                              |                      | I <sub>OUT</sub> = 1A, V <sub>IN_SYS</sub> = 24V                             | 25.7  | 27.7      | 29.7  | μΑ/Α  |

|                                                                                              |                      | I <sub>OUT</sub> = 2A, V <sub>IN SYS</sub> = 24V                             | 26.23 | 27.83     | 29.44 |       |

| Gain Factor I <sub>IMON</sub> :I <sub>OUT</sub>                                              | GAINIMON             | I <sub>OUT</sub> = 3A, V <sub>IN_SYS</sub> = 24V                             | 26.48 | 27.88     | 29.27 |       |

|                                                                                              |                      | $I_{OUT} = 4A, V_{IN SYS} = 24V$                                             | 26.61 | 27.9      | 29.2  | 1     |

|                                                                                              |                      | I <sub>OUT</sub> = 5A, V <sub>IN SYS</sub> = 24V                             | 26.69 | 27.92     | 29.17 | -     |

|                                                                                              |                      | I <sub>OUT</sub> = 6A, V <sub>IN_SYS</sub> = 24V                             | 26.7  | 27.94     | 29.22 |       |

| FAULT FLAG (nFLT): Active-Low                                                                | •                    | •                                                                            | •     | •         | •     |       |

| nFLT Pull-Down Resistance                                                                    | R <sub>nFLT</sub>    |                                                                              | 50    | 79        | 110   | Ω     |

| nFLT Input Leakage Current                                                                   | I <sub>nFLT</sub>    | V <sub>nFLT</sub> = 0V to 60V                                                | -150  | 6         | 150   | nA    |

| Power Good (PG)                                                                              |                      | 1                                                                            |       |           |       |       |

| PG Pull-Down Resistance                                                                      | R <sub>PG</sub>      |                                                                              | 50    | 78        | 110   | Ω     |

| PG Input Leakage Current                                                                     | I <sub>PG</sub>      | V <sub>PG</sub> = 0V to 60V                                                  | -150  | 6         | 150   | nA    |

| Positive Input for Power Good Compar                                                         |                      | •                                                                            |       |           |       |       |

| PGTH Threshold Voltage, Rising                                                               | V <sub>PGTHR</sub>   |                                                                              | 1.163 | 1.2       | 1.229 | V     |

| PGTH Threshold Voltage, Falling                                                              | V <sub>PGTHF</sub>   |                                                                              | 1.094 | 1.122     | 1.146 | V     |

| PGTH Input Leakage Current                                                                   | I <sub>PG</sub>      | V <sub>PGTH</sub> = 0V to 60V                                                | -150  | 6         | 150   | nA    |

| Thermal Protection                                                                           |                      | •                                                                            |       |           |       |       |

| Thermal Regulation Set Point                                                                 | $T_{J\_REG}$         |                                                                              |       | 130       |       | °C    |

| Thermal Shutdown Threshold, Rising                                                           | T <sub>SD</sub>      |                                                                              |       | 167       |       | °C    |

| Thermal Shutdown Hysteresis                                                                  | T <sub>HYS</sub>     |                                                                              |       | 16        |       | °C    |

| MODE                                                                                         |                      | 1                                                                            | 1     | I         | 1     |       |

|                                                                                              |                      | MODE = open                                                                  |       | Latch-Off |       |       |

| Mode Selection                                                                               |                      | MODE = short to GND                                                          |       | Auto-Retr |       |       |

NOTE:

1. Guaranteed by design, not verified in production testing.

## TIMING REQUIREMENTS

$(T_J = -40^{\circ}C \text{ to } +125^{\circ}C, V_{IN\_SYS} = V_{IN} = 4.5V \text{ to } 60V, V_{nSHDN} = 2V, R_{ILIM} = 30k\Omega$ , IMON = PG = nFLT = open, C<sub>SS</sub> = open. All voltages are with respect to GND, unless otherwise noted.)

| PARAMETER                                                                               | SYMBOL                                               | CONDITIONS                                                                                                                         | MIN          | TYP          | MAX          | UNITS            |

|-----------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|------------------|

| UVLO Input (UVLO)                                                                       |                                                      |                                                                                                                                    |              |              |              |                  |

| UVLO Switch Turn-On Delay                                                               | tuvlo_on_dly                                         | UVLO $\uparrow$ (200mV above V <sub>UVLOR</sub> ) to V <sub>OUT</sub> = 200mV with V <sub>PGTH</sub> = low, C <sub>SS</sub> = 10nF |              | 1270         |              | μs               |

| UVLO Switch Turn-On Delay (Fast)                                                        | t <sub>UVLO_ON_FAST_DLY</sub>                        | UVLO $\uparrow$ (200mV above V <sub>UVLOR</sub> ) to V <sub>OUT</sub> = 200mV with V <sub>PGTH</sub> = high                        | 65           | 115          | 210          | μs               |

| UVLO Switch Turn-Off Delay                                                              | $t_{\text{UVLO}_{OFF}_{DLY}}$                        | UVLO $\downarrow$ (100mV below V_{UVLOF}) to nFLT $\downarrow$ 10%                                                                 | 2            | 4            | 7.8          | μs               |

| UVLO to Fault De-assertion Delay                                                        | $t_{\text{UVLO}\_n\text{FLT}\_\text{DLY}}$           | UVLO↑ to nFLT↑ delay                                                                                                               | 560          | 753          | 960          | μs               |

| Over-Voltage Protection Input (OVP)                                                     |                                                      |                                                                                                                                    |              |              |              |                  |

| OVP Switch Turn-Off Delay                                                               | $t_{\text{OVP}_{OFF}_{DLY}}$                         | $OVP\uparrow$ (200mV above $V_{OVPR}$ ) to $nFLT\downarrow$                                                                        | 1            | 2            | 3.4          | μs               |

| OVP Switch Turn-On Delay (Fast)                                                         | $t_{\text{OVP}\_\text{ON}\_\text{FAST}\_\text{DLY}}$ | OVP↓ (100mV below $V_{OVPF}$ ) to $V_{OUT}$ = 200mV with $V_{PGTH}$ = high                                                         | 8.8          | 25           | 52.5         | μs               |

| OVP Switch Disable Delay                                                                | t <sub>ovp_on_dly</sub>                              | $OVP\downarrow$ (100mV below V <sub>OVPF</sub> ) to V <sub>OUT</sub> = 200mV with V <sub>PGTH</sub> = low, C <sub>SS</sub> = 10nF  |              | 368          |              | μs               |

| Maximum Duration in Output Voltage<br>Clamp Operation                                   | t <sub>ovc_dly</sub>                                 | SGM25706C/D/E only                                                                                                                 |              | 170          |              | ms               |

| nFLT Assertion Delay in Output Voltage<br>Clamp Operation                               | $t_{\text{OVC\_nFLT\_DLY}}$                          | SGM25706C/D/E only                                                                                                                 |              | 691          |              | μs               |

| Shutdown Control Input (nSHDN)                                                          |                                                      |                                                                                                                                    |              |              |              |                  |

| Shutdown Entry Delay                                                                    | t <sub>SD_DLY</sub>                                  | nSHDN $\downarrow$ (below V <sub>SHUTF</sub> ) to MOSFET off                                                                       | 1.8          | 4.1          | 5.8          | μs               |

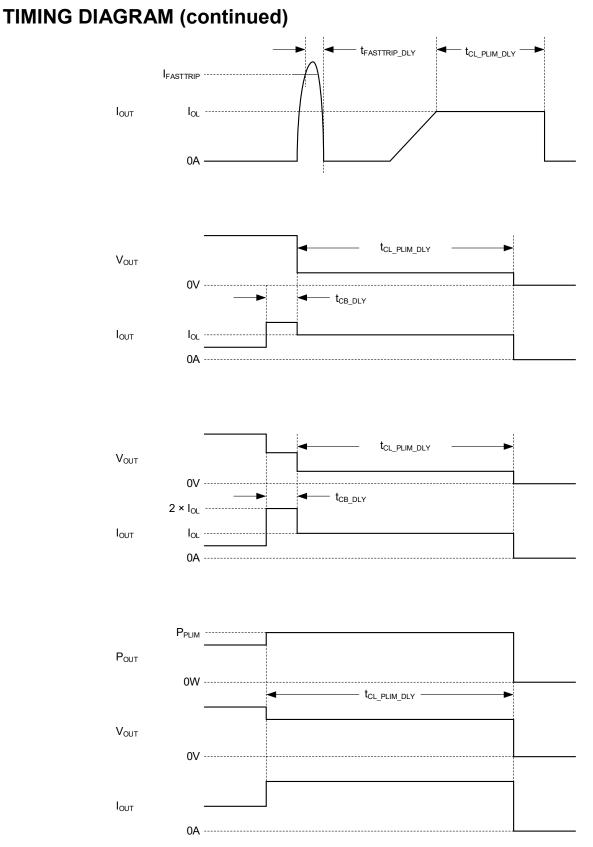

| Current Limit                                                                           |                                                      |                                                                                                                                    |              |              |              |                  |

| Hot-Short Response Time                                                                 | +                                                    | I <sub>OUT</sub> > I <sub>SCP</sub>                                                                                                |              | 0.3          |              | μs               |

| Soft Short Response                                                                     | t <sub>fasttrip_dly</sub>                            | I <sub>FASTTRIP</sub> < I <sub>OUT</sub> < I <sub>SCP</sub>                                                                        |              | 2            |              | μs               |

| nFLT Delay in Current & (Power<br>Limiting: SGM25706C Only)                             |                                                      | Current limiting: SGM25706A/C only                                                                                                 |              | 0.63         | 2.6          | ms               |

| Maximum Duration in 2 × Current<br>Limiting & (Power Limiting:<br>SGM25706D/E Only)     | t <sub>CB_DLY</sub>                                  | $I_{OL} < I_{OUT} \le I_{2xOL}$<br>Current limiting: SGM25706B/D/E only                                                            | 19.5         | 26.3         | 33.5         | ms               |

| Maximum Duration in Current & (Power<br>Limiting: SGM25706C/D/E Only)                   | t <sub>CL_PLIM_DLY</sub>                             |                                                                                                                                    | 125          | 171          | 220          | ms               |

| Retry Delay in Pulse Over-Current<br>Limiting & (Power Limiting:<br>SGM25706C/D/E Only) | t <sub>cbretry_dly</sub>                             | MODE = GND                                                                                                                         | 500          | 682          | 860          | ms               |

| Reverse Current Blocking (RCB) Con                                                      | nparator                                             | · · · · ·                                                                                                                          |              |              |              |                  |

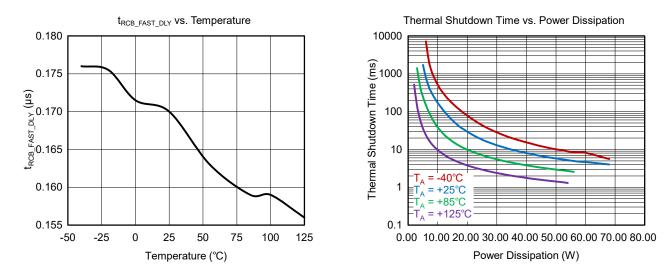

| Reverse Protection Comparator<br>Detection Delay (Reverse)                              | t <sub>RCB_FAST_DLY</sub>                            | $(V_{IN_SYS} - V_{OUT}) \downarrow (1V \text{ overdrive below } V_{REVTH})$ to $V_{DRV} \uparrow$                                  |              | 0.183        | 0.3          | μs               |

| Fault Assertion Delay                                                                   | t <sub>RCB_FLT_DLY</sub>                             | (V <sub>IN_SYS</sub> - V <sub>OUT</sub> )↓ to nFLT↓                                                                                | 470          | 661          | 839          | μs               |

| Reverse Protection Comparator<br>Detection Delay (Forward)                              | t <sub>FWD_FLT_DLY</sub>                             | (V <sub>IN_SYS</sub> - V <sub>OUT</sub> )↑ to V <sub>BGATE</sub> - V <sub>IN_SYS</sub> = 5V,<br>C <sub>BFET-IN SYS</sub> = 4.7nF   |              | 1.33         |              | ms               |

| Fault De-Assertion Delay                                                                |                                                      | (V <sub>IN_SYS</sub> - V <sub>OUT</sub> )↑ to nFLT↑                                                                                | 475          | 767          | 1190         | μs               |

| Output Ramp Control (SS)                                                                |                                                      |                                                                                                                                    |              |              |              |                  |

| Output Ramp Time in Fast Charging                                                       | t <sub>fastcharge</sub>                              | $C_{\text{SS}}$ = open, 10% to 90% $V_{\text{OUT}},$ $C_{\text{OUT}}$ = 1µF, $V_{\text{IN}}$ = 24V                                 | 280          | 418          | 560          | μs               |

| Output Ramp Time                                                                        | t <sub>ss</sub>                                      | $C_{\text{SS}}$ = 22nF, 10% to 90% $V_{\text{OUT}}, V_{\text{IN}}$ = 24V                                                           |              | 8.63         |              | ms               |

| Power Good (PG)                                                                         |                                                      |                                                                                                                                    |              |              |              |                  |

| PG Delay (Deglitch) Time                                                                | t <sub>PG</sub>                                      | Rising edge, PGTH↑ (200mV above V <sub>PGTHR</sub> )<br>Falling edge, PGTH↓ (100mV below V <sub>PGTHF</sub> )                      | 0.96<br>0.96 | 1.35<br>1.58 | 1.71<br>2.51 | ms<br>µs         |

| Fault Flag (nFLT)                                                                       | I                                                    |                                                                                                                                    | 0.30         | 1.00         | 2.01         | ι μ <sub>2</sub> |

| nFLT Assertion Delay in Pulse<br>Over-Current Limiting                                  | t <sub>CB_FLT_DLY</sub>                              | SGM25706B/D/E only                                                                                                                 | 19.5         | 26.3         | 33.5         | ms               |

| Thermal Protection                                                                      | 1                                                    | 11                                                                                                                                 |              | <u> </u>     | 1            | 1                |

| Thermal Shutdown Auto-Retry Interval                                                    | trep percy                                           | MODE = GND                                                                                                                         | 500          | 682          | 860          | ms               |

| Thermal Regulation Timeout                                                              |                                                      |                                                                                                                                    | 500          | 2.77         | 000          | -                |

|                                                                                         | t <sub>TREG_TIMEOUT</sub>                            |                                                                                                                                    |              | 2.11         |              | S                |

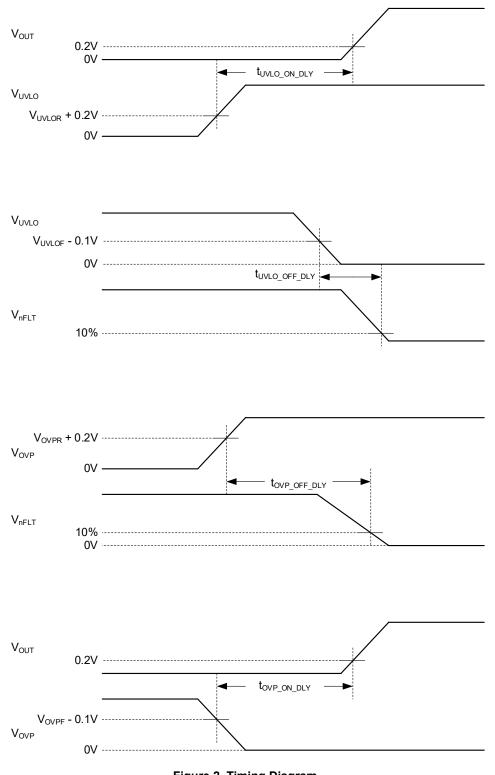

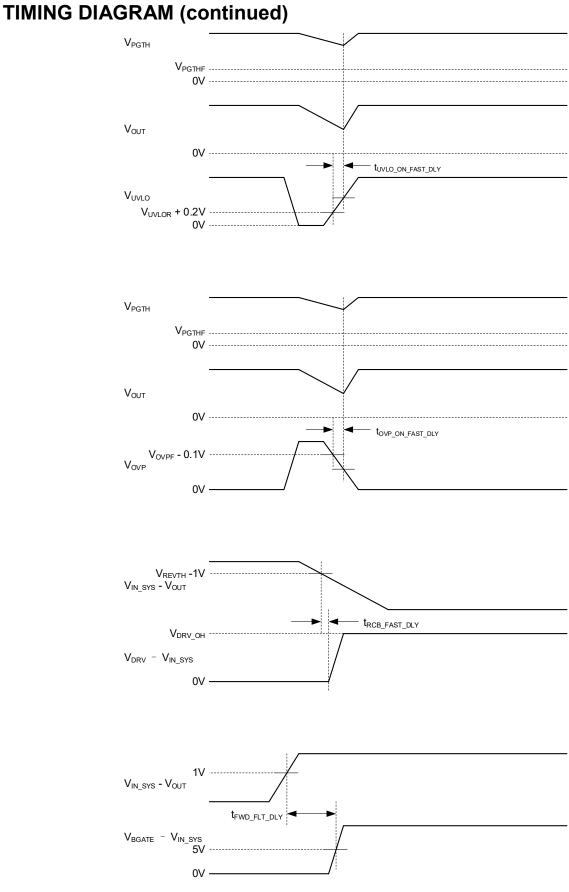

## **TIMING DIAGRAM**

Figure 2. Timing Diagram

Figure 3. Timing Diagram

## **TYPICAL PERFORMANCE CHARACTERISTICS**

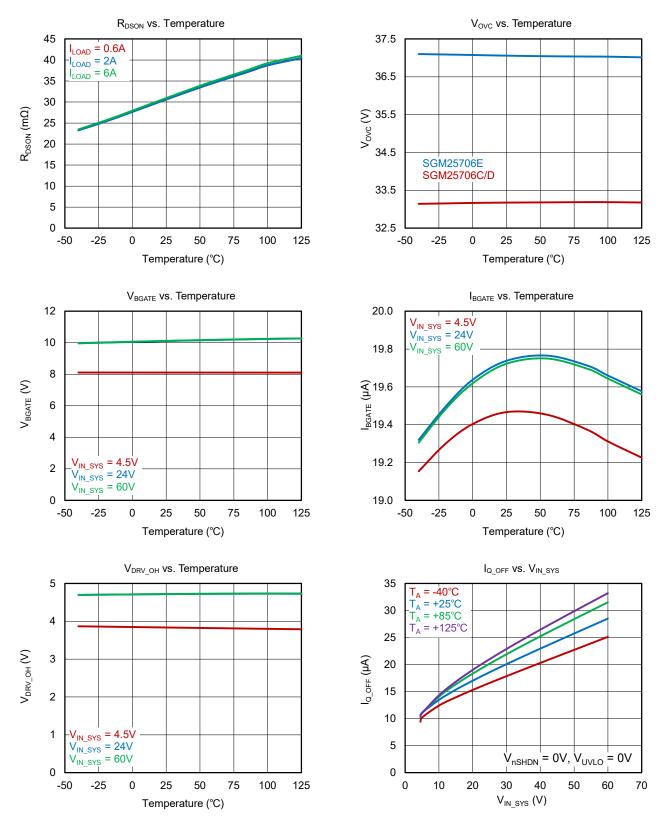

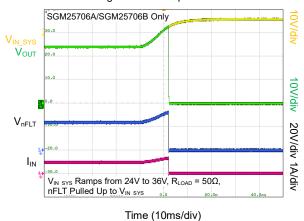

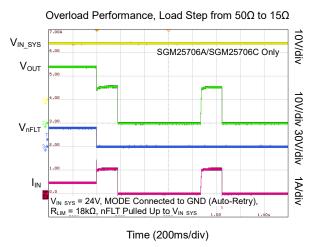

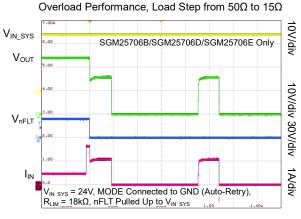

$T_{J} = -40^{\circ}C \text{ to } +125^{\circ}C, V_{IN\_SYS} = V_{IN} = 24V, V_{nSHDN} = 2V, R_{ILIM} = 30k\Omega, IMON = PG = nFLT = C_{SS} = open, unless otherwise noted.$

SG Micro Corp

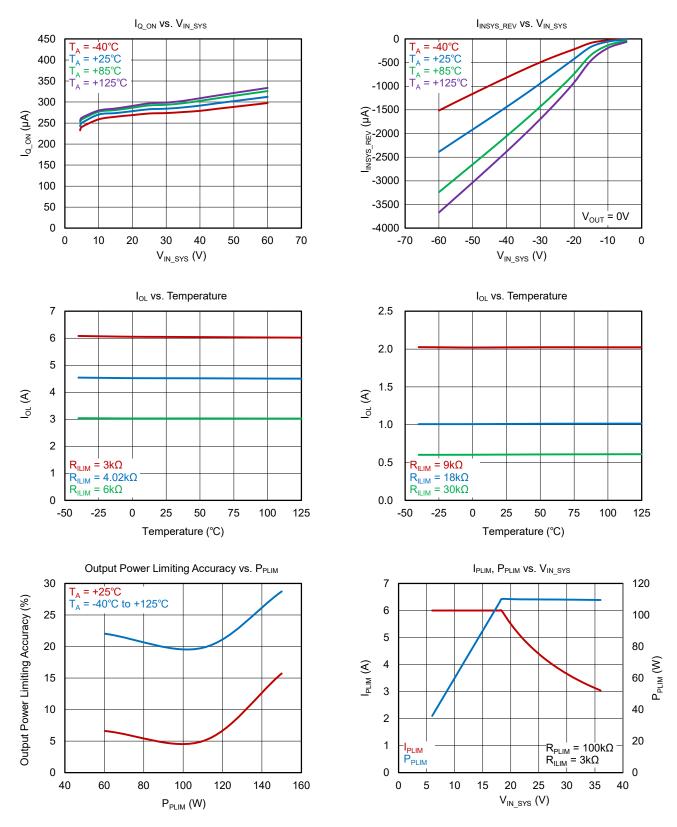

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{IN_SYS} = V_{IN} = 24V$ ,  $V_{nSHDN} = 2V$ ,  $R_{ILIM} = 30k\Omega$ , IMON = PG = nFLT =  $C_{SS}$  = open, unless otherwise noted.

SG Micro Corp

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{IN_SYS} = V_{IN} = 24V$ ,  $V_{nSHDN} = 2V$ ,  $R_{ILIM} = 30k\Omega$ , IMON = PG = nFLT =  $C_{SS}$  = open, unless otherwise noted.

SG Micro Corp

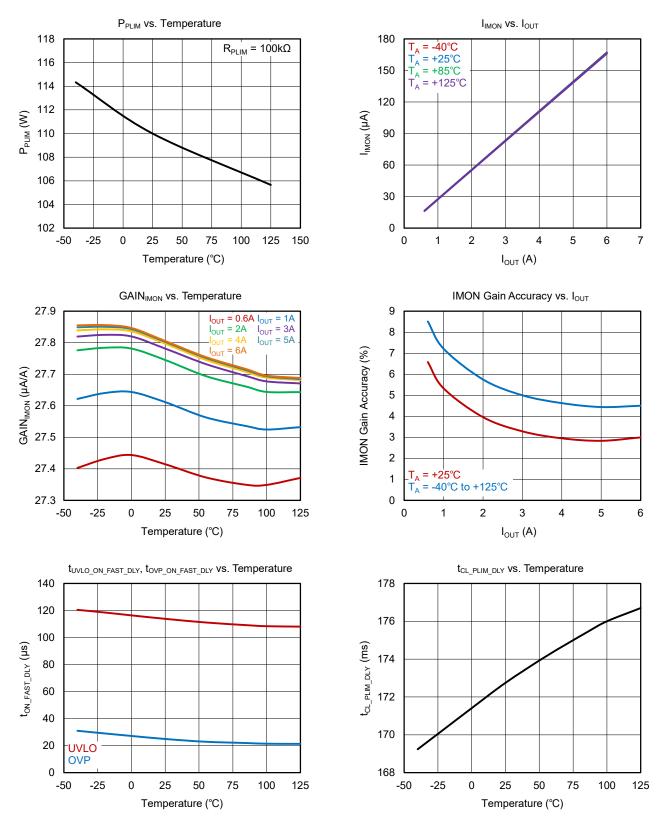

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{IN\_SYS} = V_{IN} = 24V$ ,  $V_{nSHDN} = 2V$ ,  $R_{ILIM} = 30k\Omega$ , IMON = PG = nFLT =  $C_{SS}$  = open, unless otherwise noted.

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

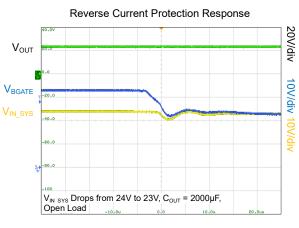

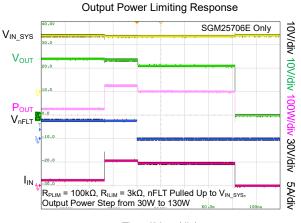

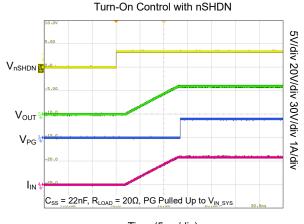

$T_A$  = +25°C, unless otherwise noted.

Thermal Regulation Loop Response

Over-Voltage Cut-Off Response at 33V Level

Time (5µs/div)

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A$  = +25°C, unless otherwise noted.

Response during Coming Out of Overload Fault

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

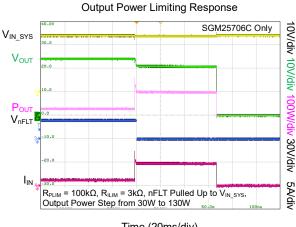

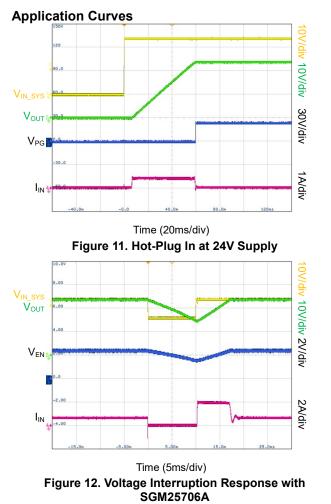

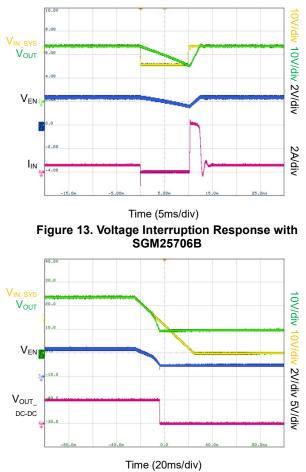

$T_A$  = +25°C,  $V_{IN_SYS}$  = 24V, unless otherwise noted.

Time (20ms/div)

Time (5ms/div)

## 60V, 6A Power Limiting, Surge Protection Industrial eFuse

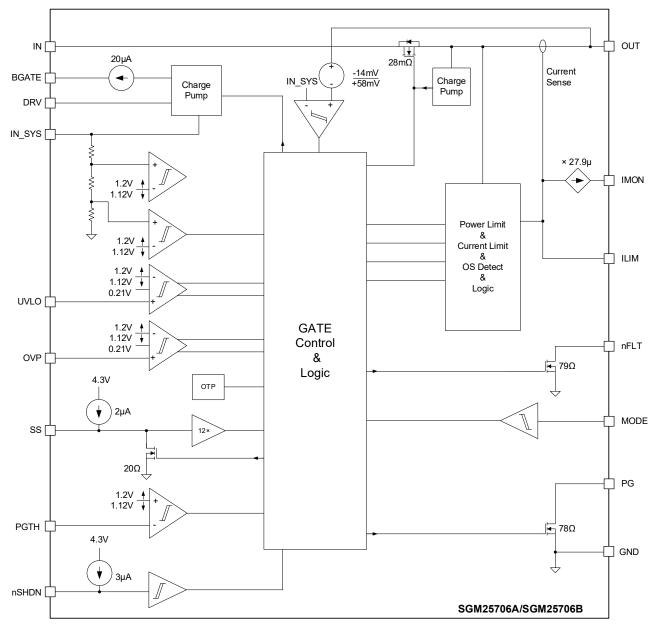

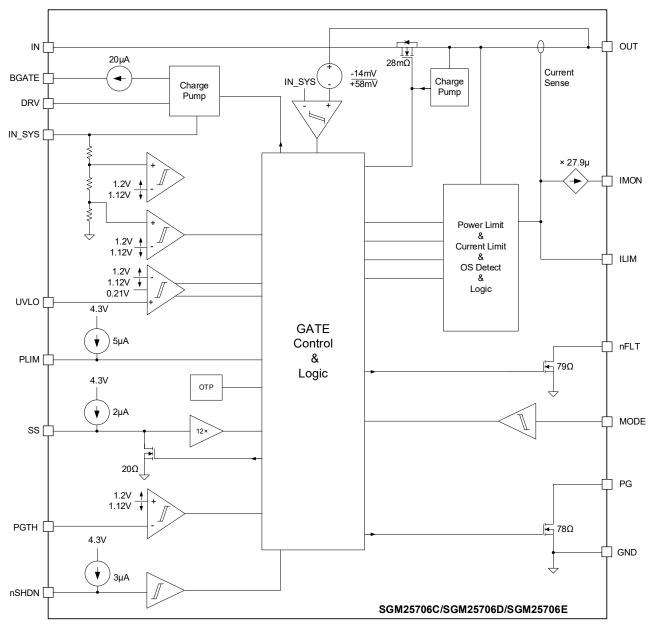

## FUNCTIONAL BLOCK DIAGRAM

Figure 5. SGM25706A and SGM25706B Block Diagram

## **FUNCTIONAL BLOCK DIAGRAM (continued)**

Figure 6. SGM25706C, SGM25706D and SGM25706E Block Diagram

## **DETAILED DESCRIPTION**

#### Overview

The SGM25706x series of 60V industrial eFuses provide comprehensive protection for various 4.5V to 60V power applications. The devices offer input reverse polarity protection up to -60V through an external N-MOSFET. For hot-plug applications, the devices provide inrush current management and output ramp rate control. Besides, the device offers many other protections such as under-voltage, over-voltage, over-current and reverse current protections. The accurate over-current limit (±8% at 6A) threshold reduces the system over-design. Under output short-circuit condition, the fast-trip short-circuit protection shuts down the device and cuts off the fault current within 0.3µs. The device cuts off the reverse current with a 0.183µs response time. The above features of SGM25706 simplify system designs for surge compliance and device protections.

The SGM25706 can distinguish between real system faults and transient event (such as real input under-voltage and transient input spike) and control the recovery behavior differently. This feature is realized through monitoring the output voltage at the PGTH pin. This ensures fast recovery of the device under tests such as input surge and input brown out tests.

The SGM25706C, SGM25706D and SGM25706E provide programmable output power limiting (PLIM) function which is for applications that demand limited output power.

The SGM25706 offers accurate monitoring of bus voltage and asserts the fault indicator pin (nFLT) under input under-voltage and over-voltage condition without additional voltage supervisor. The part continuously monitors the voltage of IN\_SYS (V<sub>IN\_SYS</sub>) and OUT (V<sub>OUT</sub>) to provide reverse current protection once V<sub>OUT</sub> - V<sub>IN\_SYS</sub> reaches the detection threshold.

Additional features of the SGM25706 devices include:

- Load current monitor at IMON pin with 4.5% at 6A accuracy.

- Selectable auto-retry or latch-off mode response under over-current limit, output power limit and over-temperature through the MODE pin.

- Power Good (PG) indicator through monitoring voltage at PGTH pin with ±2.8% detection threshold.

- Thermal shutdown response under over-temperature protection.

- Fault indicator (nFLT) with de-glitched report for faults such as input under-voltage and over-voltage.

- Enable and disable control using nSHDN pin for micro-controller.

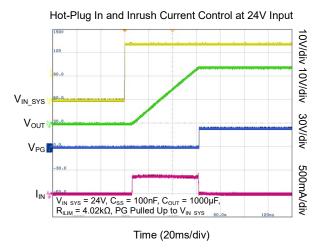

### Hot-Plug In and Inrush Current Control

The SGM25706 is designed to provide hot-plug in power management by controlling the inrush current as well as the output slew rate. This design helps eliminate the voltage drop and avoid undesired power reset. The output ramp rate at power-on is set by the capacitor from the SS pin to GND. If SS pin is left open, the device will start up with the fastest output slew rate  $(24V (10\% to 90\%)/418\mu s)$ . The inrush current can be calculated using Equation 1.

$$I = C \times \frac{dV}{dt} \ge I_{\text{INRUSH}} = C_{\text{OUT}} \times \frac{V_{\text{IN}}}{t_{\text{SS}}} \tag{1}$$

Where

$$t_{\rm ss} = 20.8 \times 10^3 \times V_{\rm IN} \times C_{\rm ss}$$

(2)

For detailed performance, refer to *Hot-Plug In and Inrush Current Control at 24V Input* in TYPICAL PERFORMANCE CHARACTERISTICS.

#### **Thermal Regulation Loop**

The average power dissipated on the device during start-up process driving a capacitive load can be calculated using Equation 3.

$$P_{D_{INRUSH}} = 0.5 \times V_{IN} \times I_{INRUSH}$$

(3)

## **DETAILED DESCRIPTION (continued)**

For system designs that require driving large output capacitors, the operating point could exceed the power dissipation versus time boundary limits shown in Thermal Shutdown Time vs. Power Dissipation in TYPICAL PERFORMANCE CHARACTERISTICS. Under this condition, the device junction temperature may exceed the over-temperature threshold and cause thermal shutdown. To avoid thermal shutdown, the thermal regulation loop regulates the device junction temperature at T<sub>J REG</sub>, +139 °C (TYP) through controlling the in-rush current and thereby limit the power dissipation of the device. Once the thermal regulation works, the internal 2.77s timer starts. The device will be turned off if the output does not fully power up within the time, and the following response (auto-retry or latch-off) depends on the MODE pin configuration shown in DEVICE OPERATIONAL DIFFERENT VARIATIONS WITH MODE CONFIGURATIONS. If the MODE pin is configured to auto-retry, the device will restart after a delay of 1.33s.

The thermal regulation loop is enabled during input power-on, UVLO cycling and nSHDN power-on. The thermal regulation loop is disabled internally when the internal MOSFET's gate is fully enhanced after start-up.

For detailed performance, refer to *Thermal Regulation Loop Response* in TYPICAL PERFORMANCE CHARACTERISTICS.

#### **PG and PGTH**

The device provides a Power Good (PG) indicator with open-drain output. It can be used to supervise the downstream load. The threshold of PG is set by connecting a resistor network from OUT to PGTH and to GND. The PG asserts (goes high) when the internal MOSFET of the device is fully turned on and the voltage at PGTH (V<sub>PGTH</sub>) exceeds the V<sub>PGTHR</sub>. This pin de-asserts when V<sub>PGTH</sub> drops below V<sub>PGTHF</sub>. The PG has a 1.35ms (TYP) de-glitch time at the rising edge and a 1.58 $\mu$ s (TYP) de-glitch time at the falling edge. The rating of PG pin is 60V and it can be connected to IN\_SYS or OUT through a resistor.

#### **PGTH as OUT Sensing Input**

For typical configuration, the PG threshold is set by connecting a resistor network from OUT to PGTH and to GND. During a system transient fault recovery event (such as recovery from input transient under-voltage or over-voltage), the device chooses different recovery behavior based on the  $V_{PGTH}$  information (output recovery with internal fast slew rate or with SS slew rate).

Figure 3 shows the turn-on behavior based on  $V_{PGTH}$ information. During the recovery process, if  $V_{PGTH}$  is greater than  $V_{PGTHF}$ , the internal MOSFET is turned on with the fastest slew rate (ignoring the capacitor at SS pin) after a delay of t<sub>OVP ON FAST DLY</sub>. Meanwhile, the thermal regulation loop is enabled for 2.77s. The maximum current through the device is limited to  $I_{OL}$  for SGM25706A and SGM25706C and to 2  $\times$   $I_{\text{OL}}$  for SGM25706B, SGM25706D and SGM25706E for a duration of  $t_{\text{CB\_DLY}}\text{)}.$  If  $V_{\text{PGTH}}$  is lower than  $V_{\text{PGTHF}},$  the internal MOSFET is turned on with the slew rate controlled by the SS capacitor. The maximum current through the device is limited to  $I_{OL}$ . With this design, the device is able to distinguish between real faults and transient faults and choose different recovery behavior accordingly. This design makes the device recover fast under transient test such as input surge or brown out tests. Besides, this design can be disabled by pulling PGTH to GND, and PG will be constant low level under this case.

#### Under-Voltage Lockout (UVLO)

The SGM25706 provides programmable under-voltage lockout (UVLO) protection with  $\pm 2.8\%$  threshold accuracy. When the voltage of UVLO (V<sub>UVLO</sub>) drops below the falling threshold V<sub>UVLOF</sub>, the internal MOSFET is turned-off and nFLT pin is asserted. The UVLO hysteresis is 78mV (TYP). The UVLO threshold can be set through connecting a resistor network from IN\_SYS to UVLO pin and to GND. The device has a 15.38V (rising) default UVLO threshold with 0.93V hysteresis which is selected by pulling UVLO pin to GND. If the UVLO protection is not used, the UVLO pin must be connected to IN\_SYS and must not be floating. For applications that input reverse polarity protection is needed, place at least a 300k $\Omega$  resistor between UVLO and IN SYS.

Figure 2 shows the turn-on behavior when  $V_{\text{UVLO}}$  exceeds  $V_{\text{UVLOR}}$  threshold.

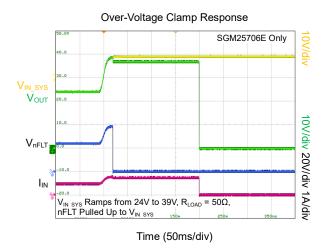

### **Over-Voltage Protection (OVP)**

The SGM25706 series of device provide robust input over-voltage protection. The SGM25706A and SGM25706B offer programmable over-voltage lockout (OVLO) protection with  $\pm 2.8\%$  threshold accuracy. When the voltage on OVP pin exceeds the rising threshold V<sub>OVPR</sub>, the internal MOSFET is turned off. The OVP threshold can be set by connecting a resistor network from IN\_SYS to OVP pin and to GND.

The SGM25706A and SGM25706B also provide a default 34.16V OVLO threshold  $V_{IN\_SYS\_OVP}$  with 490mV hysteresis which can be enabled by pulling OVP pin to GND.

The SGM25706C and SGM25706D offer a fixed 34.7V (MAX) over-voltage clamp (OVC) protection, while the SGM25706E offers 38.4V (MAX) over-voltage clamp (OVC) protection. During the OVC protection, excess power is dissipated on the device which could increase the device temperature. To suppress the temperature rise, the device has a 170ms maximum duration for OVC operation. After this duration, the internal MOSFET is turned off and the following behavior (auto-retry or latch off) depends on the MODE pin configuration.

Figure 2 illustrates the OVP behavior. For OVLO functionality, the nFLT is asserted with a  $2\mu$ s (TYP) delay after voltage on OVLO pin exceeds V<sub>OVPR</sub>. For OVC functionality, the nFLT is asserted with a 691 $\mu$ s (TYP) delay after the device enters OVC operation. For both conditions, the nFLT would remain asserted until the over-voltage fault is removed.

For detailed performance, refer to *Over-Voltage Cut-Off Response at 33V Level* and *Over-Voltage Clamp Response* in TYPICAL PERFORMANCE CHARACTERISTICS.

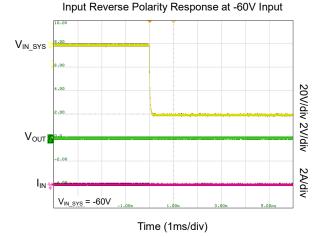

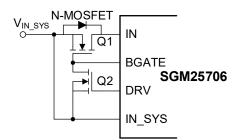

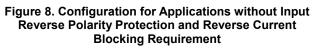

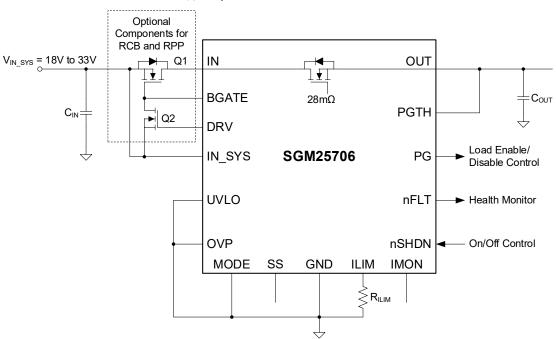

# Input Reverse Polarity Protection (BGATE, DRV)

The SGM25706 provides input reverse polarity protection. Connect an external N-MOSFET (Q1) with the Source terminal to IN\_SYS pin, Drain terminal to IN pin, and Gate terminal to BGATE pin as shown in Figure 7. This connection makes the external MOSFET

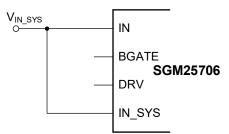

back to back connection with the internal MOSFET of the device and protects the device against input reverse polarity fault. Besides, an external small signal MOSFET (Q2) is needed to quickly pull down the external MOSFET (Q1). Connect its Source terminal to IN\_SYS pin, Drain terminal to BGATE pin (Gate terminal of Q1) and Gate terminal to DRV pin. If the input reverse polarity protection is not needed, both Q1 and Q2 are not needed and IN is directly connected to IN\_SYS with BGATE and DRV pin floating as shown in Figure 8.

The SGM25706 supports a maximum voltage difference between IN\_SYS and OUT, namely  $V_{IN\_SYS}$  -  $V_{OUT}$ , up to -85V. The voltage stress is withstood by the external MOSFET Q1. The device offers a 10.08V gate driving voltage at BGATE pin. The signal MOSFET Q2 pulls down the gate of Q1 under reverse polarity and reverse current faults. Under proper design, Q2 should have a minimum  $V_{DS}$  rating of 15V and a maximum  $V_{GS}$  rating of 20V. The input capacitance  $C_{ISS}$  should be less than 50pF with the turn-on threshold voltage  $V_{TH}$  less than 1.5V.

Figure 7. Configuration for Input Reverse Polarity Protection and Reverse Current Blocking

#### **Reverse Current Protection**

The SGM25706 provides reverse current protection through monitoring the V<sub>IN\_SYS</sub> and V<sub>OUT</sub>. When V<sub>IN\_SYS</sub> - V<sub>OUT</sub> drops below -14mV, the reverse protection works and quickly turns off the external MOSFET Q1. The total response time to turn off Q1 is  $t_{RCB\_FAST\_DLY}$  +  $t_{DRIVER}$  where  $t_{DRIVER}$  is the time taken to turn off Q1 which can be calculated using Equation 4.

$$t_{\text{DRIVER}} = -R_{\text{DSON}_{Q2}} \times C_{\text{ISS}_{Q1}} \times \ln(\frac{V_{\text{TH}_{Q1}}}{V_{\text{BGATE}}})$$

(4)

Where

- R<sub>DSON\_Q2</sub> is the on-resistance of pull-down MOSFET Q2.

- C<sub>ISS\_Q1</sub> is the input capacitance of the blocking MOSFET Q1.

- V<sub>TH\_Q1</sub> is the turn-on threshold voltage of Q1.

- V<sub>BGATE</sub> = 10.08V (TYP).

For typical design,  $t_{DRIVER}$  is generally 10% to 20% of  $t_{RCB \ FAST \ DLY}$  of 0.183µs (TYP).

#### **Overload and Short-Circuit Protection**

The device monitors the load current continuously to provide over-load protection.

#### **Overload Protection**

Set the current limit using Equation 5.

$$I_{OL} = \frac{18}{R_{ILIM}}$$

(5)

Where

- I<sub>OL</sub> is the overload current limit in A.

- $R_{ILIM}$  is the current limit resistor in k $\Omega$ .

# Active Current Limit at 1 × $I_{OL}$ , (SGM25706A and SGM25706C Only)

For SGM25706A and SGM25706C, the load current is limited to 1 ×  $I_{OL}$  under over-load condition. The output voltage under regulation decreases which will increase the device power dissipation and cause device temperature rise. To suppress this, the device has a  $t_{CL_PLIM_DLY}$  (171ms TYP) maximum duration for over-current limit operation. Within this time duration, if the device temperature exceeds the over-temperature

threshold, the internal MOSFET is turned off due to thermal shutdown, and the following behavior (auto-retry or latch-off) depends on the MODE pin configuration. If the device continuously operates at over-current manner for this 171ms time, then the internal MOSFET will be turned off after this duration. Likely, the following behavior (auto-retry or latch-off) depends on the MODE pin configuration.

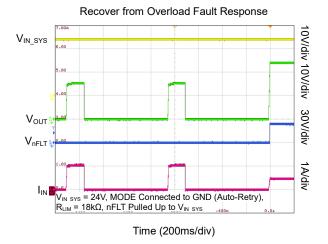

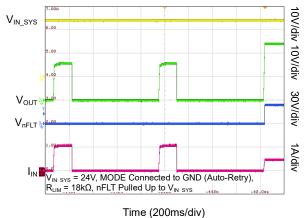

#### Active Current Limit with 2 × I<sub>OL</sub> Pulse Current Support, (SGM25706B, SGM25706D and SGM25706E Only)

For SGM25706B, SGM25706D and SGM25706E, after the power-up with  $V_{PGTH}$  above  $V_{PGTHR}$ , if the load current exceeds  $I_{OI}$ , an internal  $t_{CB,DIY}$  (26.3ms TYP) timer starts. During this time, the load current allowed to pass through the device will be limited to not more than 2 ×  $I_{OL}$  (load current more than 2 ×  $I_{OL}$  will be regulated to 2 ×  $I_{OL}$ ). After t<sub>CB DLY</sub> time, the load current is regulated to I<sub>OL</sub>. The maximum time duration for the 1 ×  $I_{OL}$  over-current limit operation is  $t_{CL PLIM DLY}$ . The following behavior (auto-retry or latch-off) depends on the MODE pin configuration. During the current limit operation, if the device temperature exceeds the over-temperature threshold, the internal MOSFET is turned off due to thermal shutdown, and the following behavior (auto-retry or latch-off) depends on the MODE pin configuration.

The 2 × I<sub>OL</sub> current limit feature is only activated after V<sub>PGTH</sub> exceeds V<sub>PGTHR</sub>. If V<sub>PGTH</sub> is below V<sub>PGTHF</sub> during conditions such as power-up or auto-retry, the 2 × I<sub>OL</sub> current limit function will not be activated and the device will limit current at I<sub>OL</sub>.

The SGM25706 provides ILIM pin open and short state detection. The internal MOSFET is turned off when ILIM pin is detected in short or open state, and remains turn-off until the fault is removed.

Refer to Overload Performance, Load Step from  $50\Omega$  to  $15\Omega$  and Response during Coming Out of Overload Fault in TYPICAL PERFORMANCE CHARACTERISTICS for detailed performance.

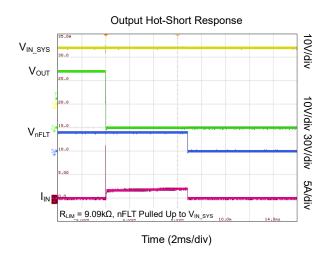

### **Short-Circuit Protection**

When the output short-circuit occurs, the current from IN to OUT rises very rapidly. Due to limited bandwidth, the current limit amplifier is unable to respond quickly to this fault. To solve this, the SGM25706 integrates with a fast-trip comparator which can shut down the internal MOSFETs within 0.3µs (TYP) with  $I_{SCP} = 37A$ . The fast-trip comparator works and cuts off the short-circuit current when the current through the device  $I_{OUT}$  exceeds the fast-trip threshold  $I_{FASTRIP}$ . The internal MOSFETs would remain OFF state for only a few ms, following by soft-restart in a current limit manner where current through the device is regulated to  $I_{OL}$  under the regulation of current limit amplifier. Then, the device behaves the same as the overload condition.

For robust performance, the fast-trip comparator is designed with a line voltage noise immunity. This is achieved by changing the turn-off time of the internal MOSFET with the over-current level. The turn-off time is faster under higher over-current level. The response time of fast-trip comparator is  $2\mu s$  (TYP) when  $I_{FASTTRIP} < I_{OUT} < I_{SCP}$ .

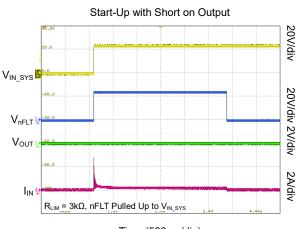

#### Start-Up with Short-Circuit On Output

For power-up with output short-circuit to GND, the current through the device is limited to  $I_{OL}$ . Due to high power dissipation of the device ( $V_{IN} \times I_{OL}$ ), the junction temperature of the device increases rapidly. When the temperature reaches the thermal regulation point, the thermal regulation loop works and limits the load current to maintain the device temperature at TJ\_REG, +130 °C (TYP) for a duration of  $t_{TREG_TIMEOUT}$ , 2.77s (TYP). The following behavior (auto-retry or latch-off) depends on the MODE pin configuration. The nFLT is asserted after  $t_{TREG_TIMEOUT}$  and remains asserted until the output short-circuit fault is removed. *Start-Up with Short on Output* in TYPICAL PERFORMANCE CHARACTERISTICS shows the device performance under power-on with output short-circuit.

# Output Power Limiting, PLIM (SGM25706C, SGM25706D and SGM25706E Only)

For SGM25706A and SGM25706B, the output power is limited to  $V_{OUT} \times I_{OL}$  which increases linearly with the input supply voltage. For applications that require limiting the output power under wide input voltage range, this design is difficult to achieve. To solve this, the SGM25706C, SGM25706D and SGM25706E provide programmable output power limiting functionality. The output power limit level is set by placing a resistor from PLIM pin to GND. If the output power limiting is not used, tie the PLIM pin to GND directly.

For SGM25706C, the device limits the output power at the level set by the PLIM resistor under output over-power condition. The output power limit functionality indirectly results in the device operation in current limit mode with  $P_{LIM} = V_{OUT} \times I_{OUT}$ .  $I_{PLIM}$ ,  $P_{PLIM}$  vs.  $V_{IN_SYS}$  in TYPICAL PERFORMANCE CHARACTERISTICS shows the device behavior under 110W power limit level. The device has a 171ms  $t_{CL_PLIM_DLY}$  maximum time duration for output power limiting operation. After this time, the device behavior (auto-retry or latch-off) depends on the MODE pin configuration.

For SGM25706D and SGM25706E, the output power is limited to  $V_{OUT} \times 2 \times I_{OL}$  for a maximum duration of  $t_{CB_DLY}$ , 26.3ms (TYP). After this duration, the output power is limited to PLIM set by the PLIM resistor. The power limit is set using Equation 6.

$$P_{\rm PLIM} = R_{\rm PLIM}^{1.04} - 9$$

(6)

Where  $P_{PLIM}$  is output power limit in W,  $R_{PLIM}$  is the power limit setting resistor in k $\Omega$ .

For detailed performance, refer to *Output Power Limiting Response* in TYPICAL PERFORMANCE CHARACTERISTICS.

## **DETAILED DESCRIPTION (continued)**

Figure 9. SGM25706C/D/E Typical Application Schematic

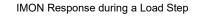

#### **Current Monitoring Output (IMON)**

The SGM25706 has a current monitoring function at the IMON pin. The sourcing current of this pin is proportional to the current of internal MOSFETs. By placing a resistor  $R_{IMON}$  from this pin to GND, this monitored current is converted to IMON voltage.

The maximum voltage on the IMON pin is internally limited to 4V. With this limitation, the maximum value of  $R_{IMON}$  can be determined using Equation 7.

$$V_{\rm IMON} = \left[ I_{\rm OUT} \times GAIN_{\rm IMON} \right] \times R_{\rm IMON}$$

(7)

Where

- GAIN<sub>IMON</sub> is the gain factor I<sub>IMON</sub> : I<sub>OUT</sub> = 27.9µA/A (TYP).

- I<sub>OUT</sub> is the load current.

Please do not place bypass capacitor at IMON pin which could cause delay in current monitoring.

For detailed performance, refer to *IMON Response during a Load Step* in TYPICAL PERFORMANCE CHARACTERISTICS.

#### FAULT Response (nFLT)

The SGM25706 has an open-drain fault indicator nFLT pin which asserts under input under-voltage, input

over-voltage, current limiting, output power limiting, reverse current, ILIM pin open or short and thermal shutdown. To avoid false reporting, this pin is designed with an internal de-glitch without additional external circuits. The nFLT pin can be left open or tied to GND if not used.

#### IN\_SYS, IN, OUT and GND Pins

Place a minimum of  $0.1\mu F$  bypass capacitor from IN\_SYS pin to GND.

For system that requires reverse current protection or input reverse polarity protection:

Connect an external N-MOSFET with Source terminal connected to IN\_SYS, Drain terminal to IN, and Gate terminal to BGATE.

Connect an external signal MOSFET with Source terminal to IN\_SYS, Drain terminal to BGATE and Gate terminal to DRV.

If the reverse current protection and reverse polarity protection are not used, connect IN\_SYS to IN directly, and the BGATE and DRV pin can be left open.

#### **Thermal Shutdown**

The SGM25706 incorporates over-temperature protection with thermal shutdown function. The internal MOSFETs will be turned off when the junction temperature  $T_J$  exceeds  $T_{SD}$  (+167°C TYP). After that, the device will remain latched-off or auto-retry with a delay of 682ms (TYP),  $t_{TSD\_RETRY}$  after  $T_J < (T_{SD} - 16°C)$  depending on the MODE pin configuration. During thermal shutdown, the nFLT pin is asserted.

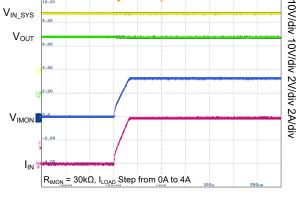

### Low Current Shutdown Control (nSHDN)

The device can be shut down through pulling the nSHDN pin below the 0.8V (TYP) threshold with a micro-controller. In shutdown mode, the quiescent current of the device is reduced to  $19\mu A$  (TYP). The controller or any other device should have at least  $8\mu A$  sinking current capability to pull down the nSHDN pin. To enable the device, nSHDN should be pulled up to at least 1.8V where the device starts up with soft-start mode.

# **APPLICATION INFORMATION**

## **Typical Application**

Figure 10. Typical Application Schematics: 24V, 2A eFuse Input Protection Circuit

#### **Design Requirements**

Table 1 shows the Design Requirements for SGM25706.

#### Table 1. Design Requirements

|                     | DESIGN PARAMETER                | EXAMPLE VALUE                                     |

|---------------------|---------------------------------|---------------------------------------------------|

| V <sub>IN</sub>     | Typical Input Voltage           | 24V                                               |

| V <sub>UV</sub>     | Under-Voltage Lockout Set Point | 18V                                               |

| Vov                 | Over-Voltage Cutoff Set Point   | 33V                                               |

| $V_{\text{PG}}$     | Output Power Good Threshold     | 22V                                               |

| I <sub>LIM</sub>    | Overload Current Limit          | 2A                                                |

| I <sub>INRUSH</sub> | Inrush Current Limit            | 500mA                                             |

| Pout                | Output Load                     | 15W (DC-DC) with<br>15V V <sub>IN_MIN_DC-DC</sub> |

| $t_{FAIL\_TR}$      | Power Interruption Time         | 10ms                                              |

#### Detailed Design Procedure Programming the Current-Limit Threshold: R<sub>ILIM</sub> Selection

The current limit level is set by the ILIM pin resistor  $R_{ILIM}$  which can be calculated using Equation 8.

$$R_{ILIM} = \frac{18}{I_{OL}} = 9k\Omega$$

(8)

Where