# 74AHCT595F 8-Bit Serial-In/Serial-Out or Parallel-Out Shift Register with Output Latches

## GENERAL DESCRIPTION

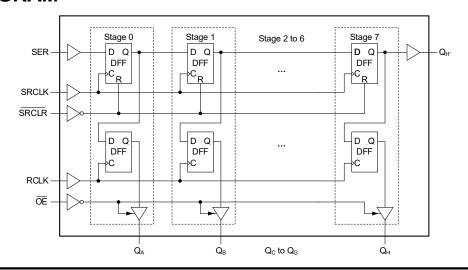

The 74AHCT595F is an 8-bit serial-in/serial-out or parallel-out shift register with output latches designed for 4.5V to 5.5V V<sub>CC</sub> operation.

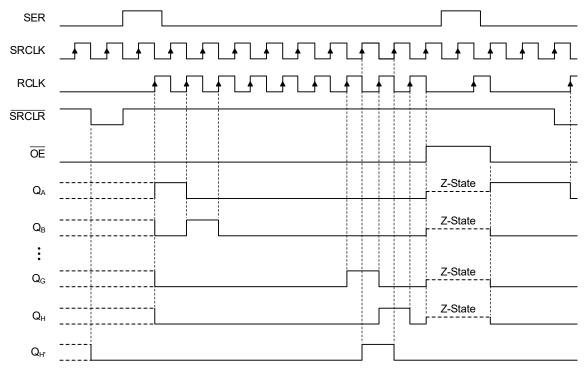

The device integrates an 8-bit shift register and an 8-bit D-type storage register. The storage register features parallel 3-state outputs. The shift register provides a clear input ( $\overline{SRCLR}$ ) with direct overriding function, a serial input ( $\overline{SERCLR}$ ) and a serial output ( $\overline{OE}$ ) to implement cascading. When output enable input ( $\overline{OE}$ ) is held low, the data in storage register will appear at the outputs. When  $\overline{OE}$  is held high, all parallel outputs are in high-impedance state.

Both the shift register and storage register have separate clocks. The shift register clock (SRCLK) and storage register clock (RCLK) are positive-edge triggered.

This device is highly suitable for partial power-down applications by using power-off leakage current ( $I_{OFF}$ ) circuit. When the device is powered down, the output is disabled, and the current backflow can be prevented from passing through the device.

The 74AHCT595F is available in Green TSSOP-16 and SOIC-16 packages. It operates over an operating temperature range of -40°C to +125°C.

## **FEATURES**

- Supply Voltage Range: 4.5V to 5.5V

- Direct Clear Input of Shift Register

- Inputs are Compatible with TTL-Voltage

- Outputs in High-Impedance State when V<sub>cc</sub> = 0V

- Latch-Up Performance (> 100mA) Meets JESD 78,

Class II Standard

- -40°C to +125°C Operating Temperature Range

- Available in Green TSSOP-16 and SOIC-16 Packages

## **APPLICATIONS**

Computing: Server, PC, Notebook, Network Switch Telecom Equipment Medical Equipment Industrial Equipment

## **LOGIC DIAGRAM**

## PACKAGE/ORDERING INFORMATION

| MODEL      | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER  | PACKAGE<br>MARKING    | PACKING<br>OPTION   |

|------------|------------------------|-----------------------------------|---------------------|-----------------------|---------------------|

| 74AHCT595F | TSSOP-16               | -40°C to +125°C                   | 74AHCT595FXTS16G/TR | 1QB<br>XTS16<br>XXXXX | Tape and Reel, 4000 |

| 74AHC1393F | SOIC-16                | -40°C to +125°C                   | 74AHCT595FXS16G/TR  | 1QAXS16<br>XXXXX      | Tape and Reel, 2500 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### ABSOLUTE MAXIMUM RATINGS

| , 12002012 III, 0 (IIII O III 1 II I I I I I I I I I I I I            |

|-----------------------------------------------------------------------|

| Supply Voltage Range, V <sub>CC</sub> 0.5V to 7.0V                    |

| Input Voltage Range, V <sub>I</sub> <sup>(1)</sup> 0.5V to 7.0V       |

| Output Voltage Range, $V_0^{(1)}$ -0.5V to MIN(7.0V, $V_{CC}$ + 0.5V) |

| Input Clamp Current, I <sub>IK</sub> (V <sub>I</sub> < 0V)20mA        |

| Output Clamp Current, I <sub>OK</sub> (V <sub>O</sub> < 0V)20mA       |

| Continuous Output Current, $I_O$ ( $V_O = 0V$ to $V_{CC}$ )±25mA      |

| Continuous Current through V <sub>CC</sub> or GND±50mA                |

| Junction Temperature <sup>(2)</sup> +150°C                            |

| Storage Temperature Range65°C to +150°C                               |

| Lead Temperature (Soldering, 10s)+260°C                               |

| ESD Susceptibility (3) (4)                                            |

| HBM±2000V                                                             |

| CDM±1000V                                                             |

## NOTES:

- 1. The input and output voltage ratings may be exceeded if the input and output clamp current ratings are observed.

- 2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability.

- 3. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 4. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

- 5. Unused input pins must be held at  $V_{\text{CC}}$  or GND to guarantee the device in normal operation.

## RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range, V <sub>CC</sub>              | 4.5V to 5.5V          |

|----------------------------------------------------|-----------------------|

| Input Voltage Range, V <sub>I</sub> <sup>(5)</sup> | 0V to 5.5V            |

| Output Voltage Range, Vo                           | 0V to V <sub>CC</sub> |

| Input Transition Rise or Fall Rate, Δt/ΔV          |                       |

| V <sub>CC</sub> = 4.5V to 5.5V                     | 20ns/V (MAX)          |

| Operating Temperature Range                        | 40°C to +125°C        |

## **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

## **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

## **FUNCTION TABLE**

|     |       | INPUTS |      |    | FUNCTION                                                                                                                   |  |

|-----|-------|--------|------|----|----------------------------------------------------------------------------------------------------------------------------|--|

| SER | SRCLK | SRCLR  | RCLK | ŌĒ | FUNCTION                                                                                                                   |  |

| X   | X     | X      | X    | Н  | Outputs (Q <sub>A</sub> ~ Q <sub>H</sub> ) are disabled.                                                                   |  |

| X   | X     | X      | X    | L  | Outputs (Q <sub>A</sub> ~ Q <sub>H</sub> ) are enabled.                                                                    |  |

| X   | X     | L      | X    | X  | Data of the shift register is cleared.                                                                                     |  |

| L   | 1     | Н      | X    | X  | Logic low-level shifted into shift register stage 0. Other stages can transfer data from the previous stage respectively.  |  |

| Н   | 1     | Н      | X    | Х  | Logic high-level shifted into shift register stage 0. Other stages can transfer data from the previous stage respectively. |  |

| Х   | Х     | X      | 1    | Х  | Data of the shift register is transferred to the storage register.                                                         |  |

H = High Voltage Level

L = Low Voltage Level

↑ = Low-to-High Clock Transition

X = Don't Care

# **TIMING DIAGRAM**

Figure 1. Timing Diagram

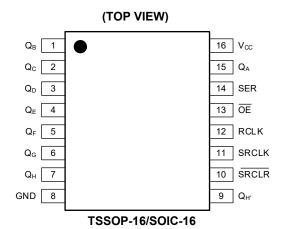

# **PIN CONFIGURATIONS**

# **PIN DESCRIPTION**

| PIN                     | NAME                                                                                                                                  | FUNCTION                                              |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| 15, 1, 2, 3, 4, 5, 6, 7 | Q <sub>A</sub> , Q <sub>B</sub> , Q <sub>C</sub> , Q <sub>D</sub> , Q <sub>E</sub> , Q <sub>F</sub> , Q <sub>G</sub> , Q <sub>H</sub> | Parallel Data Outputs.                                |  |  |  |

| 8                       | GND Ground.                                                                                                                           |                                                       |  |  |  |

| 9                       | Q <sub>H</sub> '                                                                                                                      | Serial Data Output.                                   |  |  |  |

| 10                      | SRCLR                                                                                                                                 | Shift Register Clear Input (Active-Low).              |  |  |  |

| 11                      | SRCLK                                                                                                                                 | Shift Register Clock Input (Rising Edge Triggered).   |  |  |  |

| 12                      | RCLK                                                                                                                                  | Storage Register Clock Input (Rising Edge Triggered). |  |  |  |

| 13                      | ŌĒ                                                                                                                                    | Output Enable Input (Active-Low).                     |  |  |  |

| 14                      | SER                                                                                                                                   | Serial Data Input.                                    |  |  |  |

| 16                      | V <sub>CC</sub>                                                                                                                       | Power Supply.                                         |  |  |  |

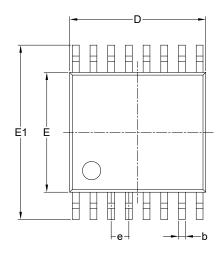

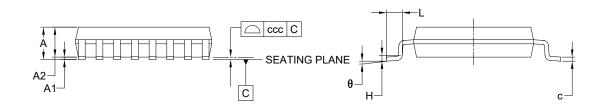

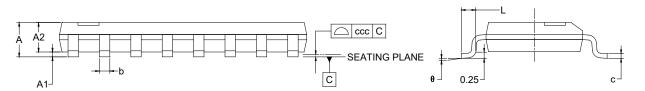

# **PACKAGE OUTLINE DIMENSIONS** TSSOP-16

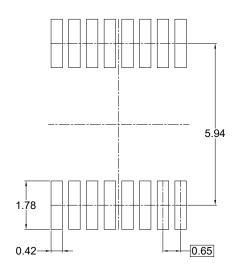

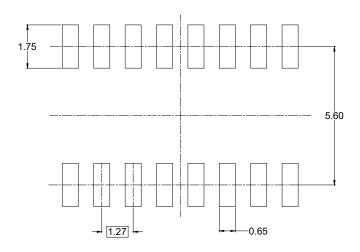

RECOMMENDED LAND PATTERN (Unit: mm)

| Cymphal | Dimensions In Millimeters |           |                |  |  |  |  |

|---------|---------------------------|-----------|----------------|--|--|--|--|

| Symbol  | MIN                       | NOM       | MAX            |  |  |  |  |

| Α       | -                         | -         | 1.200          |  |  |  |  |

| A1      | 0.050                     | -         | 0.150          |  |  |  |  |

| A2      | 0.800                     | -         | 1.050          |  |  |  |  |

| b       | 0.190                     | -         | 0.300          |  |  |  |  |

| С       | 0.090                     | -         | 0.200<br>5.100 |  |  |  |  |

| D       | 4.860                     | -         |                |  |  |  |  |

| Е       | 4.300                     | -         | 4.500          |  |  |  |  |

| E1      | 6.200                     | -         | 6.600          |  |  |  |  |

| е       |                           | 0.650 BSC |                |  |  |  |  |

| L       | 0.450 -                   |           | 0.750          |  |  |  |  |

| Н       | 0.250 TYP                 |           |                |  |  |  |  |

| θ       | 0°                        | -         | 8°             |  |  |  |  |

| ccc     | 0.100                     |           |                |  |  |  |  |

- This drawing is subject to change without notice.

The dimensions do not include mold flashes, protrusions or gate burrs.

- 3. Reference JEDEC MO-153.

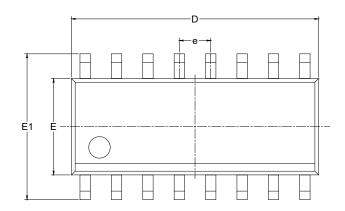

# **PACKAGE OUTLINE DIMENSIONS** SOIC-16

## RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions<br>In Millimeters |         |        |  |  |  |  |

|--------|------------------------------|---------|--------|--|--|--|--|

|        | MIN                          | NOM     | MAX    |  |  |  |  |

| Α      | -                            | -       | 1.750  |  |  |  |  |

| A1     | 0.100                        | -       | 0.250  |  |  |  |  |

| A2     | 1.250                        | -       | 1.550  |  |  |  |  |

| b      | 0.310                        | -       | 0.510  |  |  |  |  |

| С      | 0.100                        | 0.100 - |        |  |  |  |  |

| D      | 9.800                        | -       | 10.200 |  |  |  |  |

| E      | 3.800                        | -       | 4.000  |  |  |  |  |

| E1     | 5.800 -                      |         | 6.200  |  |  |  |  |

| е      | 1.270 BSC                    |         |        |  |  |  |  |

| L      | 0.400 - 1.27                 |         |        |  |  |  |  |

| θ      | 0°                           | -       | 8°     |  |  |  |  |

| ccc    | 0.100                        |         |        |  |  |  |  |

- NOTES:

1. This drawing is subject to change without notice.

2. The dimensions do not include mold flashes, protrusions or gate burrs.

- 3. Reference JEDEC MS-012.

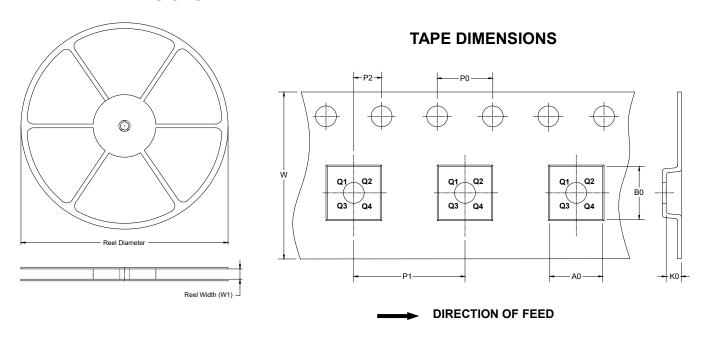

# TAPE AND REEL INFORMATION

## **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TSSOP-16     | 13"              | 12.4                     | 6.80       | 5.40       | 1.50       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| SOIC-16      | 13"              | 16.4                     | 6.50       | 10.30      | 2.10       | 4.0        | 8.0        | 2.0        | 16.0      | Q1               |

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

# **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-----------|----------------|---------------|----------------|--------------|

| 13"       | 386            | 280           | 370            | 5            |